소개

수천 년 동안 인류는 기술 발전을 위해 오래되고 검증된 공식을 개발했습니다. 발명가와 설계자는 비용 효율성과 성능 향상에 집중하기 전에 먼저 신기술의 일반적인 메커니즘을 파악하는 데 집중합니다.

이 기본 경험 법칙은 다른 분야나 산업과 마찬가지로 솔리드 스테이트 스토리지 분야에도 적용됩니다. 이 기사에서는 솔리드 스테이트 드라이브 기술의 성능을 높이는 데 도움이 될 수 있는 중요한 최근 개발인 HMB(호스트 메모리 버퍼)에 대해 살펴보겠습니다.

SSD 메모리 설계의 장단점

솔리드 스테이트 드라이브(SSD)의 설계에서 추가 플래시 메모리는 성능을 높이면서 전체 드라이브 용량을 늘릴 수 있습니다. 그러나 다른 제품 설계와 마찬가지로 엔지니어는 자원과 비용 사이에서 균형을 이루어야 합니다.

SSD 설계의 경우 기존 기능 이상으로 각 장치의 성능을 향상시키는 두 가지 방법이 있습니다. 플래시 메모리의 밀도를 높이거나 추가 물리적 공간을 희생하여 추가 플래시 메모리를 장착하는 것입니다. 그러나 인쇄 회로 기판(PCB) 공간은 드라이브 폼 팩터의 선택에 관계없이 제한되어 있기 때문에 일반적으로 보드의 다른 구성 요소를 생략하는 비용이 발생합니다.

이제 많은 공급업체가 비용 절감을 달성하기 위해 드라이브 설계에서 빠르지만 값비싼 DRAM(동적 랜덤 액세스 메모리)을 제거하기로 선택합니다. 그러나 DRAM은 고속 휘발성 메모리로서 자체 용도가 있으며 쉽게 교체할 수 없습니다. DRAM이 없는 설계는 또한 데이터 전송 중, 특히 대용량 임의 읽기 환경에서 성능 및 신호 무결성 조정 측면에서 직면해야 하는 고유한 문제가 있습니다.

호스트 메모리 버퍼란 무엇입니까?

그렇다면 설계자는 DRAM이 없는 SSD의 약점을 어떻게 해결할 수 있습니까? 간결한 대답은 호스트 메모리 버퍼(HMB) 기술입니다. HMB는 SSD가 호스트 CPU의 메모리 자원을 활용해 능동적으로 고성능을 추구할 수 있게 해주는 기술이다.

NVMe(NVM Express 또는 Non-Volatile Memory Express)는 NAND 플래시 메모리 및 SSD와 같은 컴퓨터의 비휘발성 메모리에 액세스하는 방법을 정의하는 개방형 표준입니다. NVMe 1.2 사양은 호스트 메모리 버퍼 기능을 처음으로 도입했습니다.

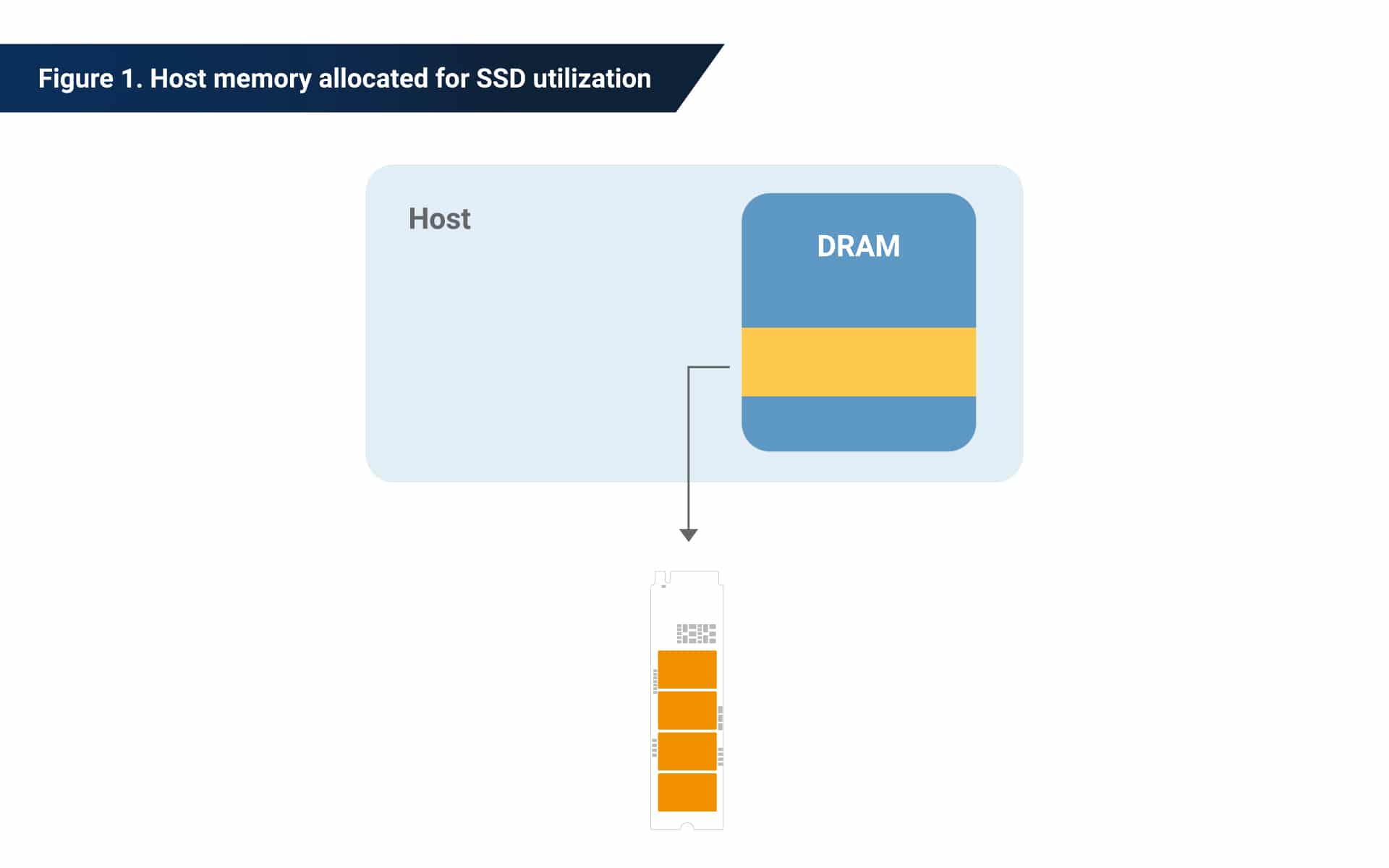

특히 NVMe 1.2는 HMB가 SSD 사용을 위해 호스트 메모리를 할당하는 방법을 설명했습니다. 적절한 구성을 가진 모든 SSD는 호스트와 통신하여 필요한 최소 버퍼 크기를 지정할 수 있습니다. NVMe 1.2 사양에는 드라이브가 실수로 제거된 경우 데이터가 손실되거나 손상되지 않도록 하는 등 다양한 목적을 위한 조건 및 제한 사항도 포함되어 있습니다.

HMB 기능을 사용하려면 드라이브와 운영 체제가 모두 지원해야 합니다. 다행히 Microsoft는 2017년에 출시된 Windows 10 Creators Update(예: 버전 1703)부터 HMB 지원을 허용했습니다.

왜 HMB인가? DRAM 있음에서 DRAM SSD 없음으로

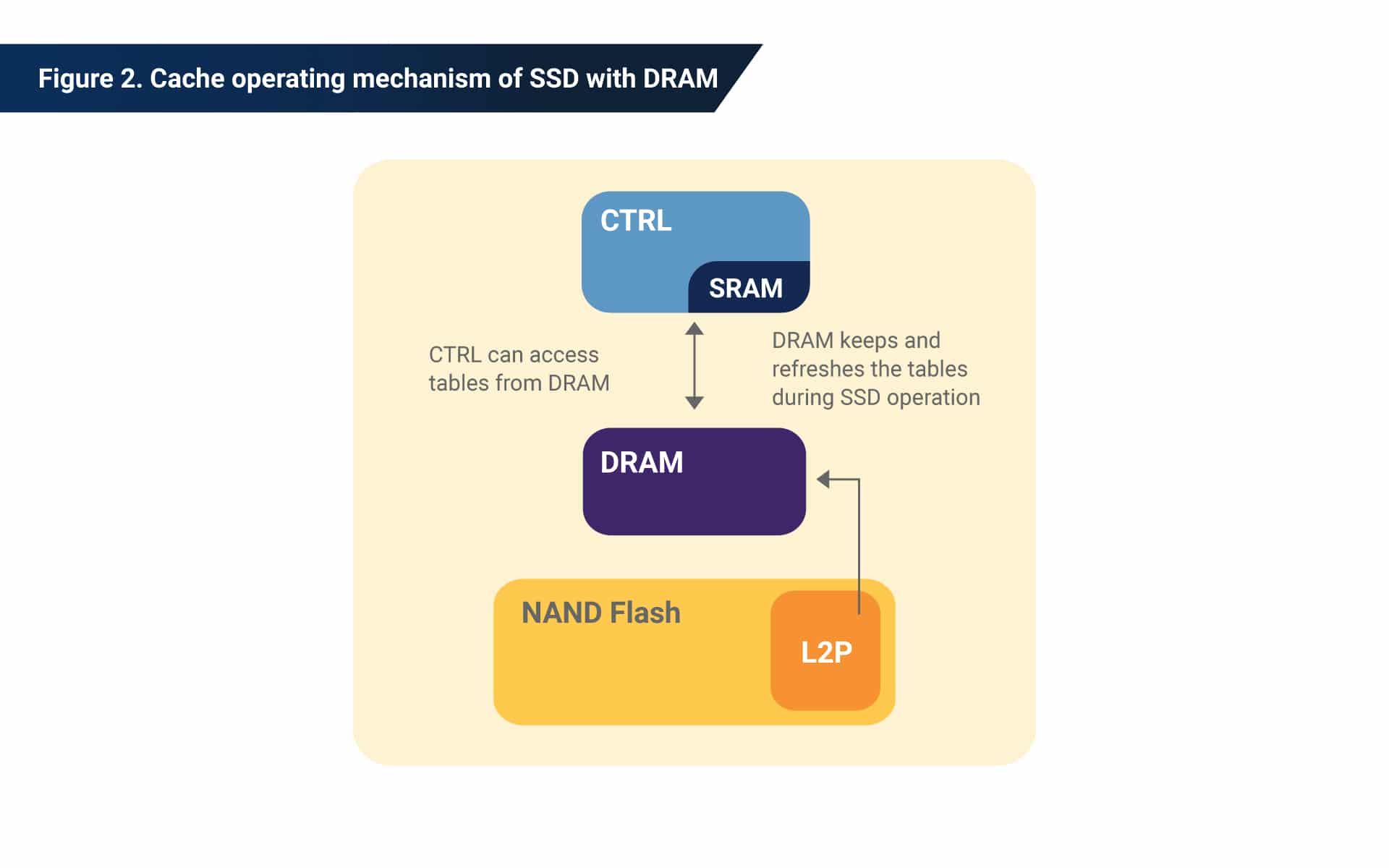

이전 SSD 설계에서는 비휘발성 플래시 장치와 휘발성 RAM을 모두 사용하여 데이터 처리 효율성을 높였습니다. 특히 DRAM 장치는 두 가지 이유로 버퍼로 사용됩니다.

-

-

- DRAM 장치는 휘발성이며 전원이 꺼지면 데이터를 추적하지 못합니다. 이는 RAM이 장기 데이터 저장에 적합하지 않음을 의미합니다.

- RAM 장치는 플래시 장치보다 빠른 속도로 읽거나 쓸 수 있습니다. 이 속성을 통해 RAM은 호스트의 데이터를 일시적으로 중지하는 "중계 스테이션" 역할을 하는 동시에 플래시 스토리지가 지속적으로 작업을 처리할 때 유예를 제공합니다.

-

DRAM에 캐시되거나 DRAM에서 검색되는 가장 중요한 정보는 논리적 주소를 NAND 플래시 어레이 내 저장된 데이터의 물리적 위치로 바꾸는 매핑 정보입니다. 이 정보는 L2P(논리-물리) 테이블이라는 매핑 테이블에 저장되며 SSD가 플래시 스토리지 안팎으로 데이터를 이동할 때 자주 업데이트됩니다. 셧다운 중에는 L2P 테이블이 플래시 메모리에 저장됩니다. DRAM은 지속적인 전원 공급 없이 빠르게 작동할 수 없게 되기 때문입니다.

반면 전원이 켜진 시나리오에서는 L2P 테이블이 DRAM에 업로드되어 컨트롤러에서 지속적으로 업데이트할 수 있습니다. DRAM 크기가 클수록 컨트롤러에서 사용할 수 있는 여유 공간이 늘어납니다. 이는 일반적으로 보다 유연한 데이터 배치를 의미하므로 명령 수신 시 반응 시간이 향상됩니다. 일반적인 데이터 워크로드 측면에서 소위 "무작위 읽기" 시퀀스를 요구하는 작업은 충분한 DRAM 공간에서 가장 많은 이점을 얻습니다.

그러나 DRAM과 같은 귀중한 리소스는 플래시 스토리지에 비해 비용이 많이 듭니다. 밀도를 통제하면 현재 DRAM 가격은 NAND 플래시 메모리 평균 가격의 10배 이상이며 이것이 곧 바뀔 조짐은 없습니다.

DRAM의 이점에도 불구하고 지난 10년 동안 DRAM이 장착되지 않은 SSD가 도입되었습니다. 이러한 "DRAM 없는" 드라이브는 비용 절감 및 물리적 크기 축소와 같은 이점을 제공했습니다.

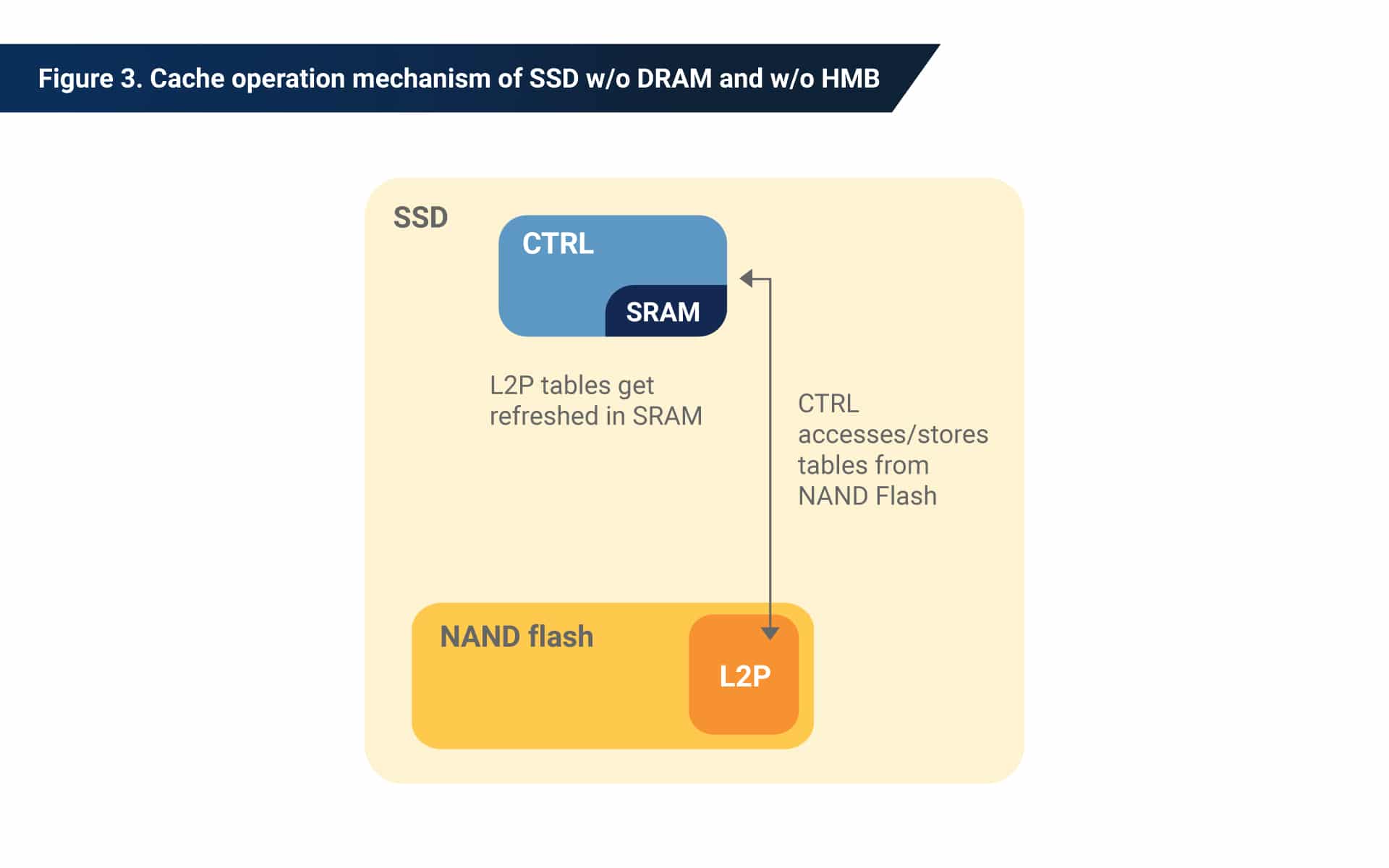

그러나 DRAM이 없는 SSD도 정확하게 "만능" 솔루션은 아닙니다. DRAM이 없는 SSD의 성능은 일반적으로 중간 데이터 및 매핑 테이블용으로 예약된 캐싱 공간의 본질적인 결함으로 인해 저하됩니다.

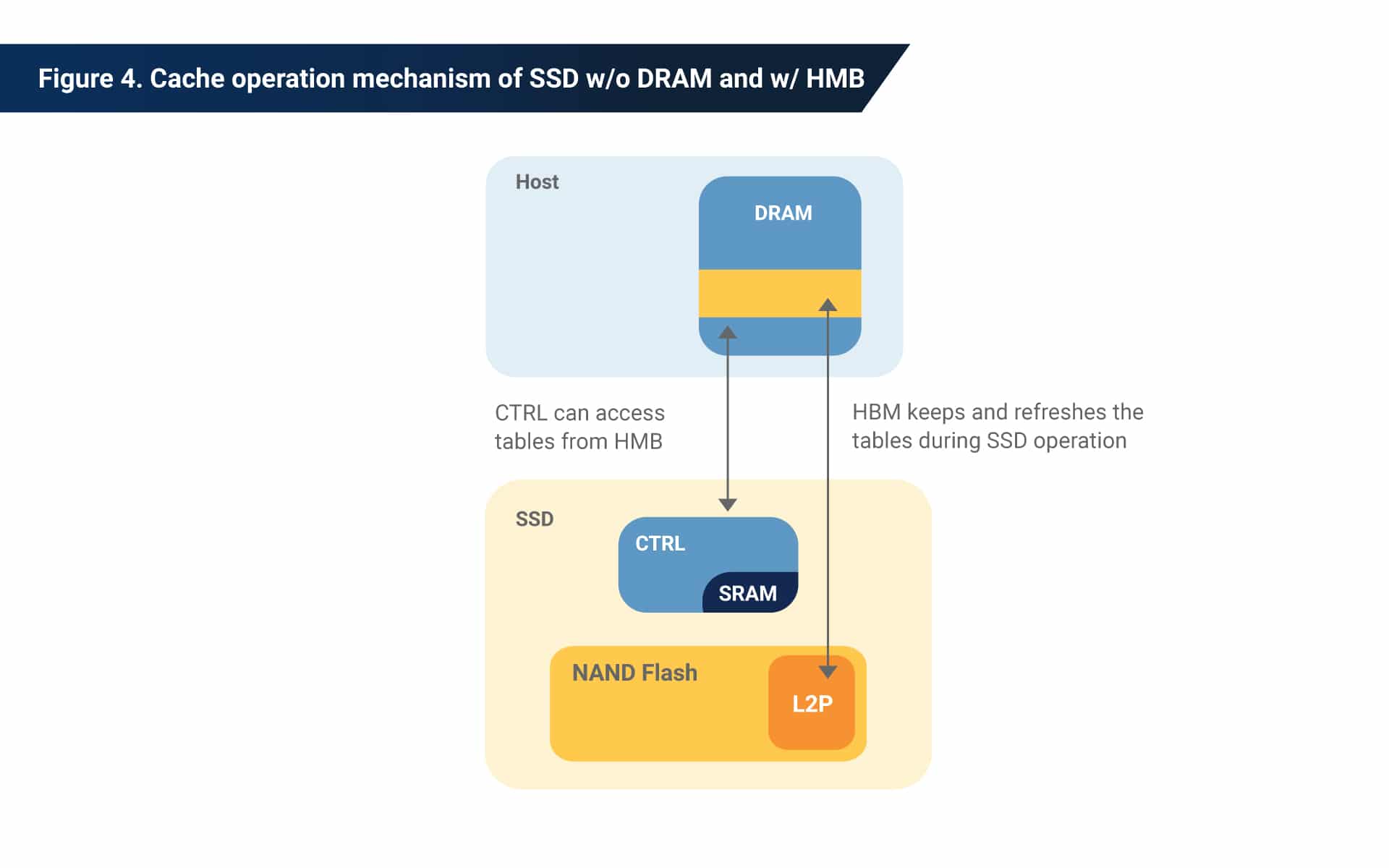

DRAM이 없는 디자인도 L2P 테이블을 NAND 메모리에 유지하지만 DRAM이 장착된 디자인과 중요한 차이점이 있습니다. 컨트롤러가 NAND 플래시 메모리에서 이러한 테이블에 액세스하려고 시도하면 정보가 업데이트되고 활용되면서 컨트롤러의 내부 SRAM(정적 RAM)에 로드됩니다. 그런 다음 이러한 테이블은 저장을 위해 NAND 플래시 메모리에 다시 배치됩니다.

여기서 주요 차이점은 SRAM을 캐싱 공간으로 사용한다는 것입니다. 그러나 SRAM은 DRAM보다 비용이 더 많이 드는 귀중한 고성능 리소스입니다. 또한 일반적인 플래시 컨트롤러에는 일반적으로 몇 메가바이트의 SRAM만 있습니다. 더 큰 버퍼 공간은 일반적으로 더 높은 효율로 이어지기 때문에 이러한 DRAM 없는 설계는 성능 관점에서 차선책으로 간주될 수 있습니다.

이 단점이 바로 HMB 기능이 설계된 이유입니다. SSD 작동 중에 L2P 테이블을 NAND 플래시에서 HMB로 직접 로드할 수 있습니다. 이러한 테이블은 기존 DRAM 방식과 거의 동일하게 호스트 측에서 버퍼 메모리에 지속적으로 새로 고칠 수 있습니다.

HMB가 활성화된 SSD는 일반적으로 임의 워크로드를 처리하는 효율성 저하가 훨씬 적거나 전혀 없습니다. 다음 섹션에서는 HMB 성능에 대한 구체적인 실제 테스트 데이터를 살펴보겠습니다.

HMB 성능 개선: 유무 비교

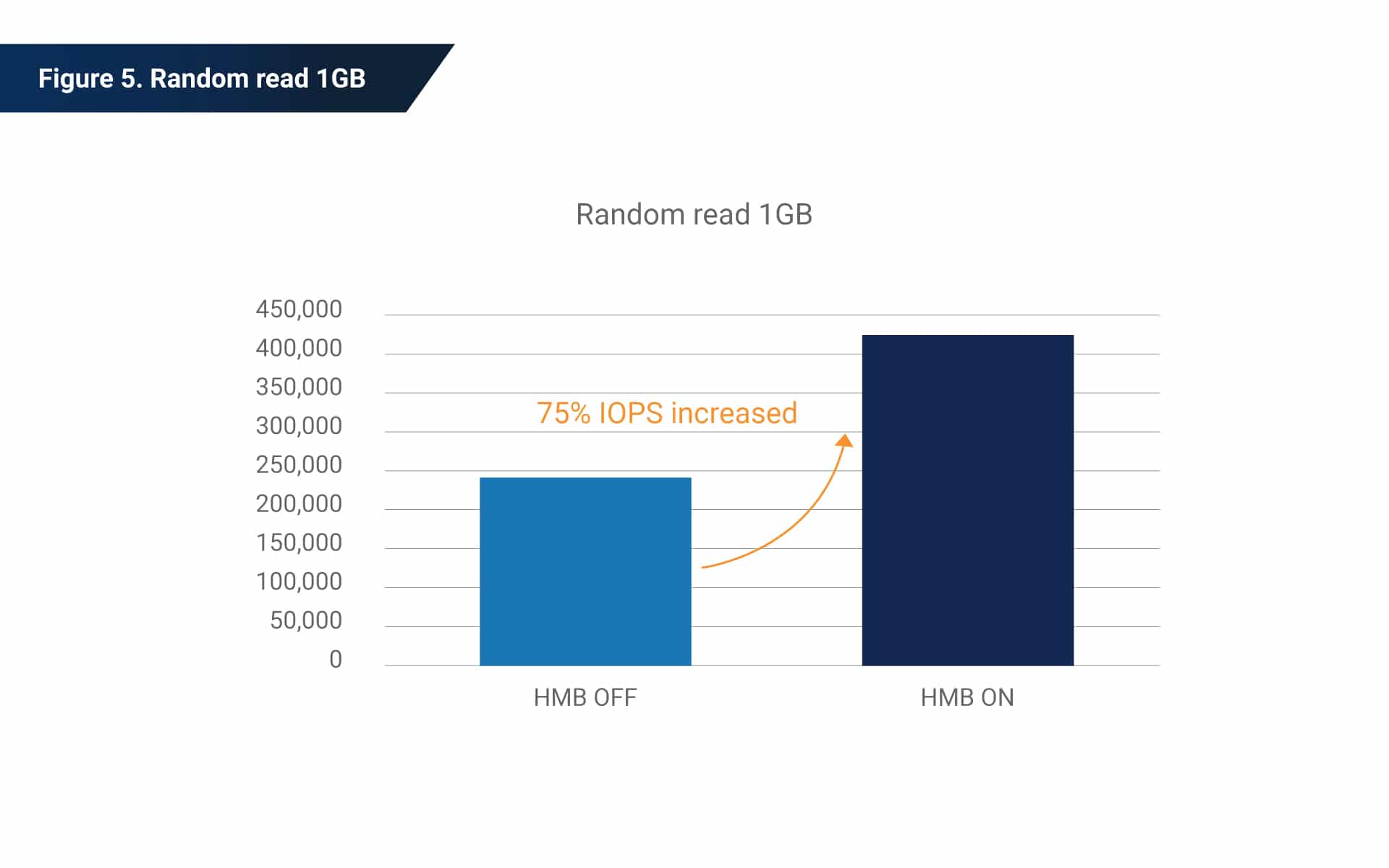

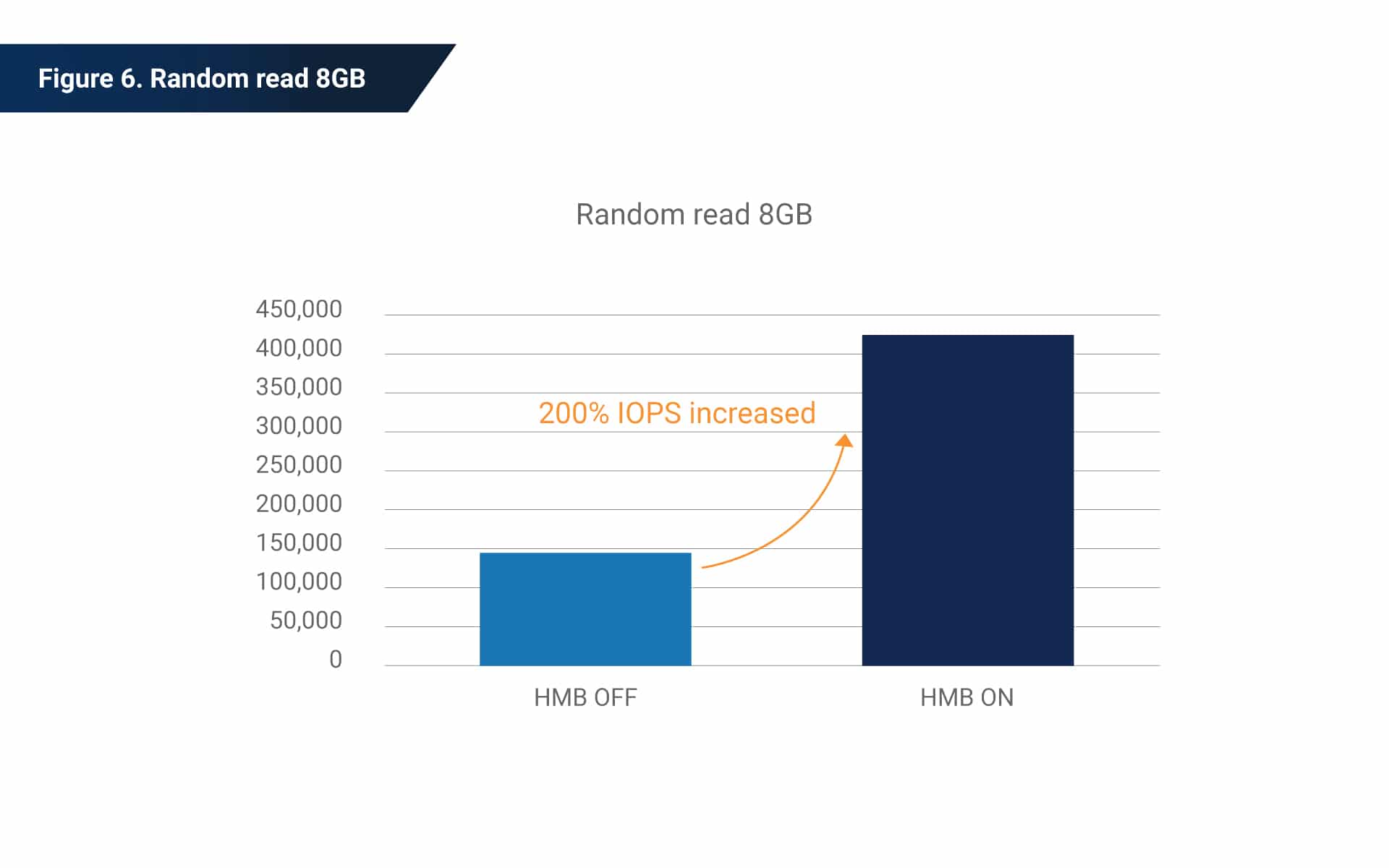

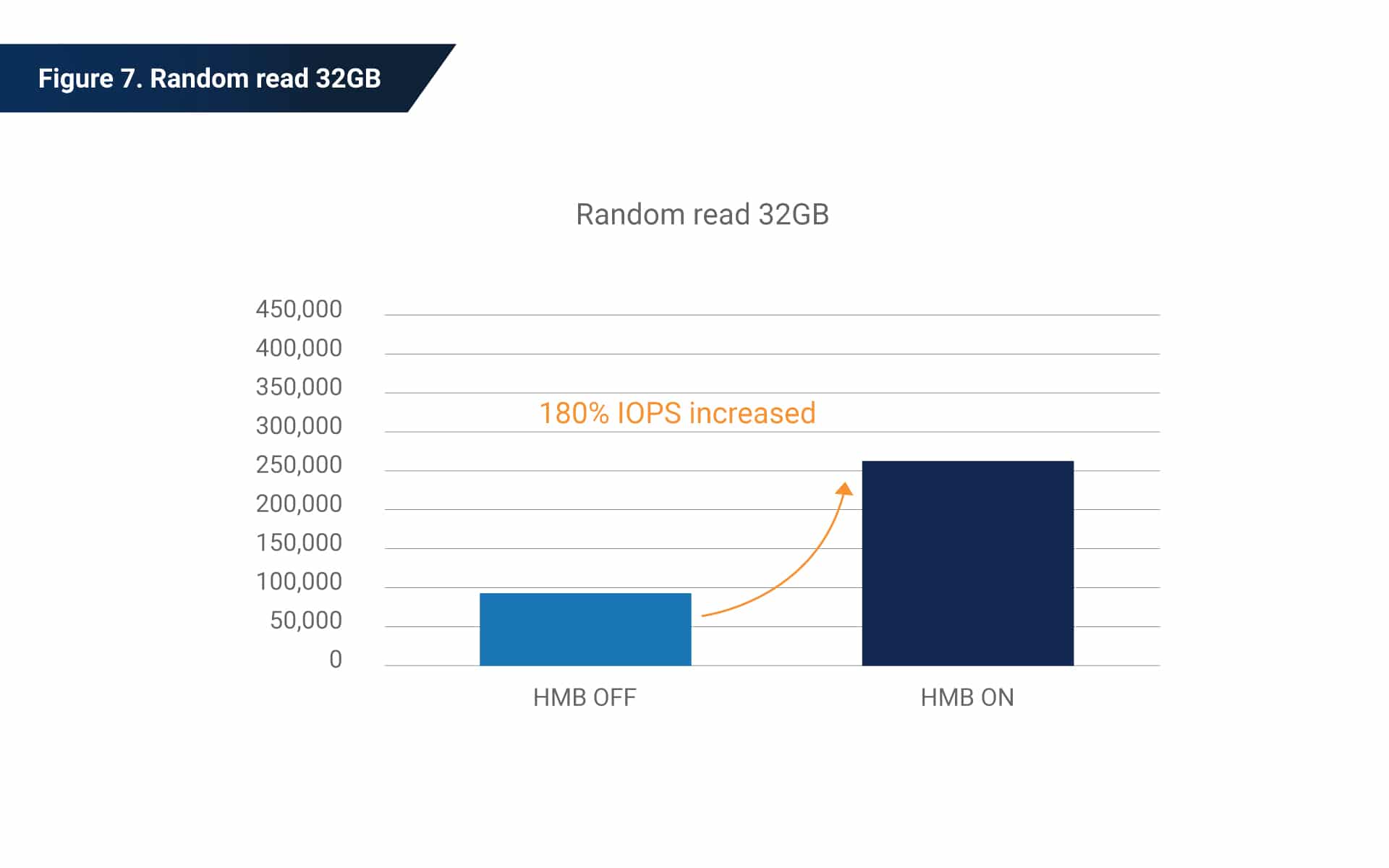

HMB를 활성화하면 SSD는 일반적으로 소위 "무작위 읽기"에서 성능이 향상됩니다. 이러한 작업은 미리 결정된 크기의 데이터(단, 플래시 스토리지 내의 예측할 수 없는 위치에서)가 컨트롤러 수준 조작을 통해 호스트 요청별로 검색되는 경우입니다.

그러나 HMB 성능 향상은 워크로드에 따라 다를 수도 있습니다. 이는 호스트가 항상 플래시 컨트롤러가 요구하는 실제 내부 메모리 공간을 제공하지 못할 수 있기 때문입니다.

이 그래프는 HMB 사용으로 인한 비선형 성능 향상을 보여주며, 1기가바이트 상당의 데이터 처리에서 32기가바이트로 워크로드를 확장합니다. 이는 HMB의 DRAM 용량 제한 때문입니다.

L2P 테이블을 처리하고 더 많은 양의 중간 데이터를 처리함에 따라 제공된 HMB 공간으로의 로드 작업이 기하급수적으로 증가하기 시작하는 임계값에 도달합니다. 따라서 32GB의 데이터로 IOPS(초당 입력/출력 작업)의 증가는 8GB의 데이터보다 덜 중요합니다. 이것은 HMB가 다른 하드웨어 기술과 마찬가지로 성능 향상에 한계가 있음을 보여줍니다.

그러나 32GB에서도 HMB를 사용할 때 여전히 100,000개 이상의 추가 IOPS를 얻습니다. 이것은 쉽게 상당한 증가입니다. 힘들게 펌웨어를 최적화하더라도 수천 IOPS만 반환할 수 있습니다.

Phison이 세계 최고의 SSD에 HMB를 사용하는 방법

DRAM이 없는 SSD는 처음 출시된 이후 공급업체의 소위 "밸류 라인"의 일부로 광범위하게 배포되어 하드웨어 구성으로 인해 비용 효율성 측면에서 이점을 제공합니다. Phison은 컨트롤러 하드웨어 리소스를 남용하지 않고 성능을 개선하기 위해 하드웨어 및 펌웨어 노하우를 활용하여 자체 SSD에 HMB를 구현했습니다.

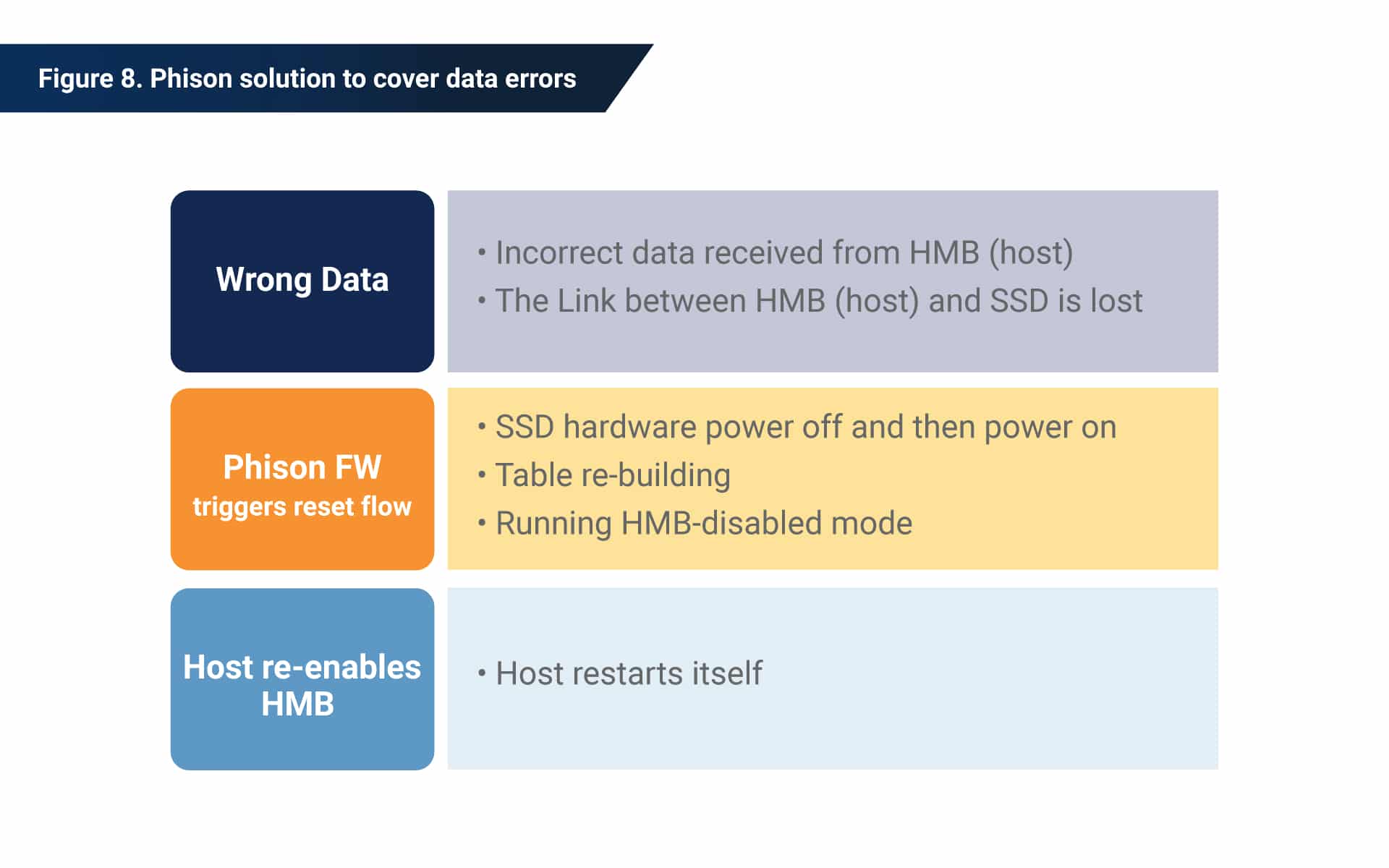

NVMe 프로토콜에 정의된 대로 플래시 컨트롤러는 HMB를 사용할 때 SSD가 예기치 않게 제거되는 경우 데이터 손실 또는 손상 가능성이 없음을 보장해야 합니다. 이 표준을 충족하기 위해 Phison의 컨트롤러 솔루션은 데이터 전송 오류를 제거하고 작동 중 데이터 무결성을 확인하도록 설계된 독점 펌웨어를 사용합니다.

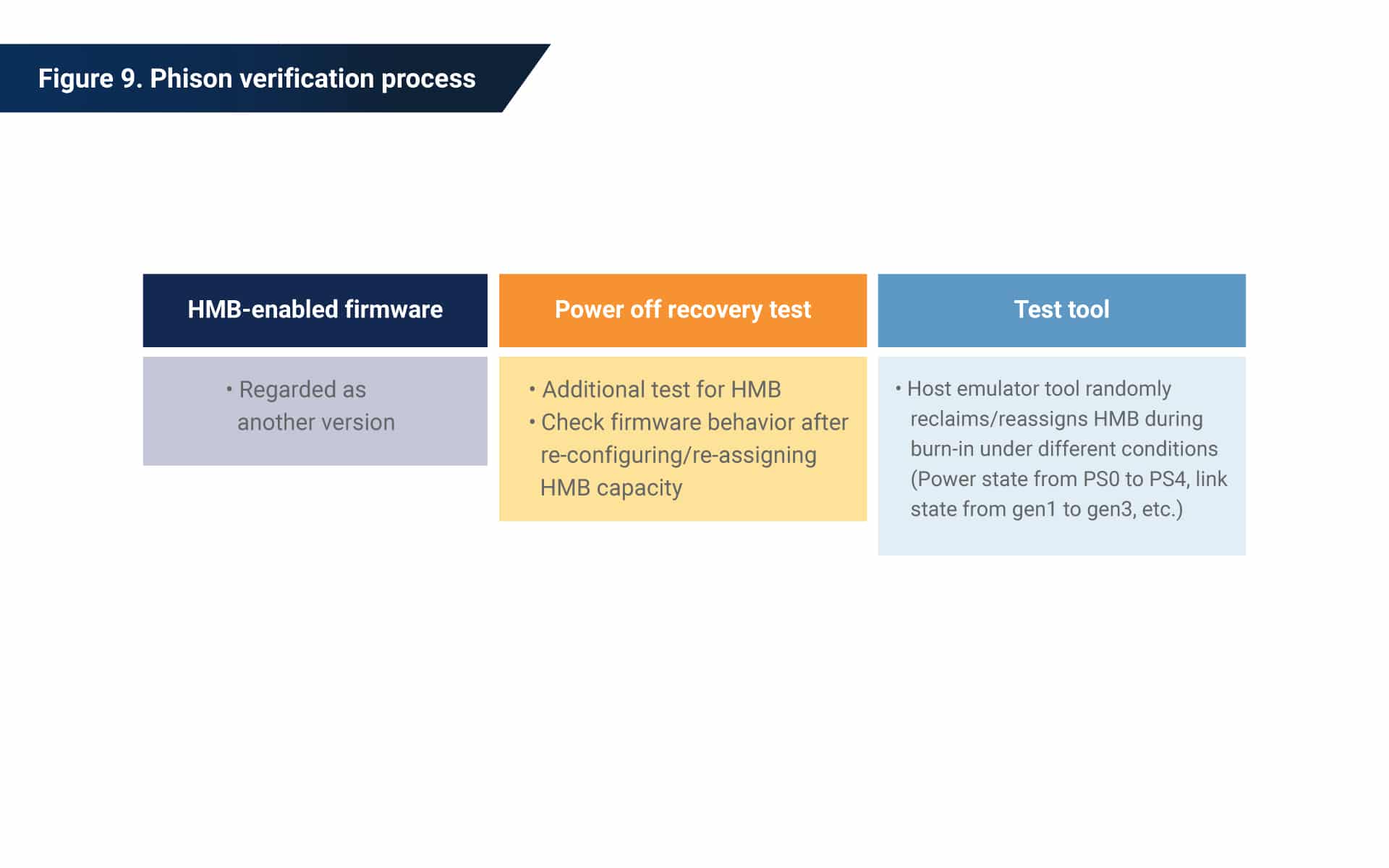

또한 Phison은 방대한 지식과 경험을 바탕으로 SSD 설계를 테스트하고 검증합니다. Phison은 철저한 기능 및 물리적 검증을 위해 컨트롤러 수준 및 시스템 수준 테스트를 모두 수행합니다.

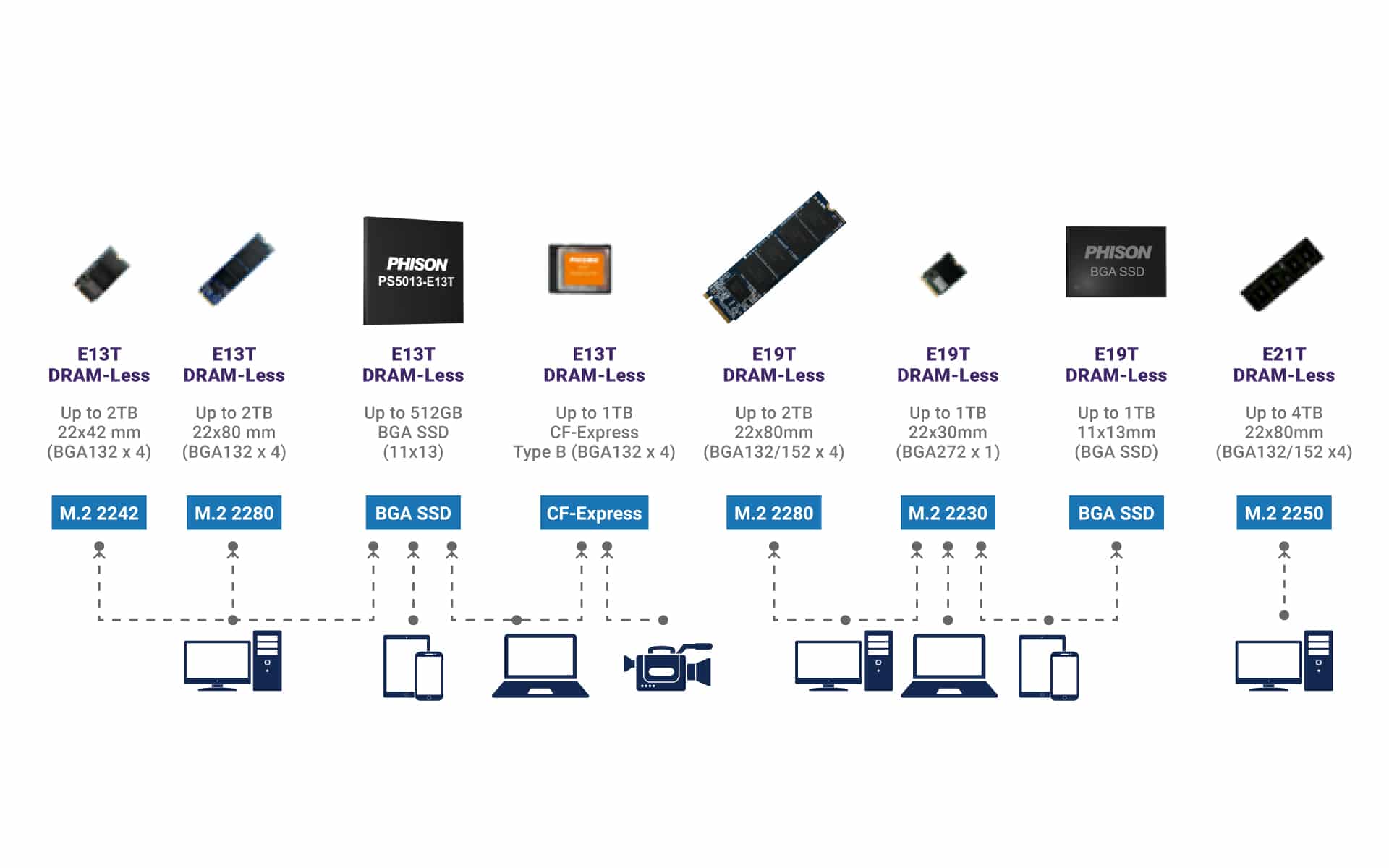

아래 차트는 다양한 산업 응용 분야에 적합한 Phison의 DRAM 없는 제품을 보여줍니다. 자세한 내용은 phison.com.