Einführung

Im Laufe der Jahrtausende hat die Menschheit eine altbewährte Formel für den technologischen Fortschritt entwickelt. Erfinder und Designer konzentrieren sich zunächst darauf, die allgemeinen Mechanismen einer neuen Technologie herauszufinden, bevor sie sich der Kosteneffizienz und Leistungsverbesserungen zuwenden.

Diese grundlegende Faustregel gilt für den Bereich Solid-State-Speicher ebenso wie für jede andere Disziplin oder Branche. In diesem Artikel untersuchen wir eine wichtige aktuelle Entwicklung, die dazu beitragen kann, die Leistung der Solid-State-Drive-Technologie zu steigern: Host Memory Buffer (HMB).

Die Kompromisse beim SSD-Speicherdesign

Beim Design eines Solid-State-Laufwerks (SSD) kann zusätzlicher Flash-Speicher die Gesamtkapazität des Laufwerks erhöhen und gleichzeitig die Leistung steigern. Wie bei jedem anderen Produktdesign müssen Ingenieure jedoch einen Kompromiss zwischen Ressourcen und Kosten eingehen.

Für das SSD-Design gibt es zwei Möglichkeiten, die Leistung jeder Einheit über ihre vorhandenen Fähigkeiten hinaus zu verbessern: entweder durch Erhöhung der Dichte des Flash-Speichers oder durch den Einbau von zusätzlichem Flash-Speicher auf Kosten von zusätzlichem physischem Speicherplatz. Da der Platz auf der Leiterplatte (PCB) unabhängig von der Wahl der Laufwerksformfaktoren begrenzt ist, geht dies jedoch in der Regel mit dem Wegfall anderer Komponenten auf der Platine einher.

Viele Anbieter entscheiden sich mittlerweile dafür, den schnellen, aber teuren DRAM (Dynamic Random Access Memory) aus ihren Laufwerksdesigns zu entfernen, um Kosteneinsparungen zu erzielen. Als flüchtiger Hochgeschwindigkeitsspeicher hat DRAM jedoch seine eigenen Zwecke und ist nicht einfach austauschbar. Ein DRAM-loses Design bringt auch seine eigenen Probleme mit sich, was die Abstimmung der Leistung und der Signalintegrität während der Datenübertragung betrifft, insbesondere bei zufälligen Lesevorgängen mit hohem Volumen.

Was ist ein Host-Speicherpuffer?

Wie können Designer also die Schwächen einer DRAM-losen SSD beheben? Die prägnante Antwort lautet: Host Memory Buffer (HMB)-Technologie. HMB ist eine Technik, die es SSDs ermöglicht, proaktiv eine höhere Leistung zu erzielen, indem sie die Speicherressourcen der Host-CPU nutzt.

NVMe (NVM Express oder Non-Volatile Memory Express) ist ein offener Standard, der definiert, wie auf den nichtflüchtigen Speicher eines Computers wie NAND-Flash-Speicher und SSDs zugegriffen wird. Die NVMe 1.2-Spezifikation war die erste, die die Host-Speicherpufferfunktion einführte.

Insbesondere wurde in NVMe 1.2 dargelegt, wie HMB die Zuweisung von Hostspeicher für die Verwendung von SSDs ermöglicht. Jede SSD mit der richtigen Konfiguration kann mit dem Host kommunizieren, um die erforderliche Mindestpuffergröße anzugeben. Die NVMe 1.2-Spezifikation enthielt auch Bedingungen und Einschränkungen für verschiedene Zwecke, beispielsweise um sicherzustellen, dass Daten nicht verloren gehen oder beschädigt werden, wenn das Laufwerk versehentlich entfernt wird.

Um die HMB-Funktion nutzen zu können, müssen sowohl das Laufwerk als auch das Betriebssystem diese unterstützen. Glücklicherweise erlaubt Microsoft die HMB-Unterstützung seit dem Windows 10 Creators Update (d. h. Version 1703), das 2017 veröffentlicht wurde.

Warum HMB? Von mit DRAM bis zu SSDs ohne DRAM

Frühere SSD-Designs verwendeten sowohl nichtflüchtige Flash-Geräte als auch flüchtigen RAM, um die Effizienz der Datenverarbeitung zu steigern. Insbesondere werden DRAM-Geräte aus zwei Gründen als Puffer verwendet:

-

-

- DRAM-Geräte sind flüchtig und verlieren den Überblick über ihre Daten, wenn der Strom abgeschaltet wird. Das bedeutet, dass RAM nicht für die langfristige Datenspeicherung geeignet ist.

- RAM-Geräte können mit einer höheren Geschwindigkeit gelesen oder beschrieben werden als Flash-Geräte. Dieses Attribut ermöglicht es dem RAM, als „Relaisstation“ zu fungieren, einem vorübergehenden Stopp für Daten vom Host, während dem Flash-Speicher eine Atempause gewährt wird, während er kontinuierlich Aufgaben verarbeitet.

-

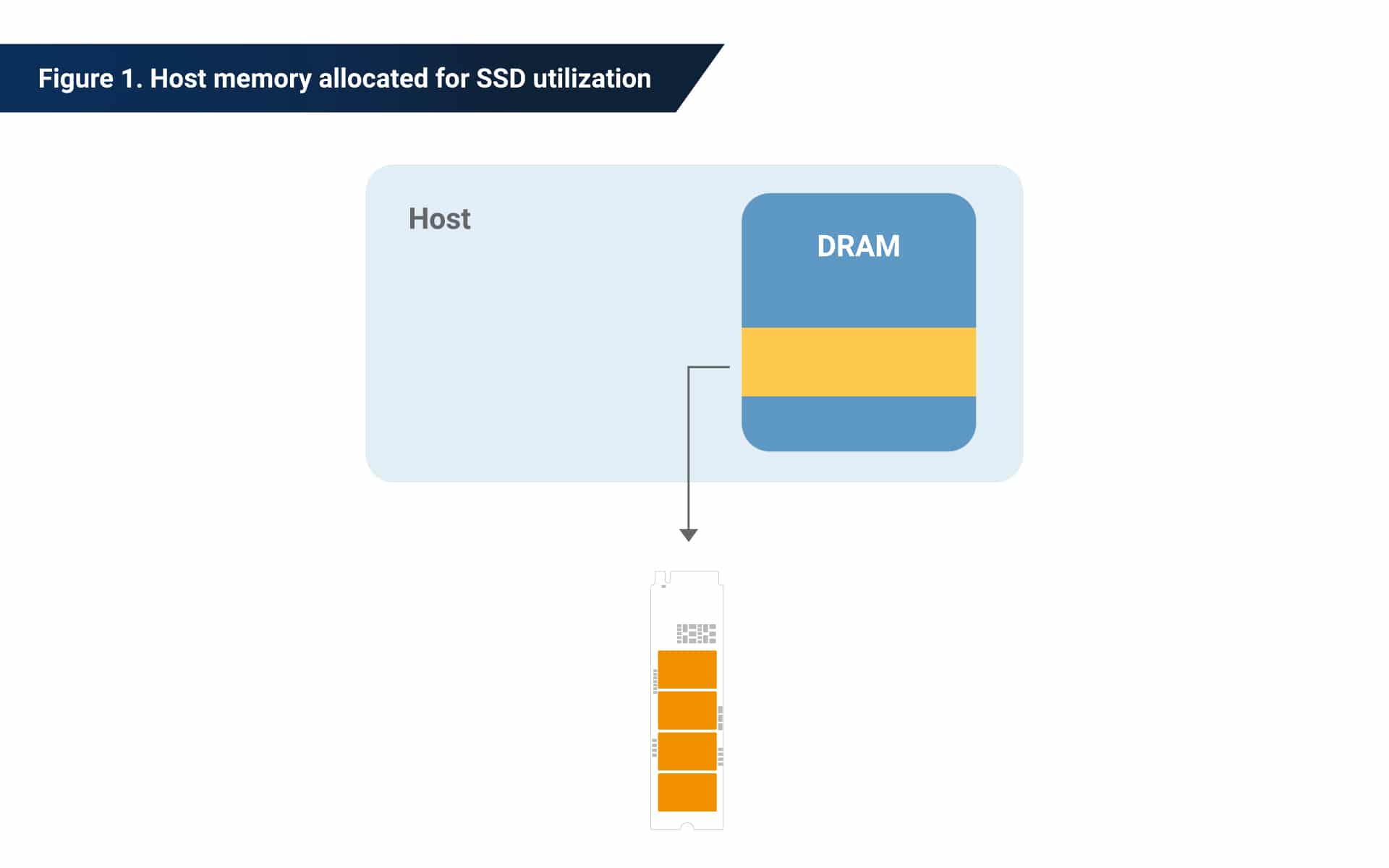

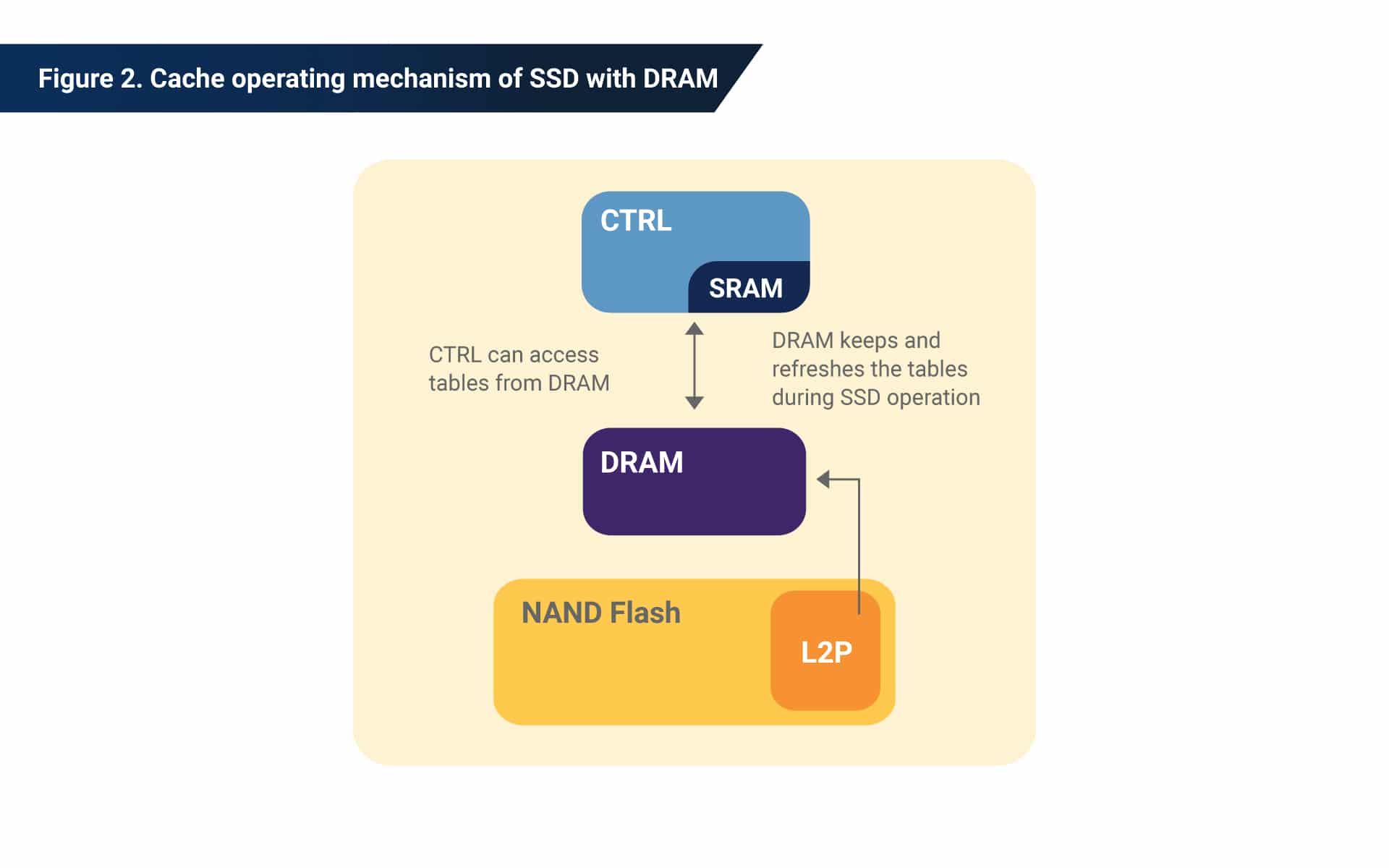

Die wichtigsten Informationen, die in einem DRAM zwischengespeichert oder von einem DRAM abgerufen werden, sind die Zuordnungsinformationen, die logische Adressen in die physischen Speicherorte der gespeicherten Daten innerhalb des NAND-Flash-Arrays umwandeln. Diese Informationen werden in Zuordnungstabellen namens L2P-Tabellen (logisch-zu-physikalisch) gespeichert und regelmäßig aktualisiert, wenn SSDs Daten in den Flash-Speicher und aus diesem heraus verschieben. Bei Abschaltungen wird die L2P-Tabelle im Flash-Speicher gespeichert, da DRAM ohne kontinuierliche Stromversorgung schnell funktionsunfähig wird.

Andererseits wird die L2P-Tabelle in eingeschalteten Szenarien in den DRAM hochgeladen, damit sie vom Controller ständig aktualisiert werden kann. Je größer die DRAM-Größe, desto mehr freier Speicherplatz steht dem Controller zum Spielen zur Verfügung. Dies bedeutet im Allgemeinen eine flexiblere Datenplatzierung und damit eine bessere Reaktionszeit beim Empfang von Befehlen. Im Hinblick auf typische Daten-Workloads profitieren Vorgänge, die sogenannte „Random Read“-Sequenzen erfordern, am meisten von reichlich DRAM-Speicherplatz.

Allerdings sind wertvolle Ressourcen wie DRAM im Vergleich zu Flash-Speicher mit hohen Kosten verbunden. Unter Berücksichtigung der Dichte liegen die aktuellen DRAM-Preise bei mehr als dem Zehnfachen der Durchschnittspreise für NAND-Flash-Speicher, und es gibt keine Anzeichen dafür, dass sich dies bald ändern wird.

Trotz der Vorteile von DRAM wurden im letzten Jahrzehnt SSDs ohne montiertes DRAM eingeführt. Diese „DRAM-losen“ Laufwerke boten Vorteile wie geringere Kosten und kleinere physische Abmessungen.

Aber DRAM-lose SSDs sind auch nicht gerade eine „Einheitslösung“, die für alle passt. Die Leistung von DRAM-losen SSDs leidet im Allgemeinen aufgrund angeborener Mängel im Caching-Bereich, der für Zwischendaten und Zuordnungstabellen reserviert ist.

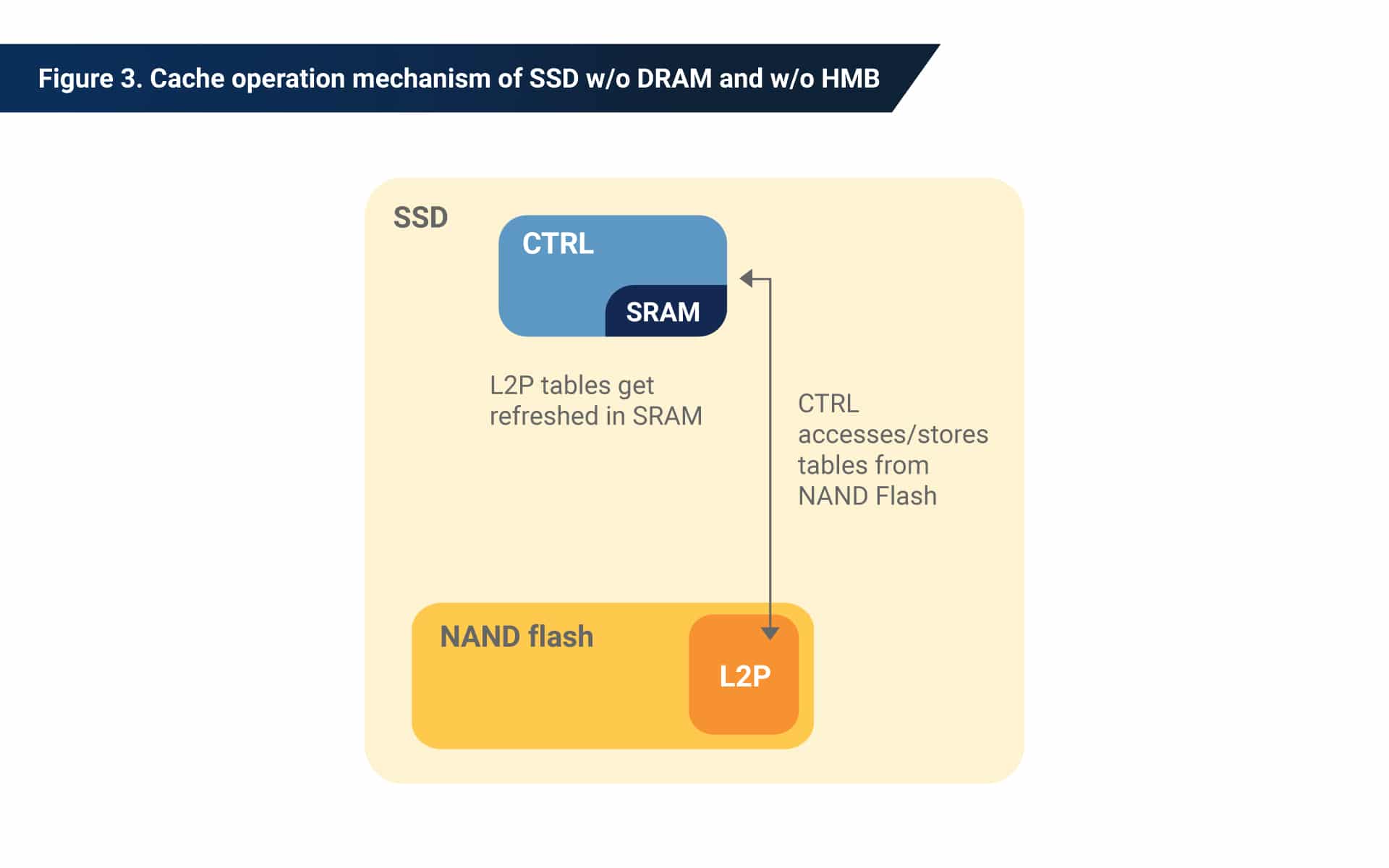

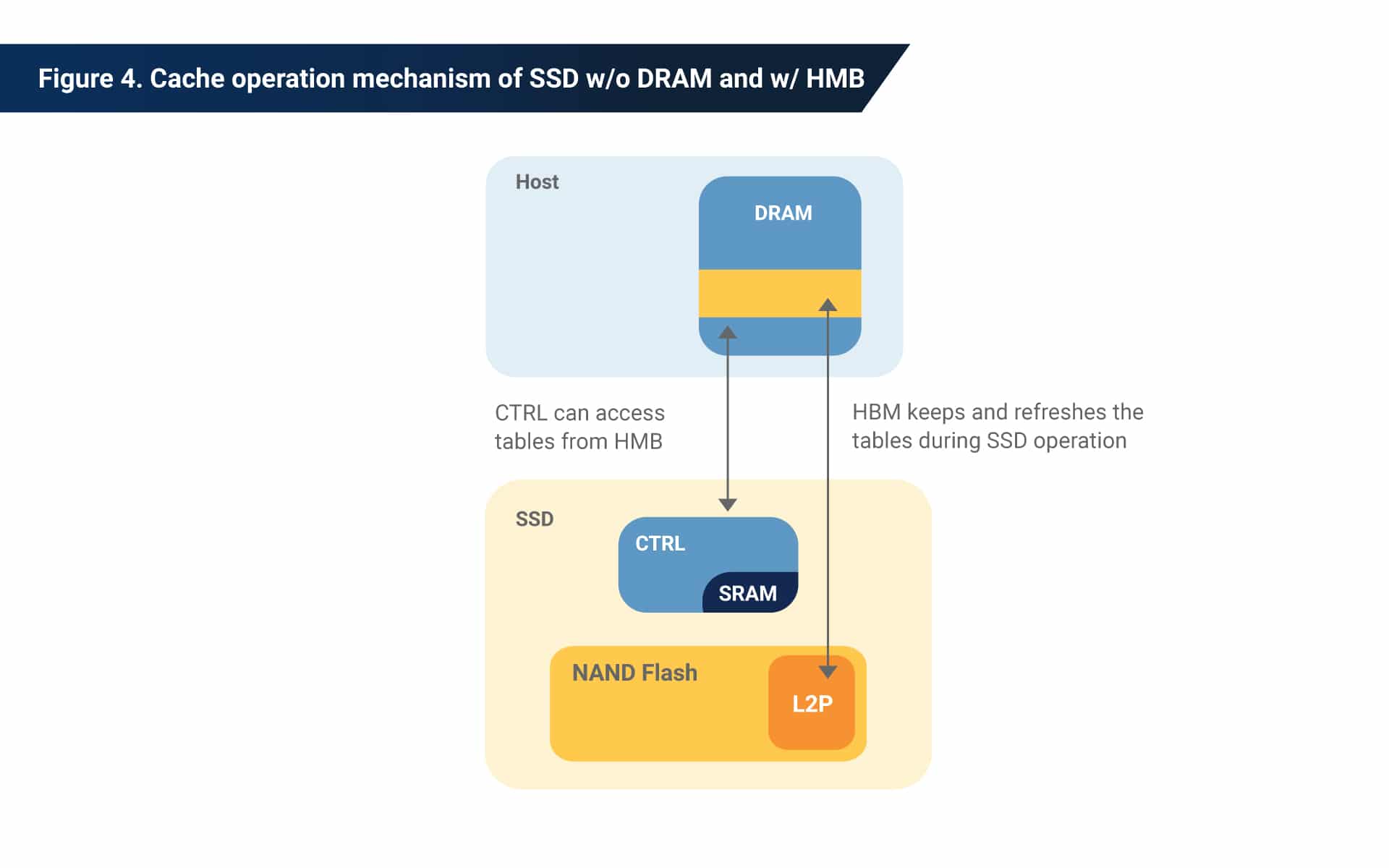

Obwohl DRAM-lose Designs auch L2P-Tabellen im NAND-Speicher behalten, weisen sie einen wichtigen Unterschied zu Designs mit montiertem DRAM auf. Wenn der Controller versucht, über den NAND-Flash-Speicher auf diese Tabellen zuzugreifen, werden die Informationen in den internen SRAM (statischen RAM) des Controllers geladen, während sie aktualisiert und genutzt werden. Anschließend werden diese Tabellen zur Speicherung erneut im NAND-Flash-Speicher abgelegt.

Der Hauptunterschied besteht hier in der Verwendung von SRAM als Caching-Speicherplatz. Allerdings ist SRAM eine wertvolle Hochleistungsressource mit noch höheren Kosten als DRAM. Darüber hinaus verfügt ein typischer Flash-Controller meist nur über wenige Megabyte SRAM. Da ein größerer Pufferraum typischerweise zu einer höheren Effizienz führt, können diese DRAM-losen Designs aus Leistungssicht als suboptimal angesehen werden.

Genau dieser Mangel ist der Grund, warum die HMB-Funktion entwickelt wurde. Im SSD-Betrieb können L2P-Tabellen direkt vom NAND-Flash auf HMB geladen werden. Diese Tabellen können vom Host aus kontinuierlich im Pufferspeicher aktualisiert werden, fast identisch mit der herkömmlichen DRAM-Methode.

Bei SSDs mit aktiviertem HMB kommt es im Allgemeinen zu deutlich geringeren bis möglicherweise gar keinen Leistungseinbußen bei der Bewältigung zufälliger Arbeitslasten. Im nächsten Abschnitt werden wir einige konkrete Testdaten aus der Praxis zur HMB-Leistung untersuchen.

HMB-Leistungsverbesserungen: mit vs. ohne

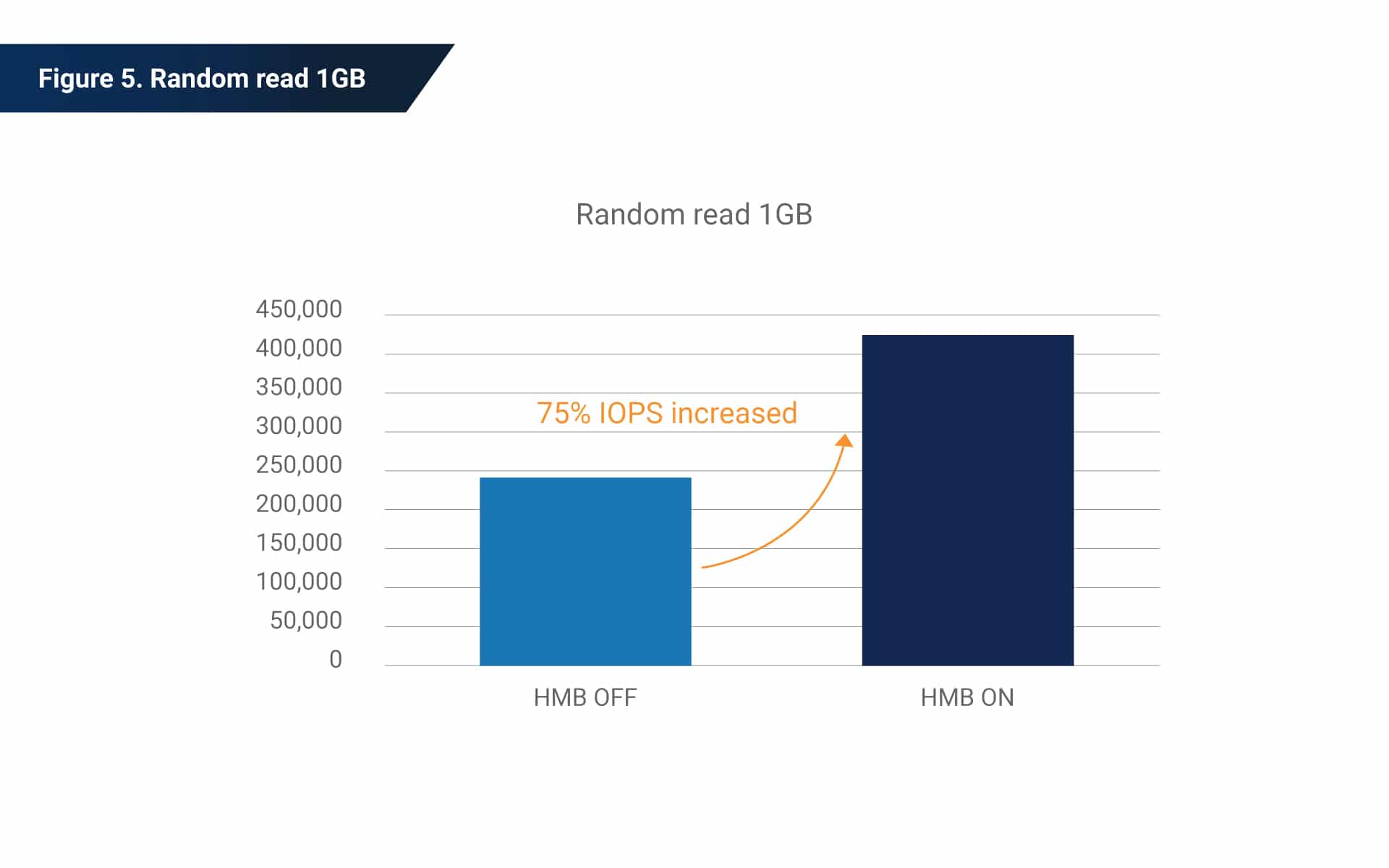

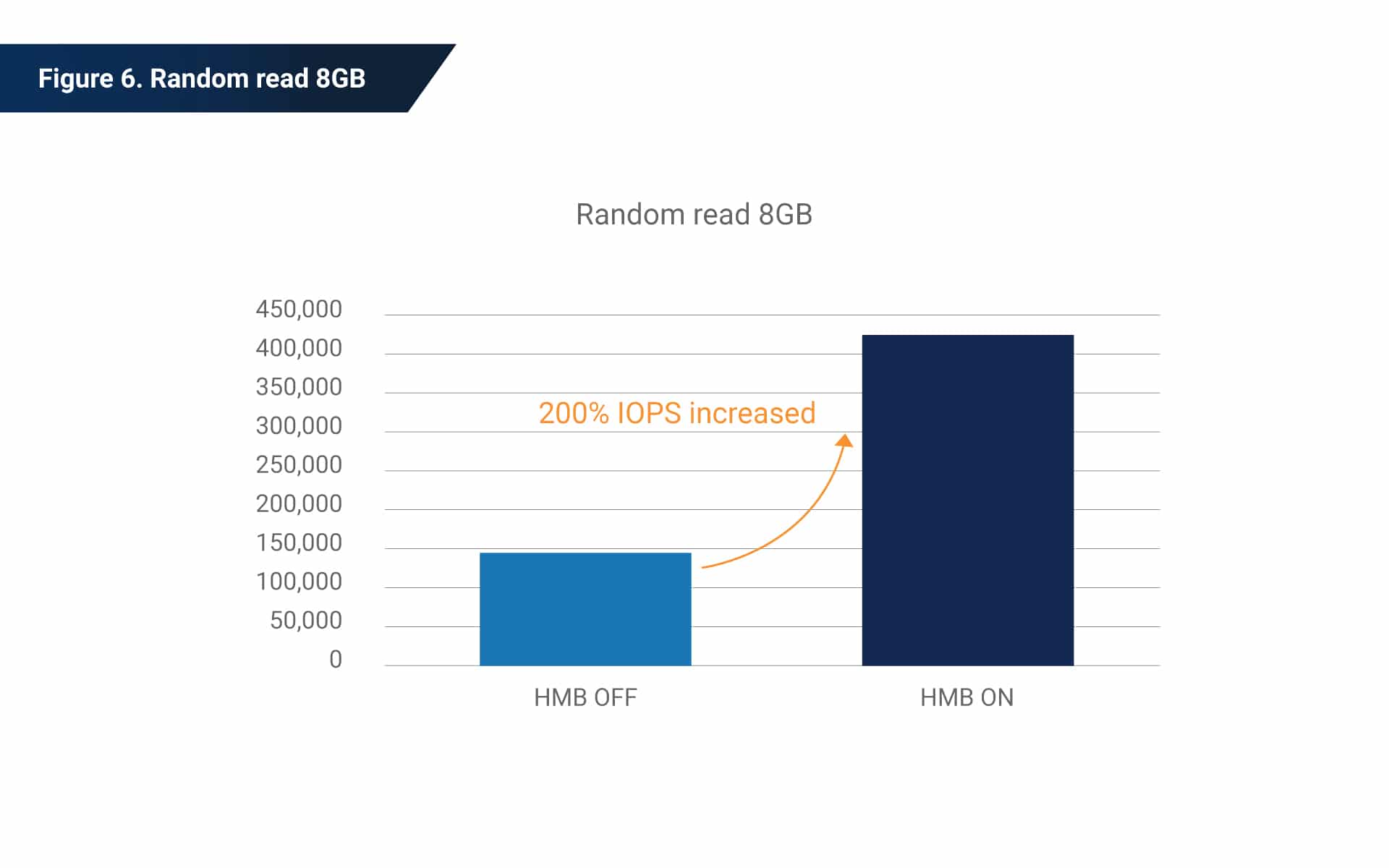

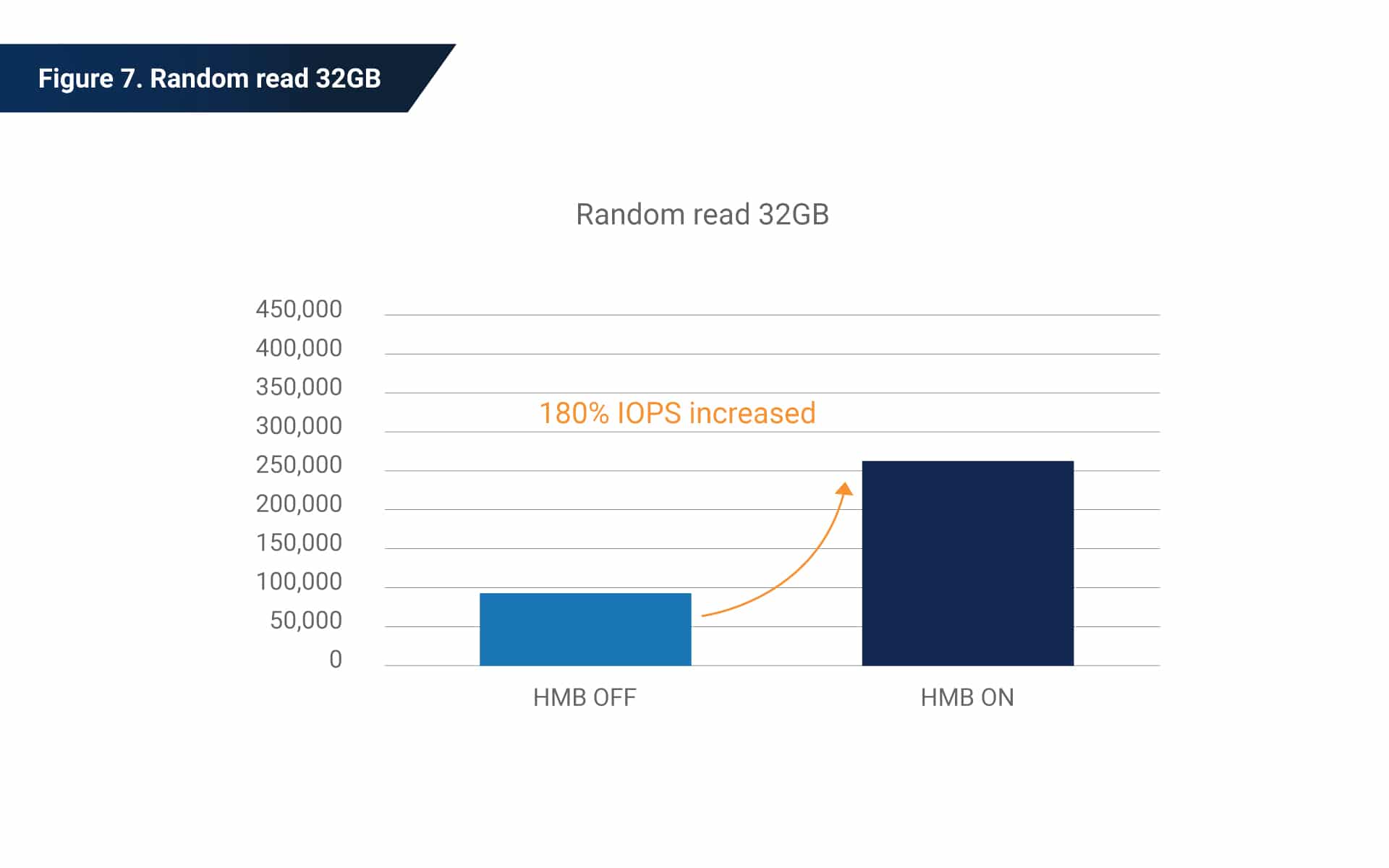

Wenn HMB aktiviert ist, verzeichnen SSDs im Allgemeinen Leistungsverbesserungen bei sogenannten „zufälligen Lesevorgängen“. Bei diesen Vorgängen werden Daten einer vorgegebenen Größe (aber von unvorhersehbaren Orten im Flash-Speicher) per Host-Anfrage über Manöver auf Controller-Ebene abgerufen.

Allerdings können die HMB-Leistungssteigerungen auch je nach Arbeitslast variieren. Dies liegt daran, dass der Host möglicherweise nicht immer in der Lage ist, die tatsächliche Menge an internem Speicherplatz bereitzustellen, die der Flash-Controller benötigt.

Diese Diagramme zeigen eine nichtlineare Leistungssteigerung durch die Verwendung von HMB, wodurch die Arbeitslast von der Verarbeitung von Daten im Wert von 1 Gigabyte auf 32 Gigabyte skaliert wird. Dies liegt an der DRAM-Kapazitätsbeschränkung von HMB.

Wenn wir die L2P-Tabellen bearbeiten und größere Mengen an Zwischendaten verarbeiten, erreichen wir einen Schwellenwert, an dem Ladevorgänge in den bereitgestellten HMB-Speicher exponentiell ansteigen. Somit fällt der Anstieg der IOPS (Eingabe-/Ausgabeoperationen pro Sekunde) bei 32 Gigabyte Daten weniger stark aus als bei nur 8 Gigabyte Daten. Dies zeigt, dass bei HMB, wie bei jeder Hardwaretechnologie, die Leistungsverbesserungen begrenzt sind.

Selbst mit 32 Gigabyte erhalten wir jedoch immer noch mehr als 100.000 zusätzliche IOPS bei Verwendung von HMB. Das ist durchaus eine deutliche Steigerung – selbst eine sorgfältige Firmware-Optimierung kann nur zu mehreren tausend IOPS führen.

Wie Phison HMB für die weltbesten SSDs nutzt

Seit ihrer Erstveröffentlichung werden SSDs ohne DRAM als Teil der sogenannten „Value Line“ von Anbietern weit verbreitet eingesetzt und bieten aufgrund ihrer Hardwarekonfiguration Vorteile bei der Kosteneffizienz. Phison hat HMB in seinen eigenen SSDs implementiert und nutzt dabei unser Hardware- und Firmware-Know-how, um die Leistung zu verbessern, ohne Controller-Hardwareressourcen zu missbrauchen.

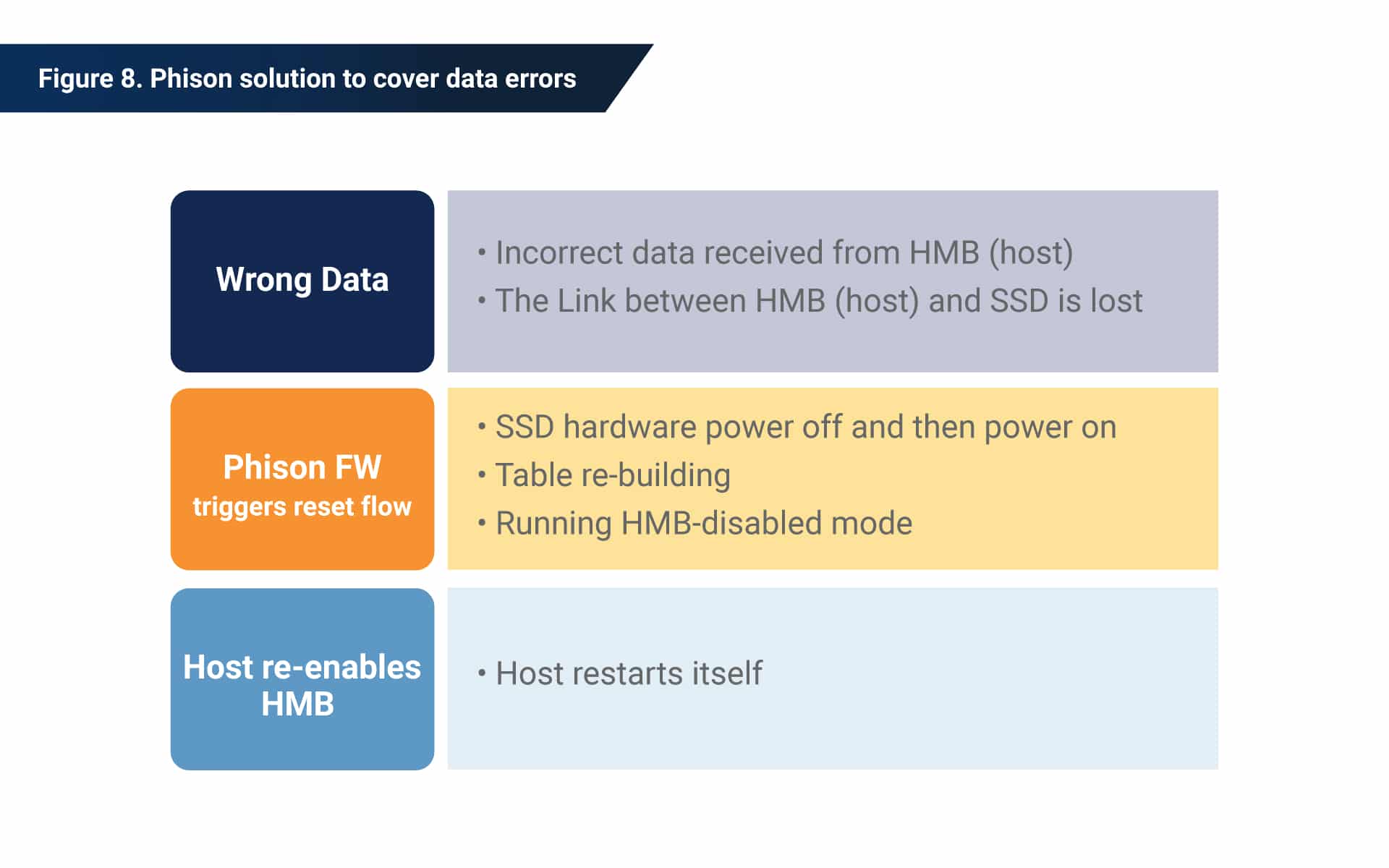

Wie im NVMe-Protokoll definiert, müssen Flash-Controller garantieren, dass bei Verwendung von HMB kein Risiko für Datenverlust oder -beschädigung besteht, wenn die SSD unerwartet entfernt wird. Um diesen Standard zu erfüllen, verwenden die Controller-Lösungen von Phison proprietäre Firmware, die darauf ausgelegt ist, Datenübertragungsfehler zu beseitigen und die Datenintegrität während des Betriebs zu bestätigen.

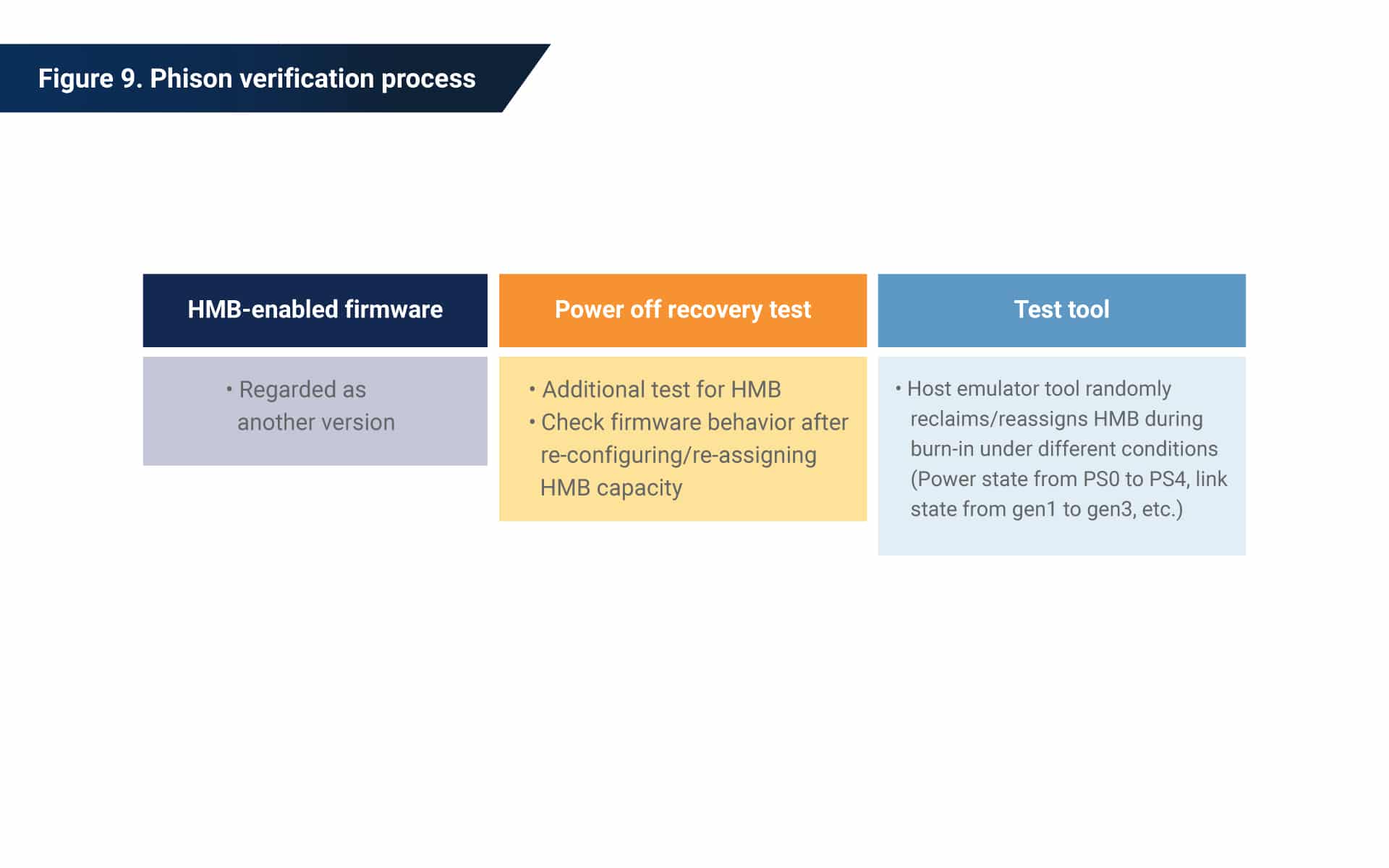

Darüber hinaus greift Phison auf sein umfangreiches Wissen und seine Erfahrung zurück, um seine SSD-Designs zu testen und zu validieren. Phison führt Tests sowohl auf Controller- als auch auf Systemebene zur gründlichen funktionalen und physischen Überprüfung durch.

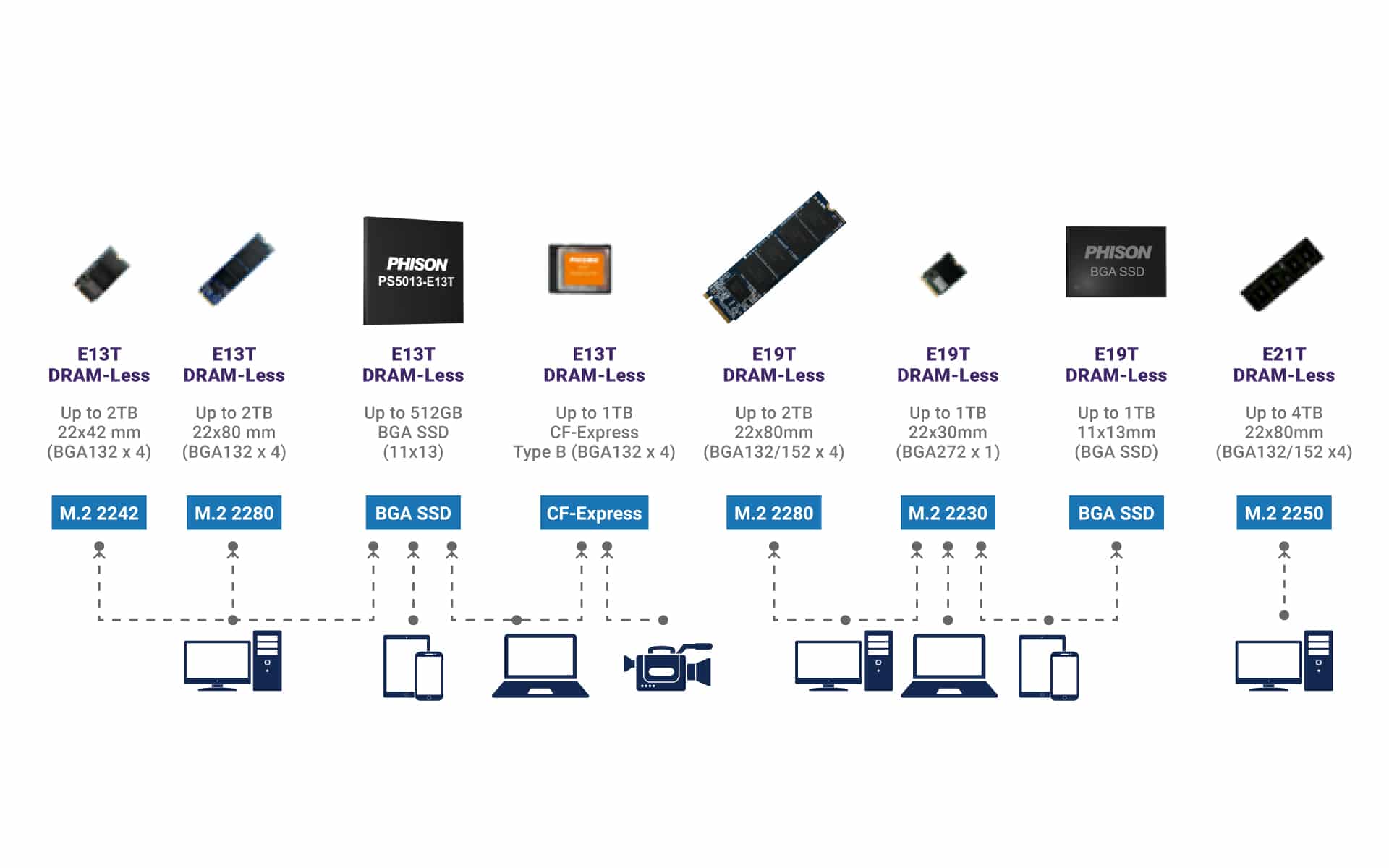

Die folgende Tabelle zeigt, welche DRAM-losen Produkte Phison herstellt, die für verschiedene Branchenanwendungen geeignet sind. Erfahren Sie mehr unter phison.com.