介绍

几千年来,人类已经开发出一种陈旧且经过时间考验的公式来实现技术进步。发明家和设计师首先专注于弄清楚新技术的一般机制,然后再转向成本效率和性能改进。

这一基本经验法则适用于固态存储领域,也适用于任何其他学科或行业。在本文中,我们将探讨一项有助于提高固态硬盘技术性能的最新重要发展:主机内存缓冲区 (HMB)。

SSD内存设计的权衡

在固态硬盘 (SSD) 的设计中,额外的闪存可以增加整体驱动器容量,同时提高性能。然而,与任何其他产品设计一样,工程师必须在资源和成本之间进行权衡。

对于SSD设计,有两种方法可以提高每个单元的性能超出其现有能力:要么增加闪存的密度,要么以额外的物理空间为代价安装额外的闪存。然而,无论选择何种驱动器外形尺寸,印刷电路板 (PCB) 空间都是有限的,这通常是以省略板上其他组件为代价的。

许多供应商现在选择从其驱动器设计中去除快速但昂贵的 DRAM(动态随机存取存储器),以降低成本。然而,作为一种高速易失性存储器,DRAM 有其自身的用途,并且不易被替代。无 DRAM 设计在数据传输过程中的性能和信号完整性调整方面也面临着自己的问题,尤其是在大容量随机读取情况下。

什么是主机内存缓冲区?

那么设计人员如何解决无 DRAM SSD 的弱点呢?简洁的答案是主机内存缓冲区(HMB)技术。 HMB 是一种允许 SSD 通过利用主机 CPU 的内存资源主动追求更高性能的技术。

NVMe(NVM Express 或 Non-Volatile Memory Express)是一种开放标准,定义了如何访问计算机的非易失性存储器,例如 NAND 闪存和 SSD。 NVMe 1.2规范首先引入了主机内存缓冲区功能。

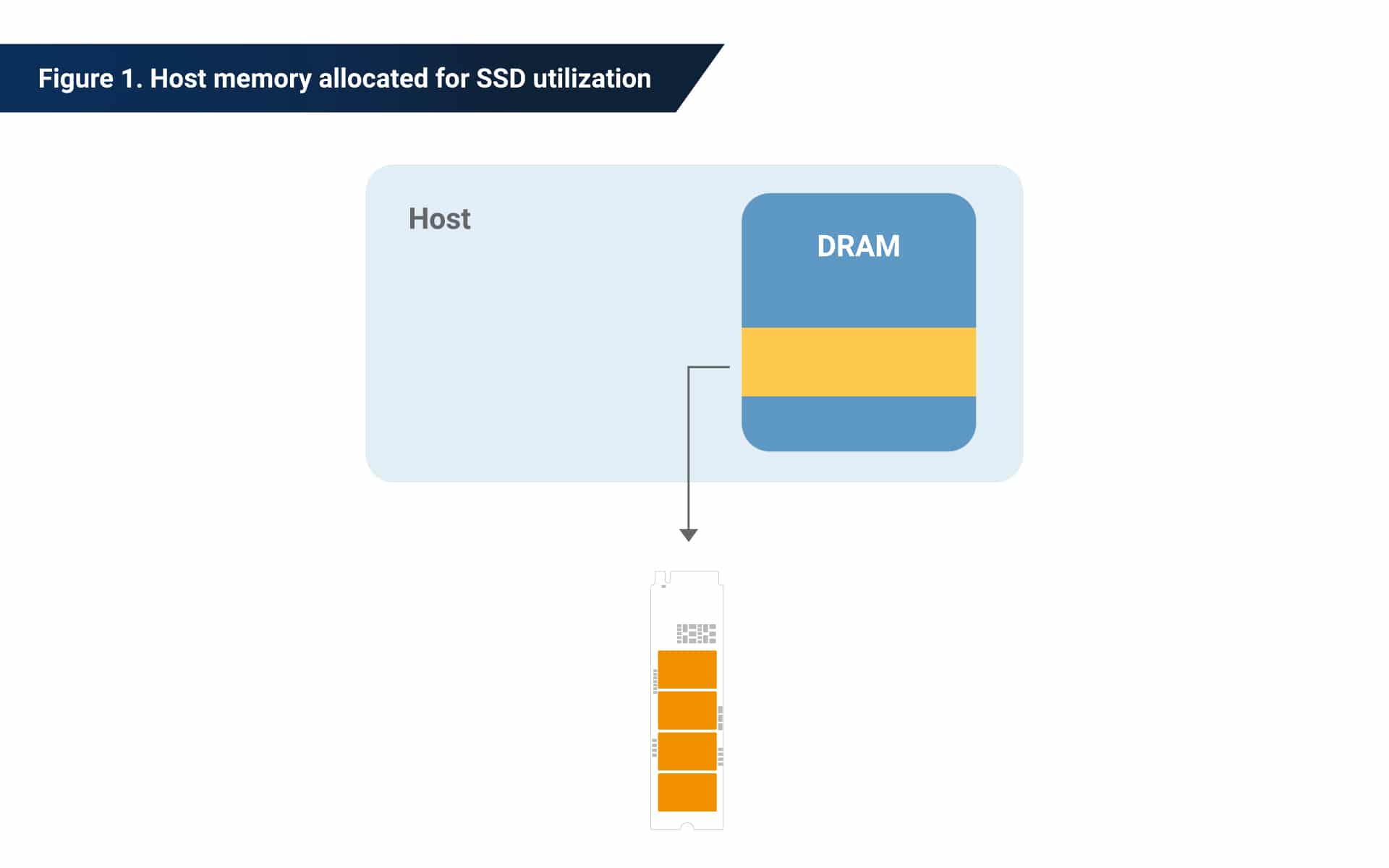

具体来说,NVMe 1.2 概述了 HMB 如何允许分配主机内存以供 SSD 使用。任何具有正确配置的 SSD 都可以与主机通信以指定其所需的最小缓冲区大小。 NVMe 1.2 规范还包括用于各种目的的条件和限制,例如确保在意外移除驱动器时数据不会丢失或损坏。

要使用 HMB 功能,驱动器和操作系统都必须支持它。幸运的是,微软从 2017 年发布的 Windows 10 Creators Update(即版本 1703)开始就允许 HMB 支持。

为什么选择HMB?从使用 DRAM 到不使用 DRAM SSD

早期的 SSD 设计同时使用非易失性闪存设备和易失性 RAM 来提高数据处理效率。具体来说,DRAM 设备用作缓冲区有两个原因:

-

-

- DRAM 设备具有易失性,当电源关闭时会丢失数据。这意味着RAM不适合长期存储数据。

- RAM 设备的读取或写入速度比闪存设备更高。此属性允许 RAM 充当“中继站”,即来自主机的数据的临时停止,同时在闪存持续处理任务时给予闪存存储喘息的机会。

-

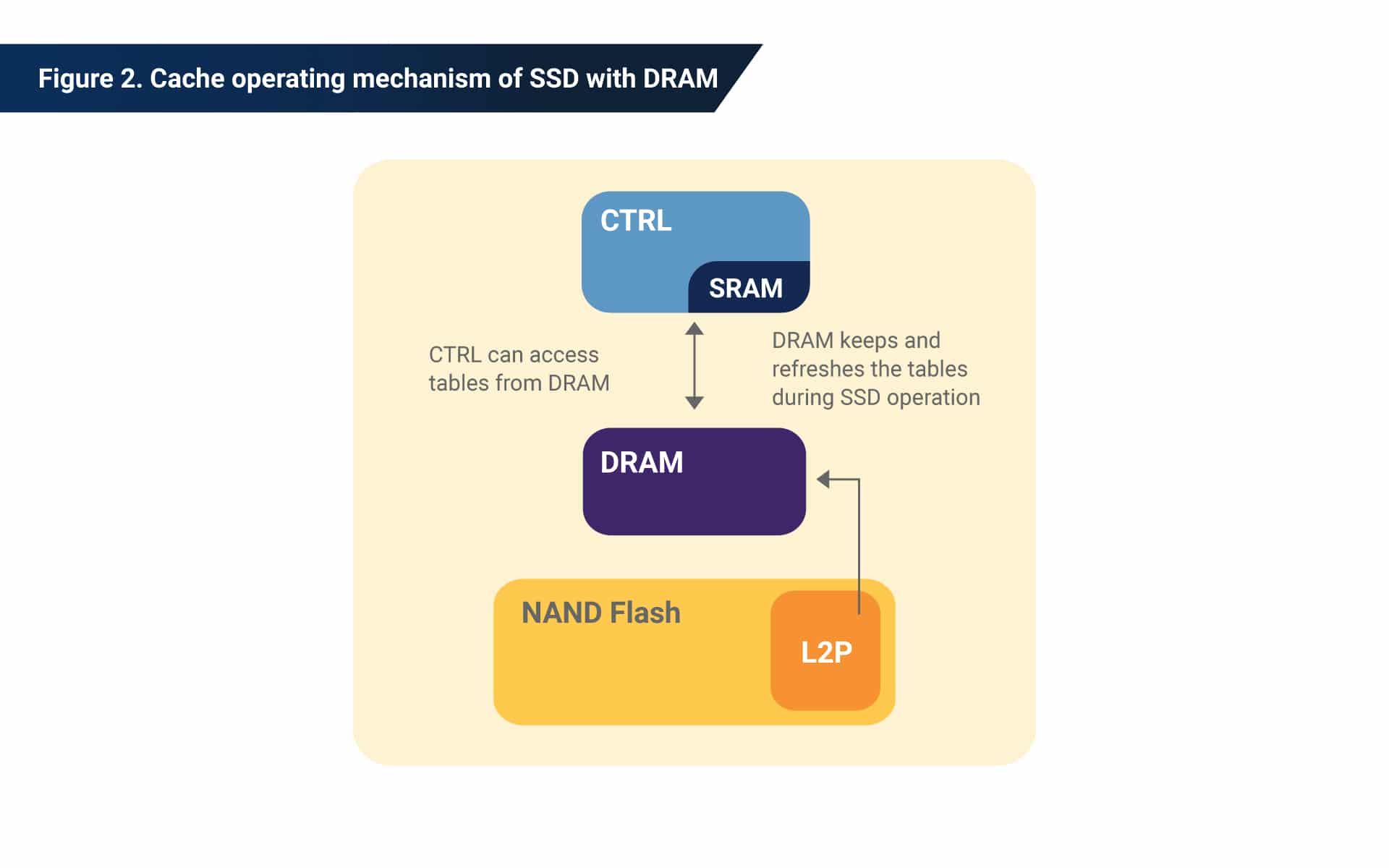

缓存到 DRAM 或从 DRAM 检索的最重要信息是将逻辑地址转换为 NAND 闪存阵列中存储数据的物理位置的映射信息。此信息存储在称为 L2P(逻辑到物理)表的映射表中,并随着 SSD 将数据移入和移出闪存存储而频繁更新。在关机期间,L2P 表存储在闪存中,因为如果没有连续供电,DRAM 很快就会变得无法运行。

另一方面,在上电情况下,L2P表会上传到DRAM,以便控制器不断更新。 DRAM 尺寸越大,可供控制器使用的可用空间就越多。这通常意味着更灵活的数据放置,从而在接收命令时有更好的反应时间。就典型数据工作负载而言,需要所谓“随机读取”序列的操作从充足的 DRAM 空间中获益最多。

然而,与闪存相比,DRAM 等宝贵资源的成本很高。控制密度后,目前 DRAM 的价格是 NAND 闪存平均价格的 10 倍以上,而且没有迹象表明这种情况会很快改变。

尽管 DRAM 具有诸多优势,但过去十年出现了不安装 DRAM 的 SSD。这些“无 DRAM”驱动器具有成本更低、物理尺寸更小的优势。

但无 DRAM 的 SSD 也不完全是“一刀切”的解决方案。由于为中间数据和映射表保留的缓存空间固有的缺陷,无 DRAM 的 SSD 的性能通常会受到影响。

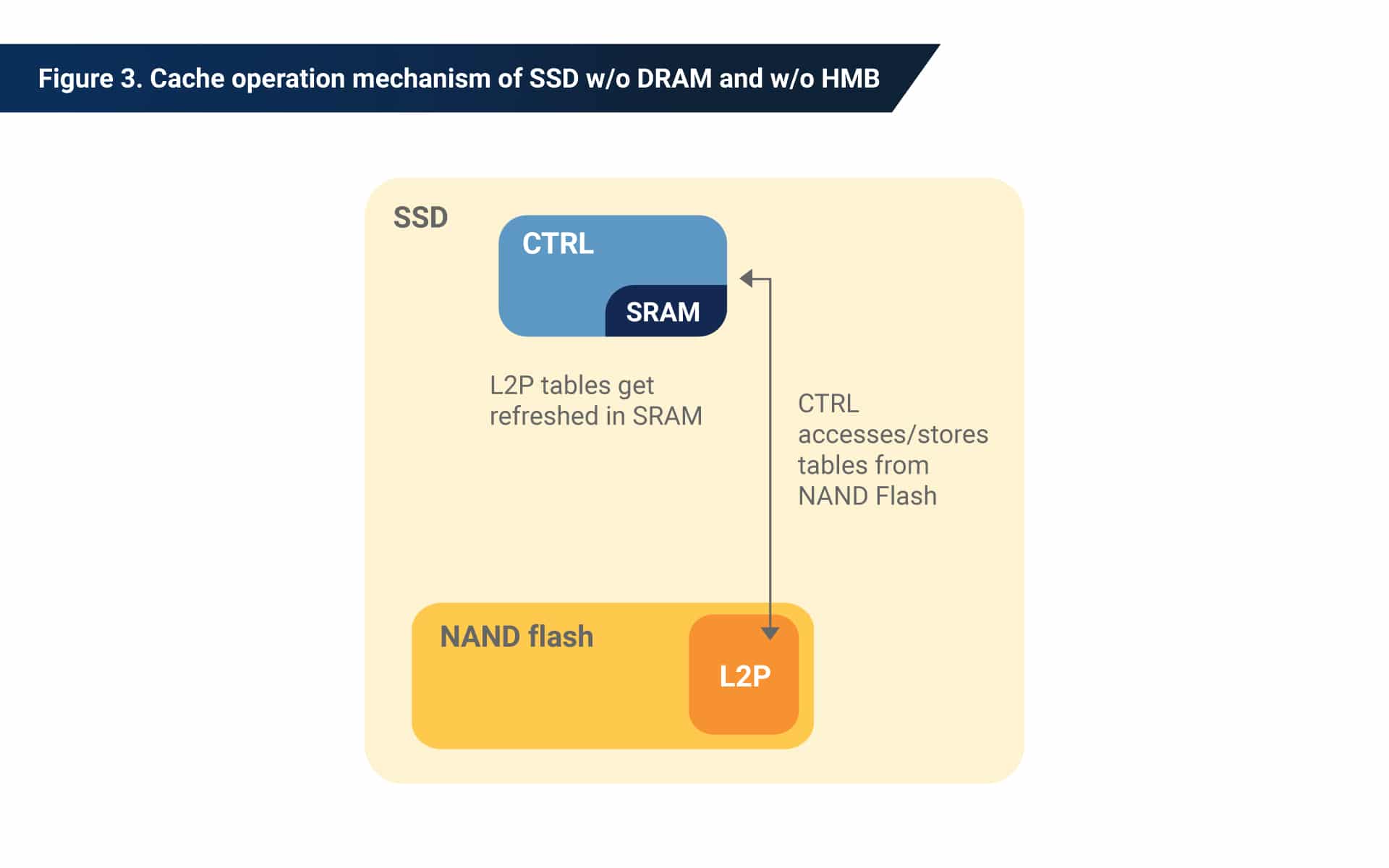

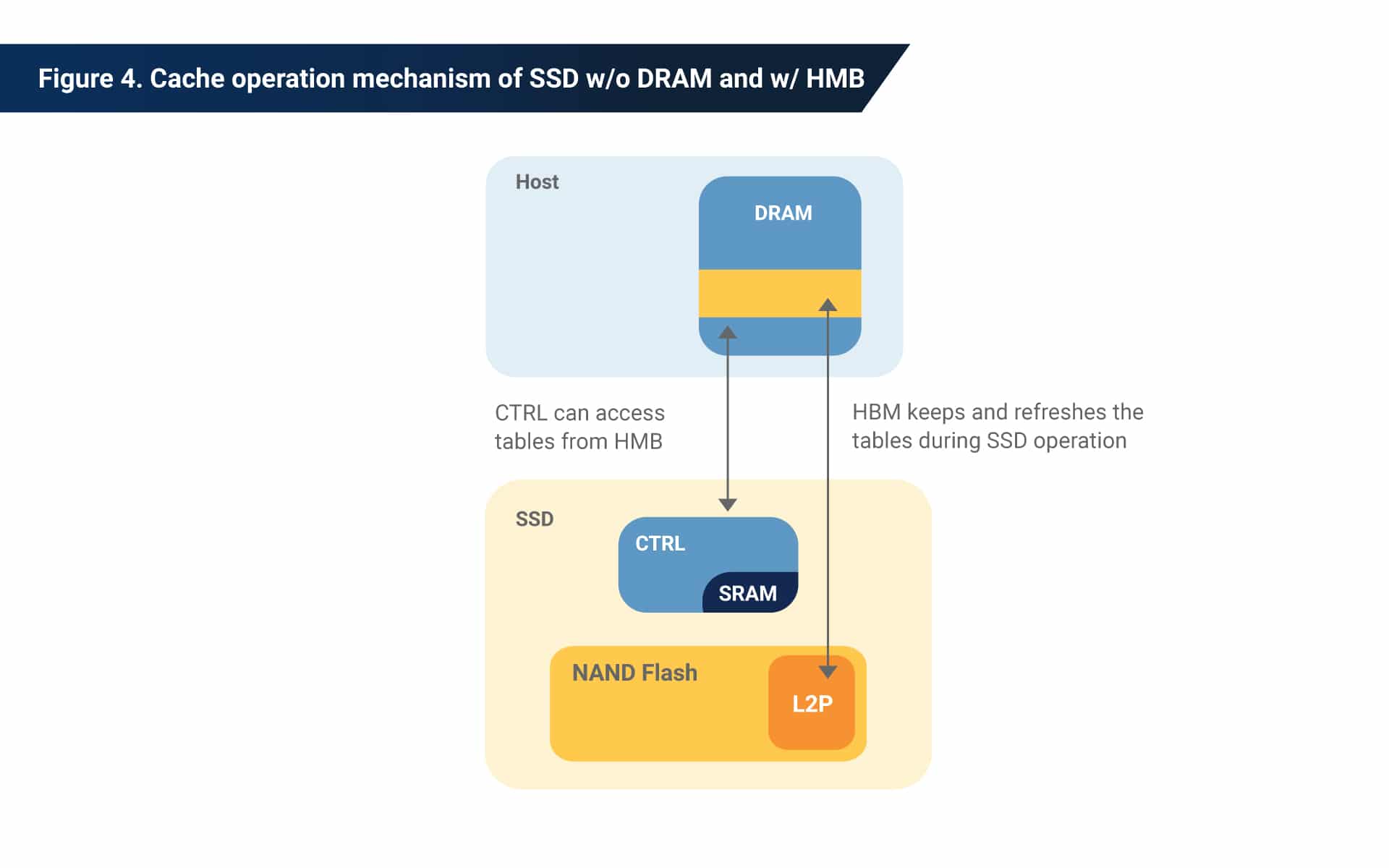

尽管无 DRAM 设计也将 L2P 表保留在 NAND 存储器中,但它们与安装 DRAM 的设计有重要区别。当控制器尝试从 NAND 闪存访问这些表时,信息会在更新和使用时加载到控制器的内部 SRAM(静态 RAM)中。之后,这些表又被放入NAND闪存中进行存储。

这里的主要区别是使用 SRAM 作为缓存空间。然而,SRAM 是一种宝贵的高性能资源,其成本甚至比 DRAM 更高。此外,典型的闪存控制器通常只有几兆字节的 SRAM。由于更大的缓冲区空间通常会带来更高的效率,因此从性能角度来看,这些无 DRAM 的设计可能被认为是次优的。

这个缺点正是 HMB 功能被设计的原因。在SSD操作期间,L2P表可以直接从NAND闪存加载到HMB。这些表可以从主机端连续刷新在缓冲存储器中,几乎与传统的 DRAM 方法相同。

启用 HMB 的 SSD 在处理随机工作负载的效率方面通常会显着减少甚至可能不会降低。在下一节中,我们将探讨一些有关 HMB 性能的具体实际测试数据。

HMB 性能改进:使用与不使用

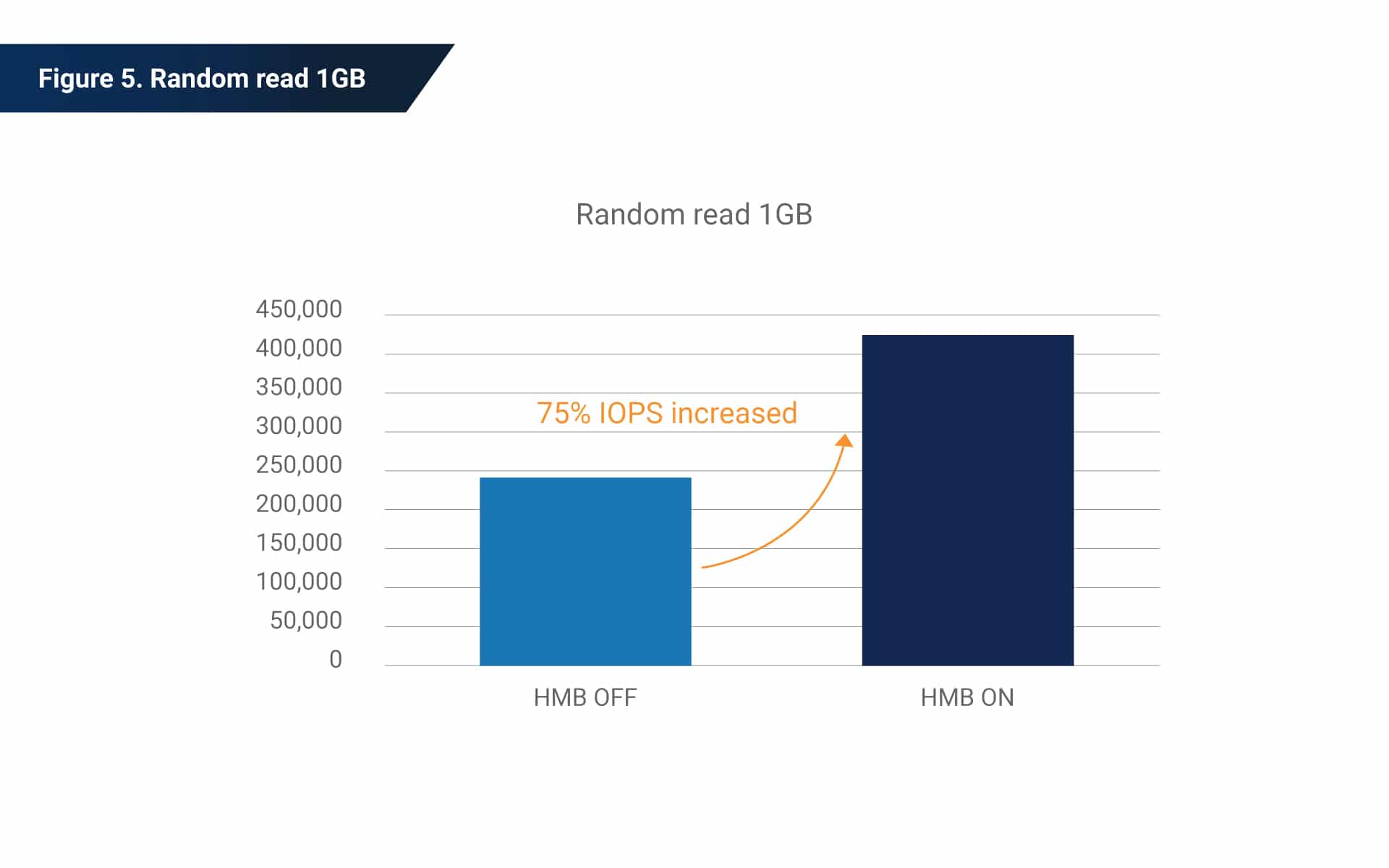

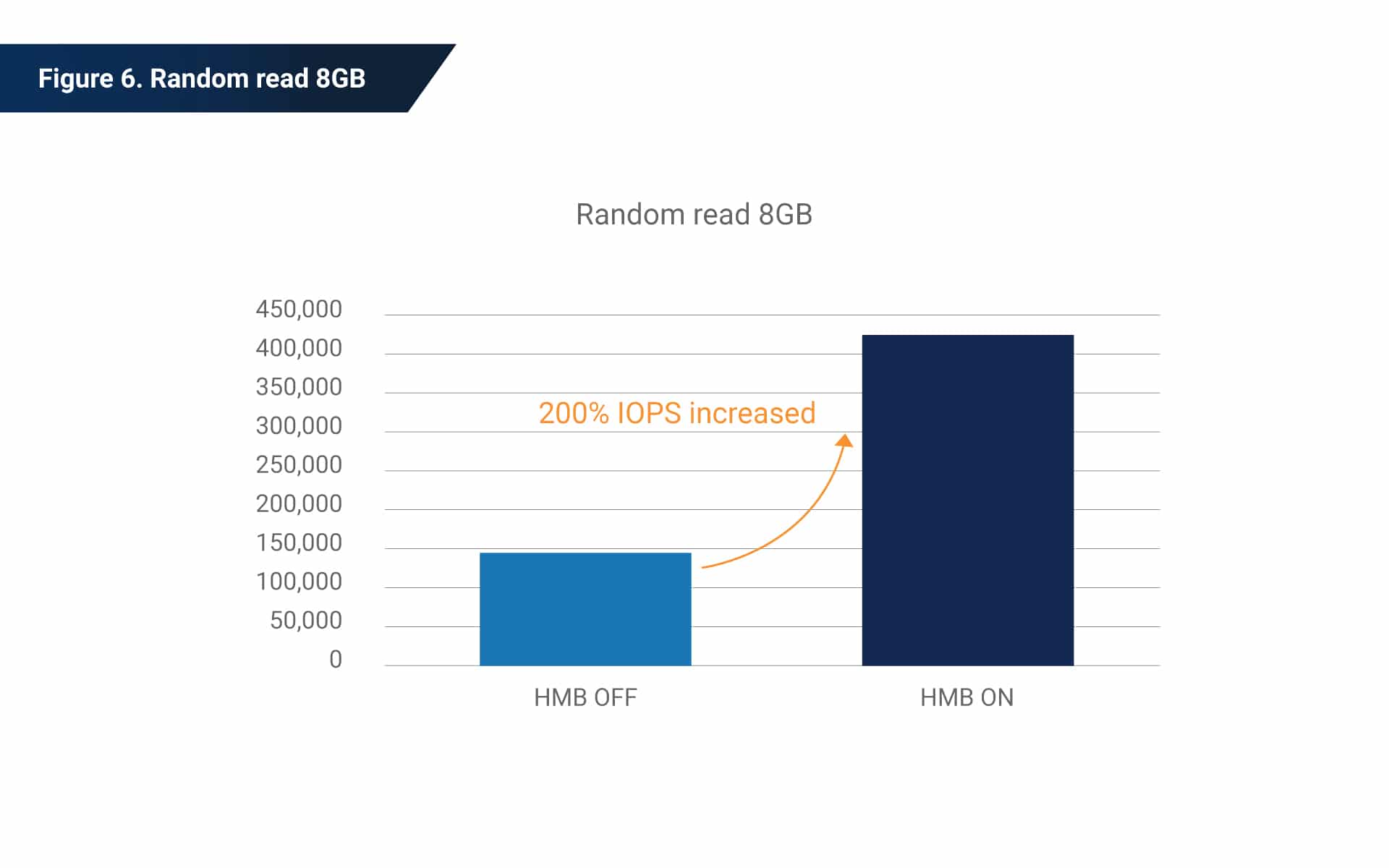

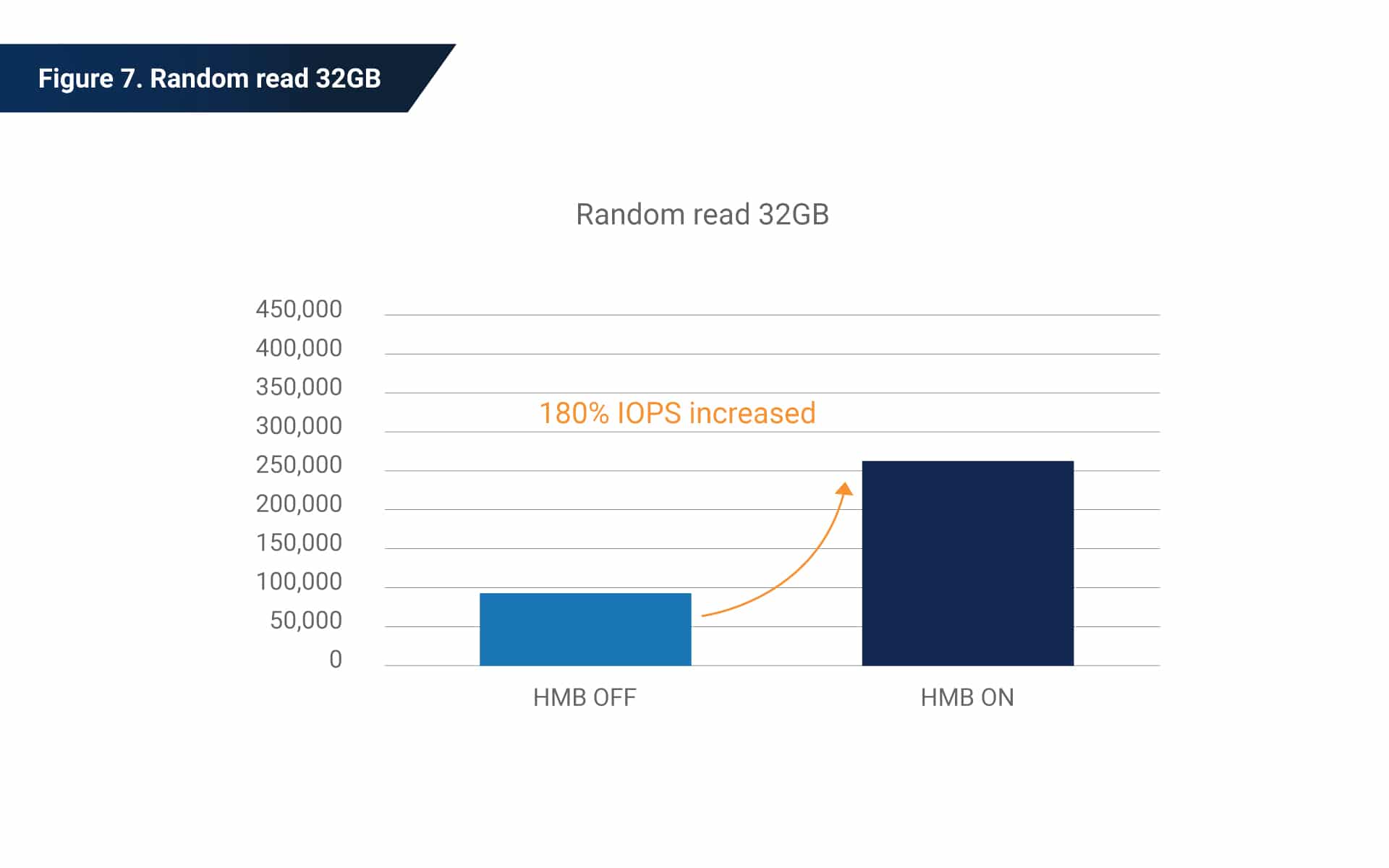

启用 HMB 后,SSD 通常会在所谓的“随机读取”中看到性能提升。这些操作是指通过控制器级操作根据主机请求检索预定大小的数据(但来自闪存内不可预测的位置)。

然而,HMB 性能提升在不同的工作负载下也会有所不同。这是因为主机可能并不总是能够提供闪存控制器所需的实际内部存储器空间量。

这些图表展示了使用 HMB 带来的非线性性能提升,将工作负载从处理 1 GB 的数据扩展到 32 GB。这是由于 HMB 的 DRAM 容量限制。

当我们处理 L2P 表并处理大量中间数据时,我们达到了一个阈值,在该阈值中,对所提供的 HMB 空间的加载操作开始呈指数增长。因此,32 GB 数据的 IOPS(每秒输入/输出操作数)的增加不如 8 GB 数据显着。这表明,HMB 与任何硬件技术一样,其性能提升也有限。

然而,即使有 32 GB,使用 HMB 时我们仍然可以获得超过 100,000 次额外的 IOPS。这显然是一个显着的提升——即使是煞费苦心的固件优化也只能得到几千 IOPS 的回报。

群联如何使用 HMB 打造世界上最好的 SSD

自首次发布以来,无 DRAM 的 SSD 已作为供应商所谓的“价值线”的一部分得到了广泛部署,由于其硬件配置而提供了成本效率优势。群联已在自己的 SSD 中实施了 HMB,利用我们的硬件和固件专业知识来提高性能,而不会滥用控制器硬件资源。

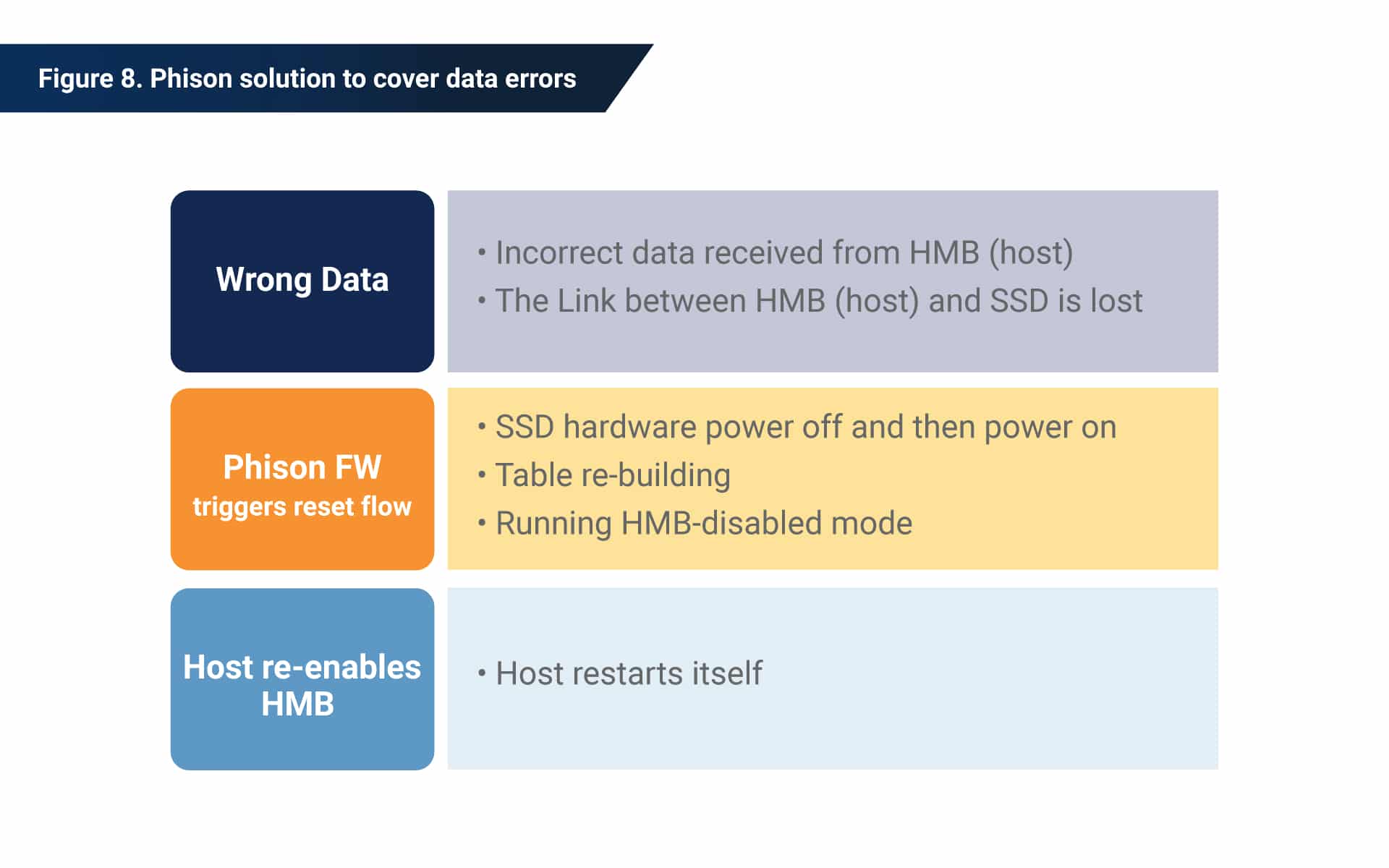

根据 NVMe 协议中的定义,如果在使用 HMB 时意外移除 SSD,闪存控制器必须保证数据丢失或损坏的可能性为零。为了满足这一标准,群联的控制器解决方案使用专有固件,旨在消除数据传输错误并在操作过程中确认数据完整性。

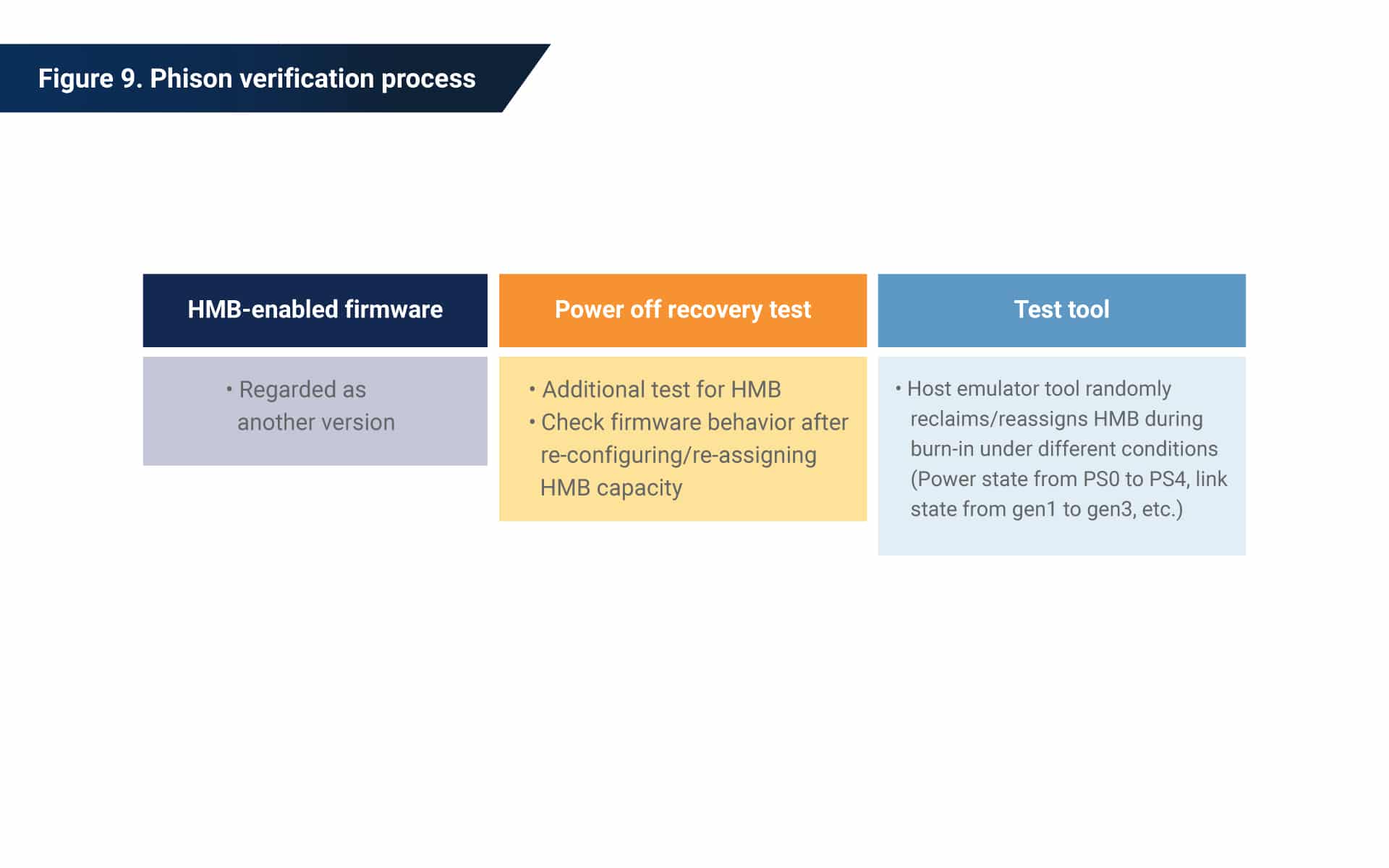

此外,群联利用其丰富的知识和经验来测试和验证其SSD设计。群联进行控制器级和系统级测试,以进行彻底的功能和物理验证。

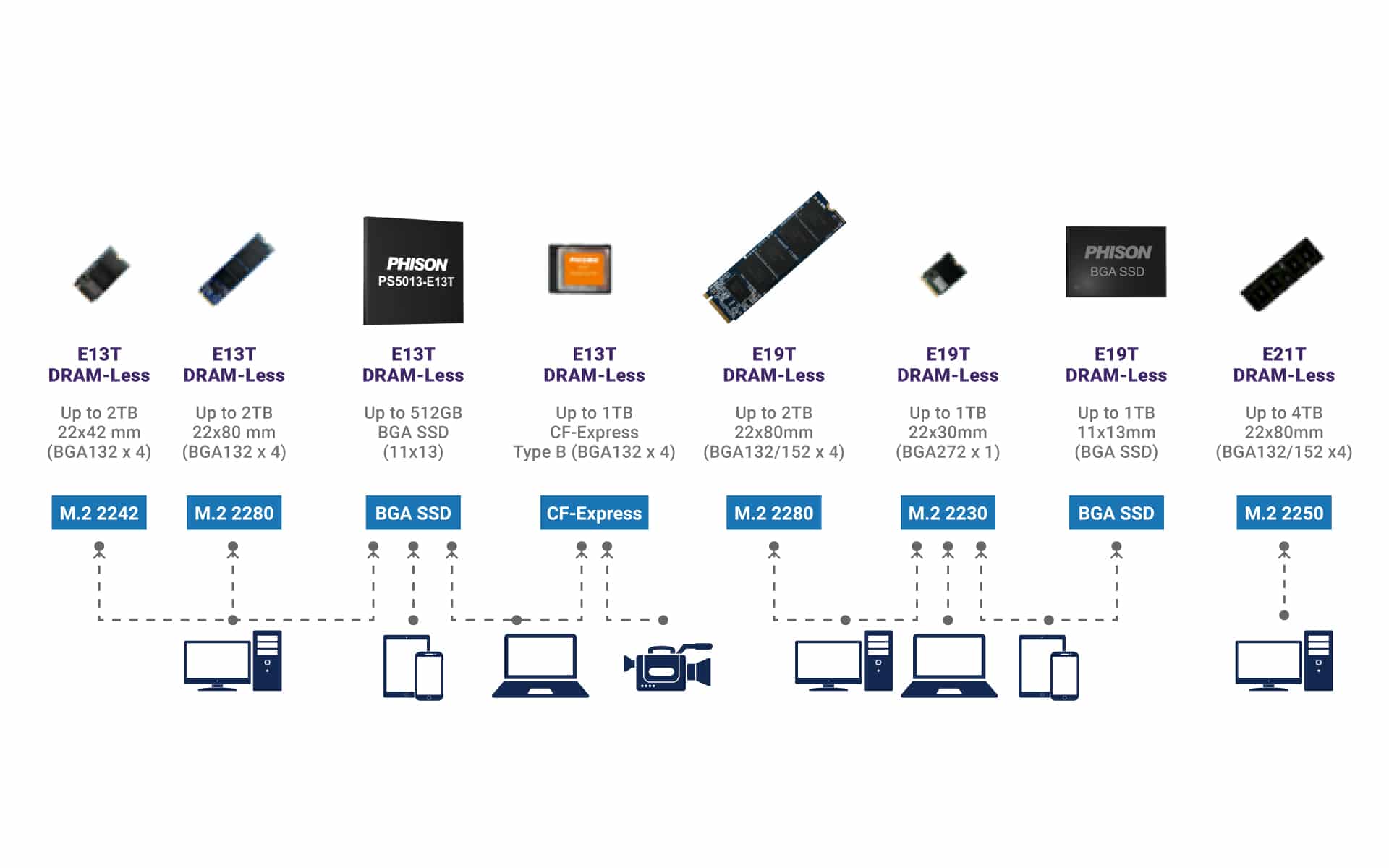

下面的图表显示了群联制造的哪些无 DRAM 产品适合各种行业应用。欲了解更多信息,请访问 群联网络.