NAND 플래시 기술의 개발은 업계의 다양한 입력을 기반으로 꾸준히 발전해 왔습니다. 호스트 장치 솔루션 공급자와 저장 장치 제조업체 간의 협력은 표준화된 인터페이스의 구축을 촉진했으며 오늘날의 생태계까지 공동으로 구축되었습니다.

공개적으로 사용 가능한 두 가지 가장 눈에 띄는 인터페이스 표준은 ONFI(Open NAND Flash Interface) 및 Toggle 표준이며, 각각의 권위 있는 작업 그룹에서 개발하고 지속적으로 확장합니다. 두 표준 간에 대조 및 비교가 가능하지만 잘 알려진 "공통 기반"은 JEDEC(Joint Electron Device Engineering Council)에서 발표한 JESD230 표준으로 개발자가 표준에서 추출하는 참조로 활용할 수 있습니다. 설정합니다.

각 표준 세트의 고유한 개발은 플래시 및 스토리지 업계 리더 그룹의 고유한 범위와 지식에 따라 형성되기 때문에 명령, 주소 지정, 타이밍, 형식 및 물리적 구성의 차이로 분명합니다. 그럼에도 불구하고 두 표준 모두 서로 다른 기술 간의 호환성 및 상호 운용성을 위해 노력하는 응집력을 전달합니다.

레거시 인터페이스

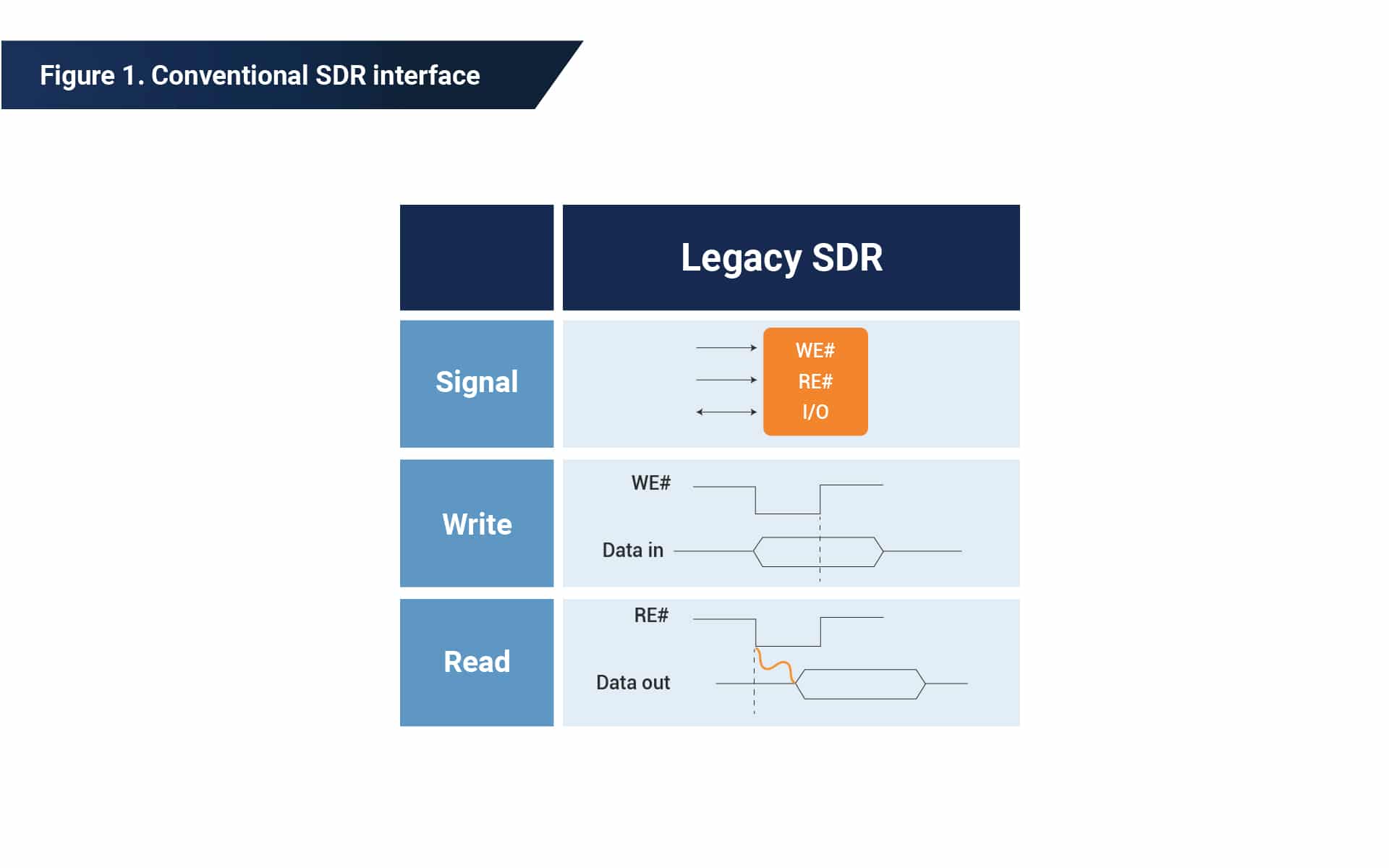

플래시 인터페이스 지식 풀을 조사하면 동기 및 비동기 데이터 전송 체계 간의 비교를 즉시 식별할 수 있습니다. 레거시로 알려진 최초의 NAND 플래시 장치 인터페이스는 데이터 전송을 위한 타이밍 기준과 관련된 비동기 전송 체계를 활용하도록 구성되었습니다. 향상된 신호 무결성 및 정확도를 위해 연속 클록 신호와 동기화해야 하는 신호를 제어하는 데 동기 방식이 사용됩니다. 비동기 방식을 사용하면 전송 작업의 트리거링이 클록 없이 "WE(Write-Enable)" 및 "RE(Read-Enable)" 제어 신호에 전적으로 의존할 수 있습니다.

또한 Legacy는 SDR(Single Data Rate)에서 데이터 전송을 지원하여 제어 신호의 한쪽 에지에서만 데이터 전송을 처리합니다. 특히 인터페이스는 데이터가 장치 안팎으로 "이동"할 때 쓰기 신호의 상승 에지와 읽기 신호의 하강 에지에서만 공식화된 신호 정렬을 시행합니다.

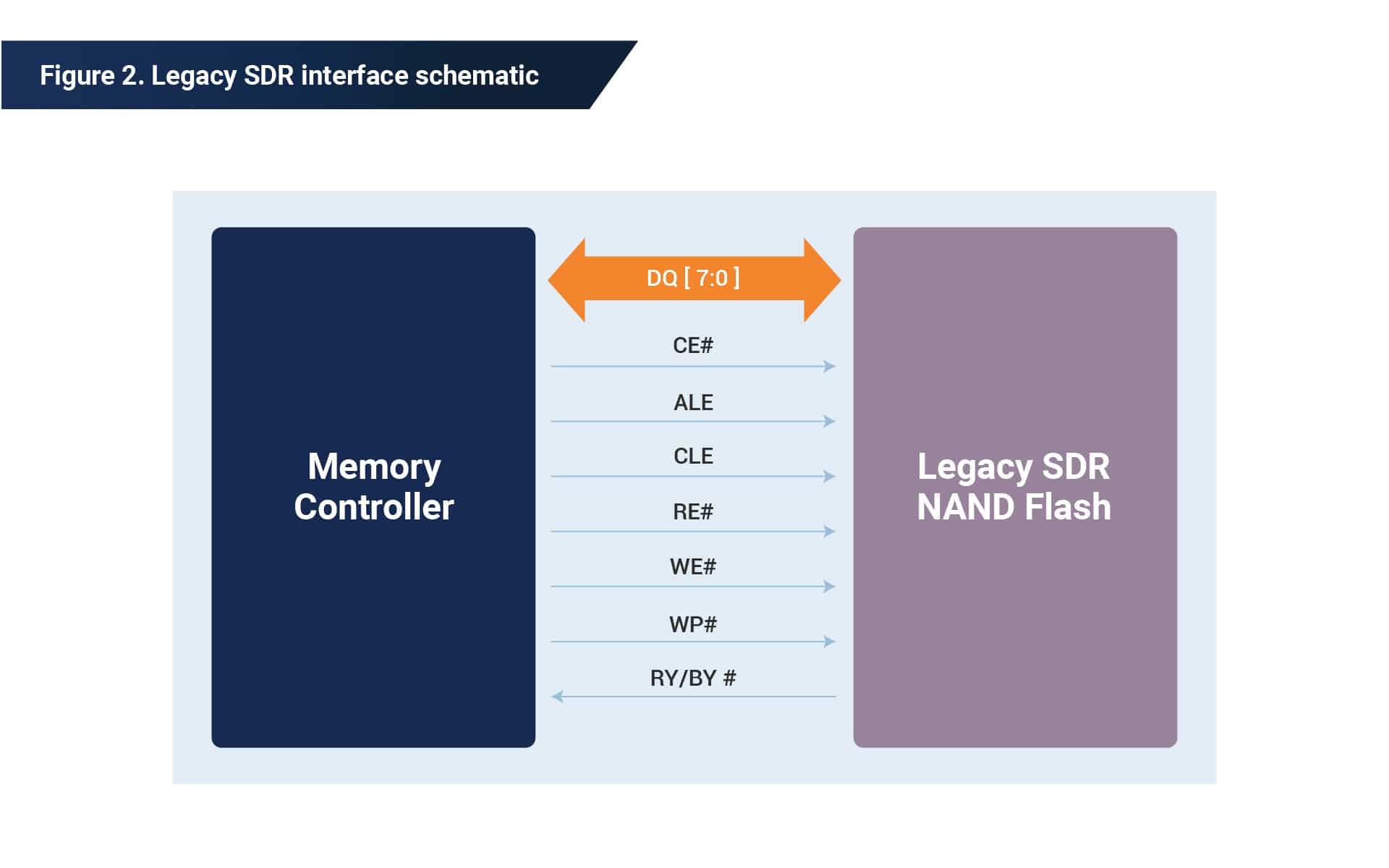

I/O 신호(DQ)를 위한 8비트(b) 양방향 데이터 버스 외에 7개의 제어 신호 핀이 있는 15핀 인터페이스는 25나노초(ns)의 전송 시간 내에 바이트(B) 전달을 수행합니다. ). 이 특성을 기반으로 최대 대역폭은 데이터 핀당 40MB/s 또는 40Mb/s로 계산할 수 있습니다. (1B/25ns = 0.04×109B/s = 40MB/s, 1B = 8b)

ONFI 인터페이스

2006년 SK 하이닉스, 인텔, 마이크론, 샌디스크, 파이손, 소니 등을 포함한 대규모 기술 회사 그룹이 ONFI(Open NAND Flash Interface) 워킹 그룹을 구성했습니다. 그해 말, 플래시 시장의 무질서한 특성(스토리지 제품, 플래시 공급업체 및 다운스트림 간의 플래시 인터페이스에 대한 일관성 없는 기준에서 비롯됨)에 대응하여 통합된 표준을 제공하는 것을 목표로 하는 ONFI 표준의 첫 번째 버전이 초안 및 출시되었습니다. 제품 제조업체).

다면적 ONFI 표준은 기능 특성화, 기능/명령 세트 조절, 신호 설명/타이밍 조건, 동작 흐름 및 레지스터 수준/물리적 사양을 포함하되 이에 국한되지 않는 시장이 절실히 필요로 하는 적절한 인터페이스의 중요한 측면을 설명했습니다. 오늘날 ONFI Workgroup은 2021년 현재 ONFI 5.0의 가장 최근 초안과 함께 표준 집합에서 확장하기 위한 업데이트를 계속 릴리스하고 있습니다.

온피 1.0

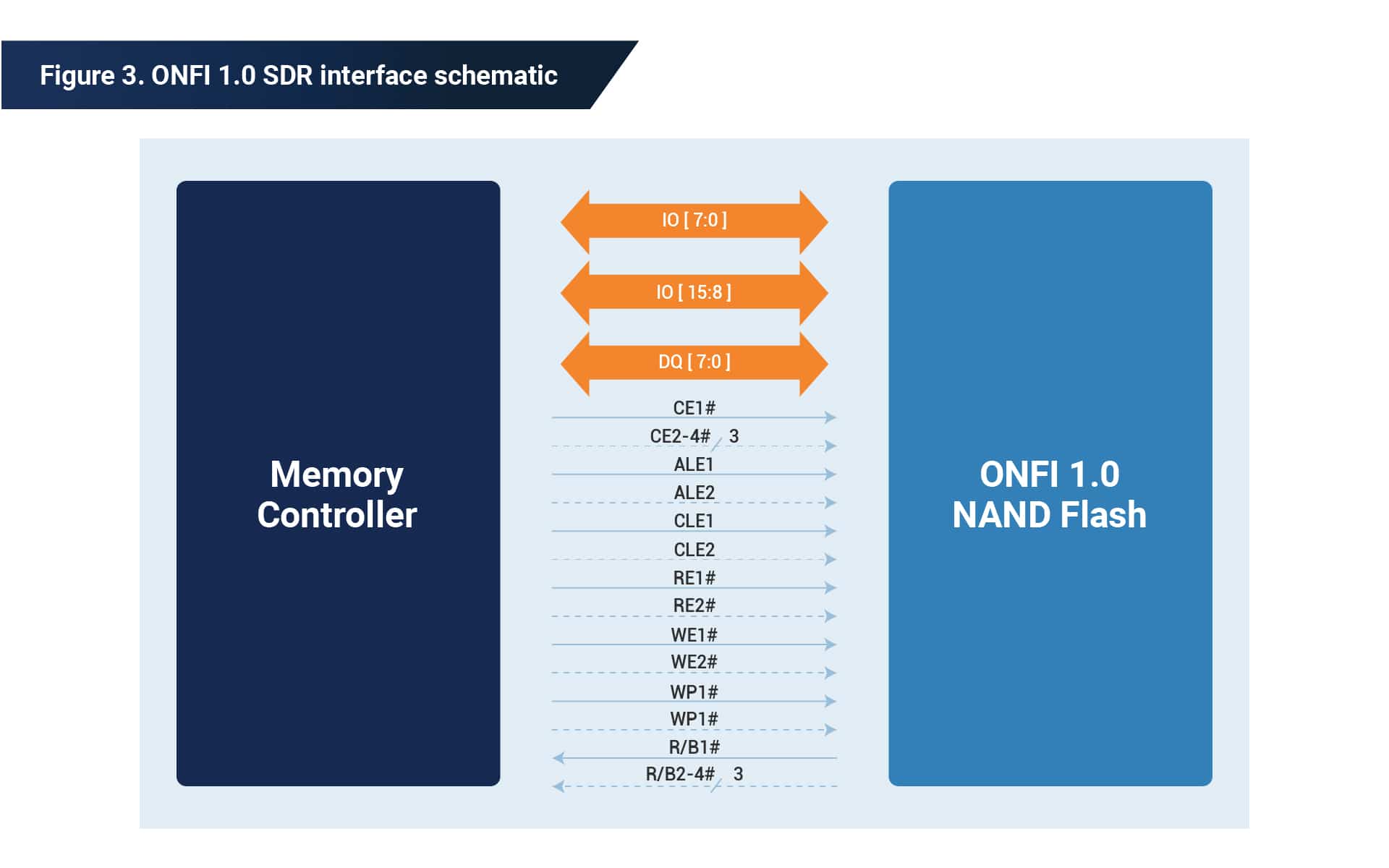

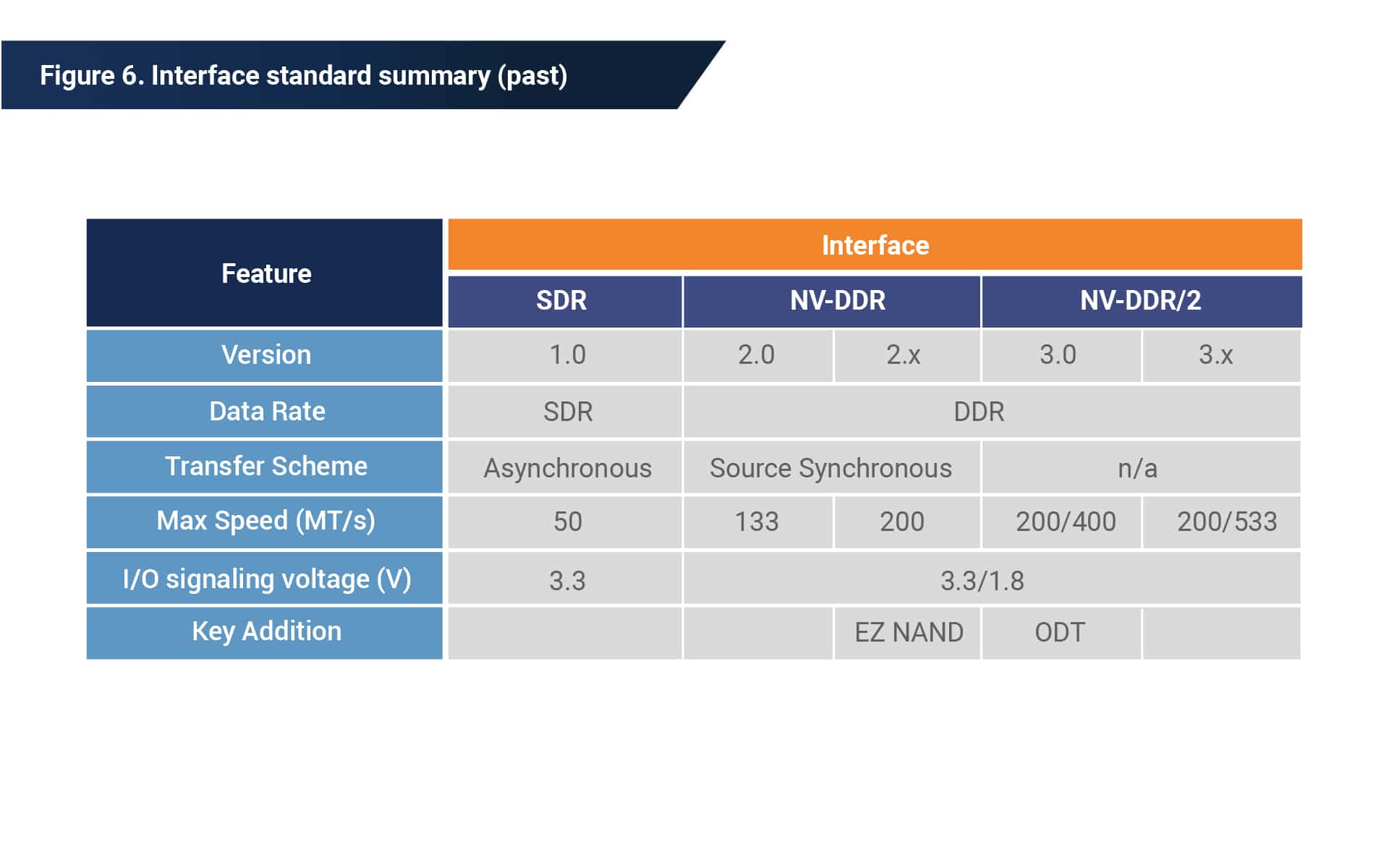

첫 번째 릴리스의 주요 목적은 레거시에서 확장된 신속한 인터페이스 표준화를 제공하는 것이었습니다. 비동기 SDR 전송 체계를 사용하는 동안 버전 1.0은 기존 레거시와 유사하지만 제어 신호 업스케일링이 있는 16비트 데이터 버스와 같은 첨단 기술을 선택적으로 지원하는 전기 인터페이스를 설명했습니다. 50MB/s의 대역폭은 Legacy의 이전 40MB/s 성능보다 향상된 20%를 나타냅니다.

온피 2.0

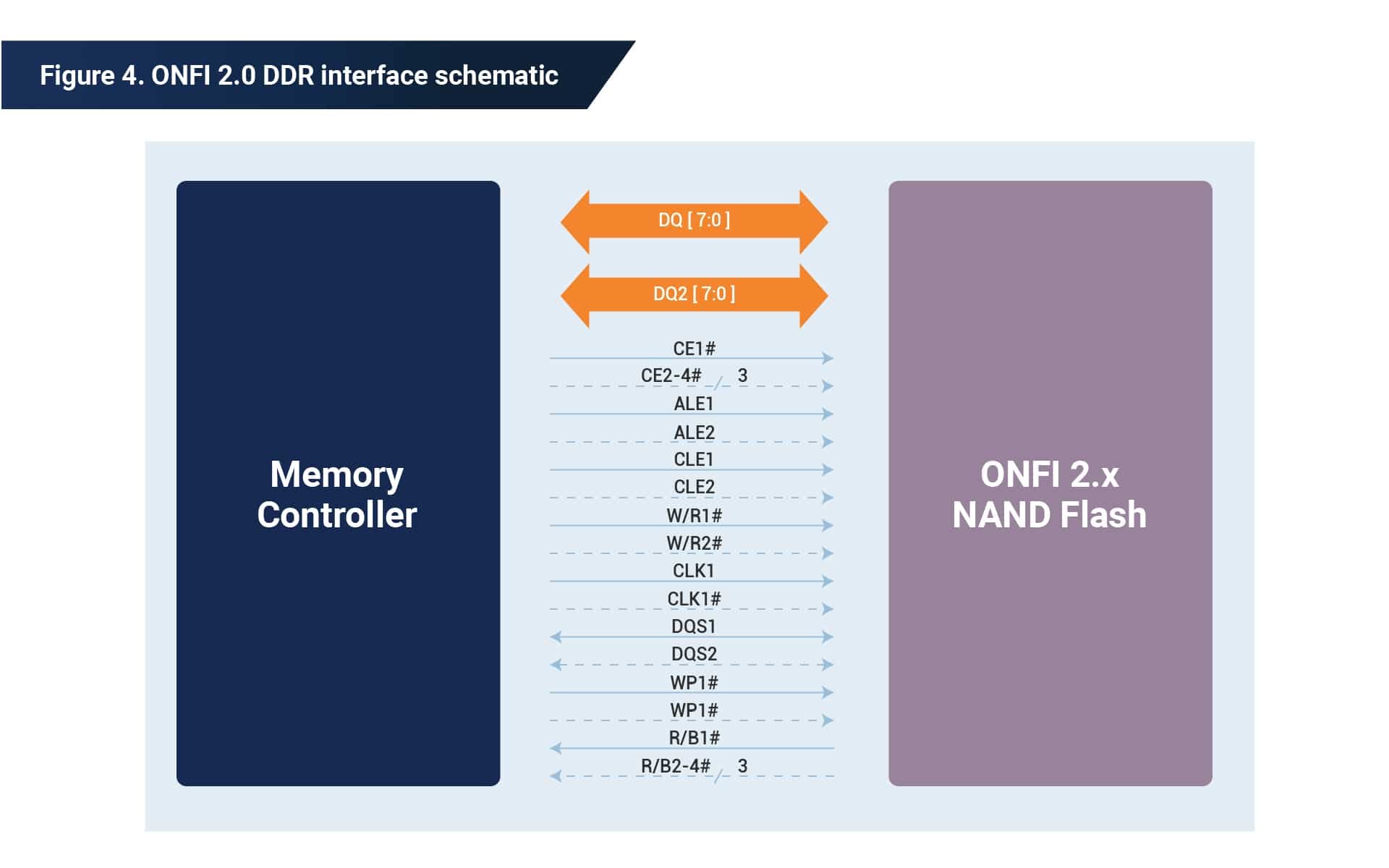

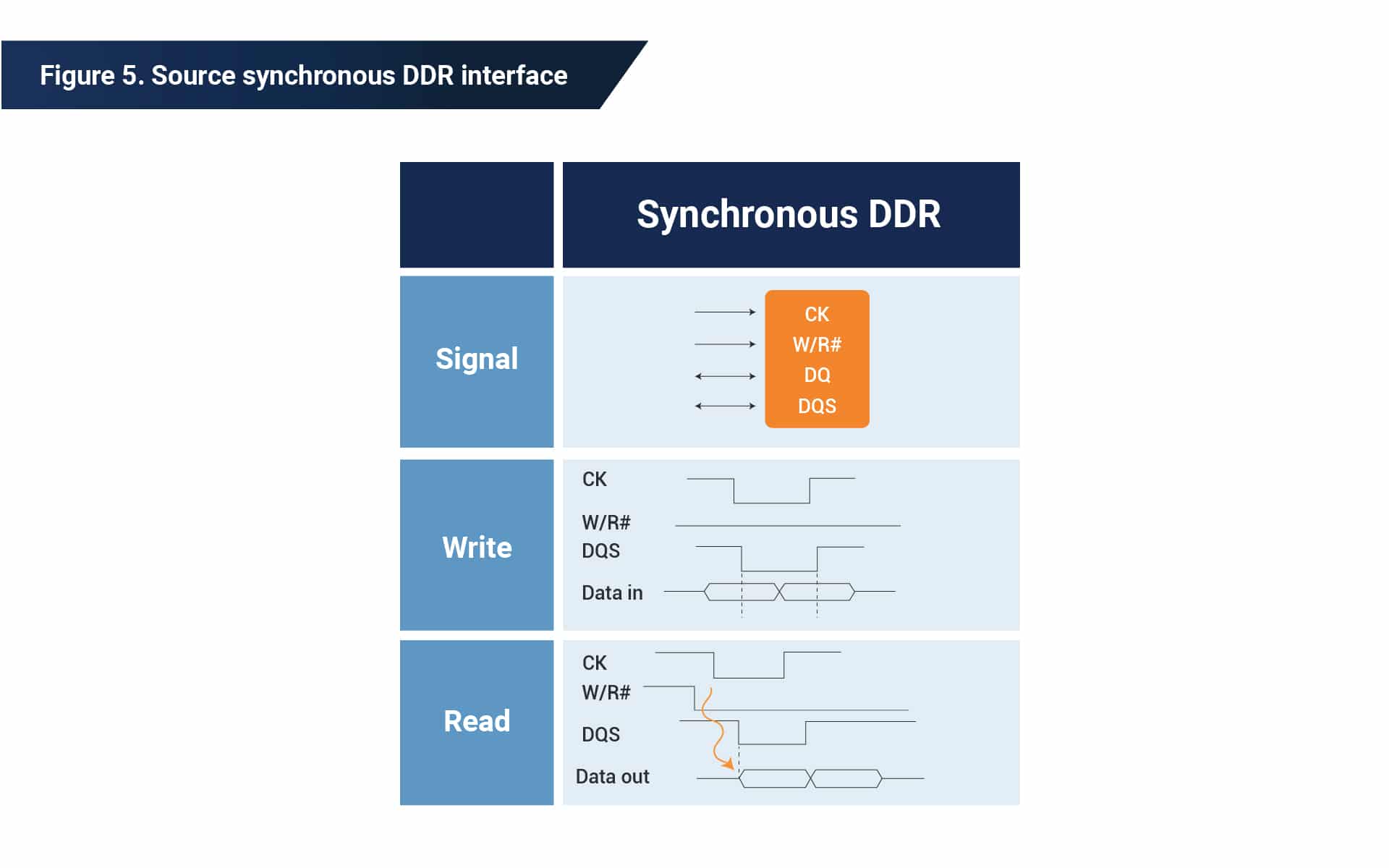

ONFI 2.0은 2008년 2월에 출시되었습니다. 가장 중요한 변화는 제어 신호의 양쪽 에지에서 데이터 전송을 허용함으로써 장치 최대 처리량을 크게 증가시킬 수 있는 DDR(Double Data Rate) 전송 체계를 채택한 것입니다. 또한 ONFI 표준은 이 사양 내에서 DDR 플래시 인터페이스를 NV-DDR(Non-Volatile DDR) 인터페이스로 수정하여 RAM(Random Access Memory)에서 사용하는 휘발성 메모리 DDR 인터페이스와 구별할 수 있도록 했습니다.

NV-DDR은 이전 SDR 개정판과의 호환성을 위해 비동기 작업 방식을 유지했지만 소스 동기 방식을 지원하도록 조정되었습니다. 구체적으로, 이전의 WE 제어 신호는 클록 신호(CLK)가 되고, RE 제어 신호는 판독 동작과 기록 동작을 선택하는 방향 신호가 된다. 또한 새로 추가된 데이터 스트로브 신호(DQS)의 상승 및 하강 에지 모두에서 데이터가 전송되어 최대 133MT/s까지 두 배의 전송 속도를 달성했습니다. 증가된 처리량은 더 큰 크기의 데이터 전송 및 임의 성능 향상에 대한 추세를 즉시 해결했습니다.

온피 2.1

ONFI 2.1은 2009년에 2.0 개정판의 여러 섹션을 확장하여 비준되었습니다. 2.1 표준은 운영 유연성을 위한 공간을 제공하는 새로운 기능 외에도 최대 전송 속도를 200MT/s로 업그레이드할 수 있습니다.

오류 수정 코딩(ECC) 기능을 보고하는 확장된 매개변수 페이지부터 시작하여 ONFI 사양 내의 여러 섹션이 확장되었습니다. 개정판 2.1의 주요 추가 사항으로, 확장된 ECC 정보는 ECC 매개변수와 다른 장치 매개변수(예: 유효한 블록 수 및 지원되는 프로그램/지우기 주기 수)의 지정된 페어링에서 NAND 장치에 대한 여러 가지 유효한 사용 방법을 허용했습니다.

메모리 구성으로 이동하면 인터리브 주소 지정 및 논리 단위 번호(LUN)의 도입으로 패키지 핀, 특히 칩 인에이블 핀이 줄어들고 복잡한 하드웨어 설계의 중복성이 감소할 뿐만 아니라 엔지니어링 기회가 열렸습니다.

장치 제어 명령으로 "Small Data Move" 및 "Change Row Address"가 도입되었습니다. "Small Data Move" 명령은 장치 제어 명령에서 축소된 데이터 청크로 로우엔드 소비자 애플리케이션에 대한 ECC 제한을 해결했습니다. "행 주소 변경" 명령은 장치 작동 유연성을 높여 워크로드 오버헤드를 줄이기 위한 것입니다.

온피 2.2

이전 개정판의 변경 사항을 기반으로 하는 ONFI 2.2는 메모리 구성에 대한 추가 지침과 함께 2009년 말에 출시되었습니다. 이전에 도입된 인터리브 주소 지정에 대한 제한이 명시되었으며 개별 LUN에 대한 재설정 명령이 추가되었습니다. 개정판은 또한 사양의 부록 내에 현재 측정 방법론을 정의했습니다.

온피 2.3

ONFI 2.3은 2010년 8월 FMS(Flash Memory Summit)에서 EZ-NAND(ECC Zero NAND) 프로토콜에 중점을 두고 출시되었습니다. 프로토콜은 ECC 관리 장치를 스토리지 컨트롤러 측에서 플래시 측으로 이동하여 부담이 큰 제어 장치의 압력을 완화할 것을 권고했습니다.

ONFI 3.x

ONFI 3.0은 2011년 3월에 최대 400MT/s의 지원 전송 속도로 야심차게 도약하면서 발표되었으며, 이는 당시 선호되는 8K 페이지 데이터 정렬 크기 증가 추세에 적합합니다. 처리량 업그레이드는 또한 전력 소비 최적화를 위한 단계로 신호 전압을 1.8V로 줄였습니다.

플래시 혁신의 한계를 높이기 위해 다른 많은 새로운 기능이 도입되었습니다. ODT(On-Die-Termination)는 컨트롤러가 패키지 내 독립 장치 또는 모든 장치에 대한 종단 저항을 켜고 끌 수 있도록 하여 메모리 채널의 신호 무결성을 개선한 설계로 이 사양 개정판에서 더 영향력 있는 추가로 길을 안내했습니다. . ODT와 같은 다중 다이 패키지 기능은 섬세한 다이 레벨 작업 및 동작을 제어하기 위해 이 개정판에서 자세히 다루었습니다.

다른 기능으로는 볼륨 주소 지정 향상과 필요한 칩 인에이블 핀 수가 감소하여 회로 라우팅 효율성이 향상되었습니다. 그러나 리비전 3.2가 출시되면서 NV-DDR2 인터페이스에서 533MT/s 처리량이 가능해지면서 전송 속도 업그레이드가 다시 주목을 받았습니다. 당시 동일한 세대의 장치 내에서 플래시 업그레이드가 합법화되었습니다.

온피 4.0

ONFI 4.0 사양은 이전에 알려진 NV-DDR2에 의해 667MT/s로, 새로 도입된 NV-DDR3에 의해 800MT/s로 업그레이드된 전송 속도와 함께 2012년에 도착했습니다. 종단 저항을 보정하기 위한 ODT 촉진 도구로 ZQ 보정이라고 하는 기술이 도입되었습니다. 이 사양은 전압 또는 온도 변화의 경우 신호 무결성의 손상을 제한했습니다. 또한 이러한 개선 사항을 통해 I/O 전력(VCCQ) 요구 사항을 1.2볼트까지 낮추어 전력 소비를 개선할 수 있었습니다.

온피 4.x

버전 4.0에서 확장된 ONFI 사양에는 전력 구성 유연성, 보조 기능 매개변수 정의, 추가 물리적 핀 할당 옵션을 포함하여 몇 가지 변경 사항이 있습니다.

ONFI 4.1부터 코어 제어 전압(VCC)에 대한 옵션이 2.5V로 열렸고 2.35V에서 3.6V까지 구성 범위가 원래 3.3/1.8/1.2 설정에 추가되었습니다.

DCC(Duty Cycle Correction) 및 DQ 읽기/쓰기 교육이 초기화 프로세스 중에 NAND 장치 조정을 용이하게 하는 기능으로 ZQ 보정 위에 추가되었습니다. 이 변경 사항은 특히 워크로드가 많은 800MT/s 이상에서 작동하는 장치를 대상으로 합니다. DCC 교육은 "Read Enable Complement" 신호("Read Enable" 신호에 대한 보완 신호)의 잠재적 듀티 사이클 불일치를 보상하기 위한 것입니다. 그만큼

DQ 교육은 DQS 및 DQ 신호를 호스트 측 시스템에 맞추려는 시도였습니다.

4.2 개정에서는 DCC 교육 사양의 세부 사항이 수정되었으며 물리적 핀 할당 옵션에서 다른 변경 사항이 발생했습니다. 특히 252볼 BGA(Ball-Grid-Array) 할당이 물리적 인터페이스를 위한 새로운 옵션으로 이전 BGA-272 및 BGA-316 할당에 합류했습니다.

온피 5.0

ONFI 5.0의 출시는 2021년 초에 이루어졌습니다. 새로 출시된 표준 사양에는 적절한 채택을 위해 필요한 변경 사항에 대한 지침과 함께 세 가지 추가 핀 할당 옵션이 공개되었습니다. 그러나 더 중요한 것은 NV-LPDDR4 인터페이스로, 각 인터페이스의 전송 속도를 높이면서 전체 전력 소비를 낮추는 데 중점을 두었습니다. 즉, NV-DDR2의 경우 800MT/s, NV-DDR3 및 NV-LPDDR4의 경우 최대 2400MT/s입니다. 증가된 전송 속도를 감안하여 NV-LPDDR4를 지원하는 장치는 데이터 버스 반전(DBI) 기능을 활용하여 신호 방향과 전류 흐름의 양을 제어하여 전력 소비를 제한할 수 있습니다.

한편, NV-LPDDR4의 출시는 ODT의 기능 수정에 대한 또 다른 추진을 촉발했습니다. ODT 비활성화/활성화 및 채널 ODT와 같은 추가 기능은 새로운 NV-LPDDR4 인터페이스에서 지속되는 ODT의 잠재적인 영향을 해결했습니다.

NV-LPDDR4를 활성화하면 NAND 장치와 컨트롤러 사이의 내부 기준 전압이 훈련되지 않은 상태로 남을 수 있지만 ODT로 인한 작은 신호 스윙으로 인해 명령 시퀀스가 실패할 수 있습니다. 따라서 적절한 시간에 ODT를 비활성화/활성화하면 새 인터페이스에서 작업에 상당한 영향을 미칠 수 있습니다.

이 스위치와 같은 기능 외에도 채널 ODT 설정은 온-NAND 출력 풀업 저항 강도와 신호 종단 저항에 대한 제어 권한을 부여합니다. 즉, 이 설정은 기본적으로 호스트 측에서 데이터 출력 작업 중에 각 채널 내에서 최적의 ODT 강도를 결정할 수 있도록 합니다. 동시에 NAND 장치는 공급업체별 설정 값에 따라 적절하게 조정됩니다.

토글 인터페이스

ONFI 1.0 출시 직후, 세계 최고의 NAND 플래시 제조업체인 Samsung Semiconductors와 Toshiba Memory Corporation(TMC)은 레거시 기능을 넘어서는 드라이브 플래시 장치 작업의 대안으로 Toggle 인터페이스 표준을 도입했습니다. Toggle 인터페이스를 사용하는 장치는 또한 다양한 하드웨어 구성, 신호 패턴 및 전기적 특성에서 확장 가능하고 세심하게 짜여진 지침 세트에서 작동합니다. Toggle 표준의 발전은 대중이 아닌 삼성 및 TMC의 NAND 장치 사양의 고객별 릴리스 내에서 발생했습니다. 이것은 작업 그룹의 통합 공개 릴리스를 기반으로 업데이트된 ONFI 표준과 대조되는 것입니다.

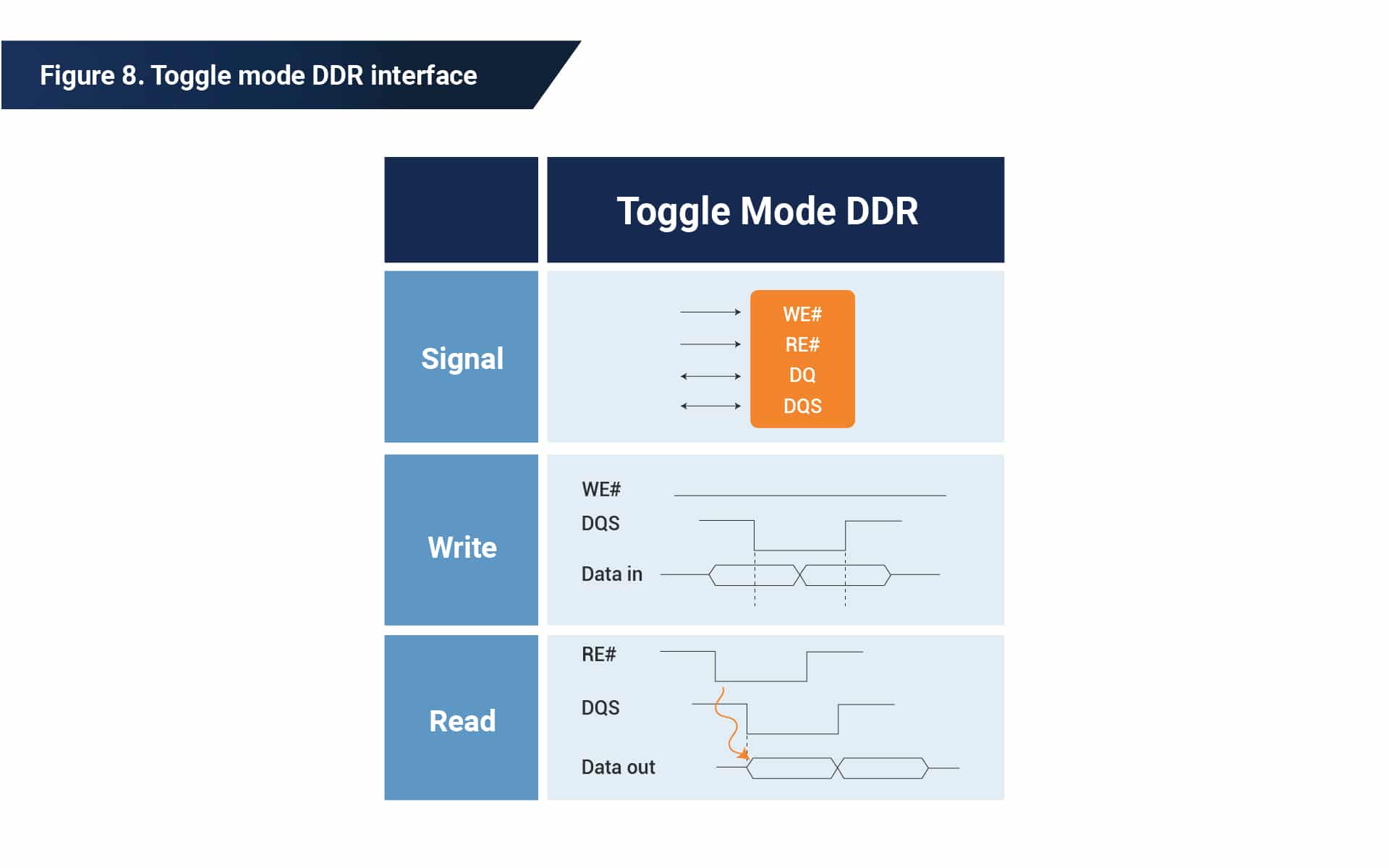

1.0 전환

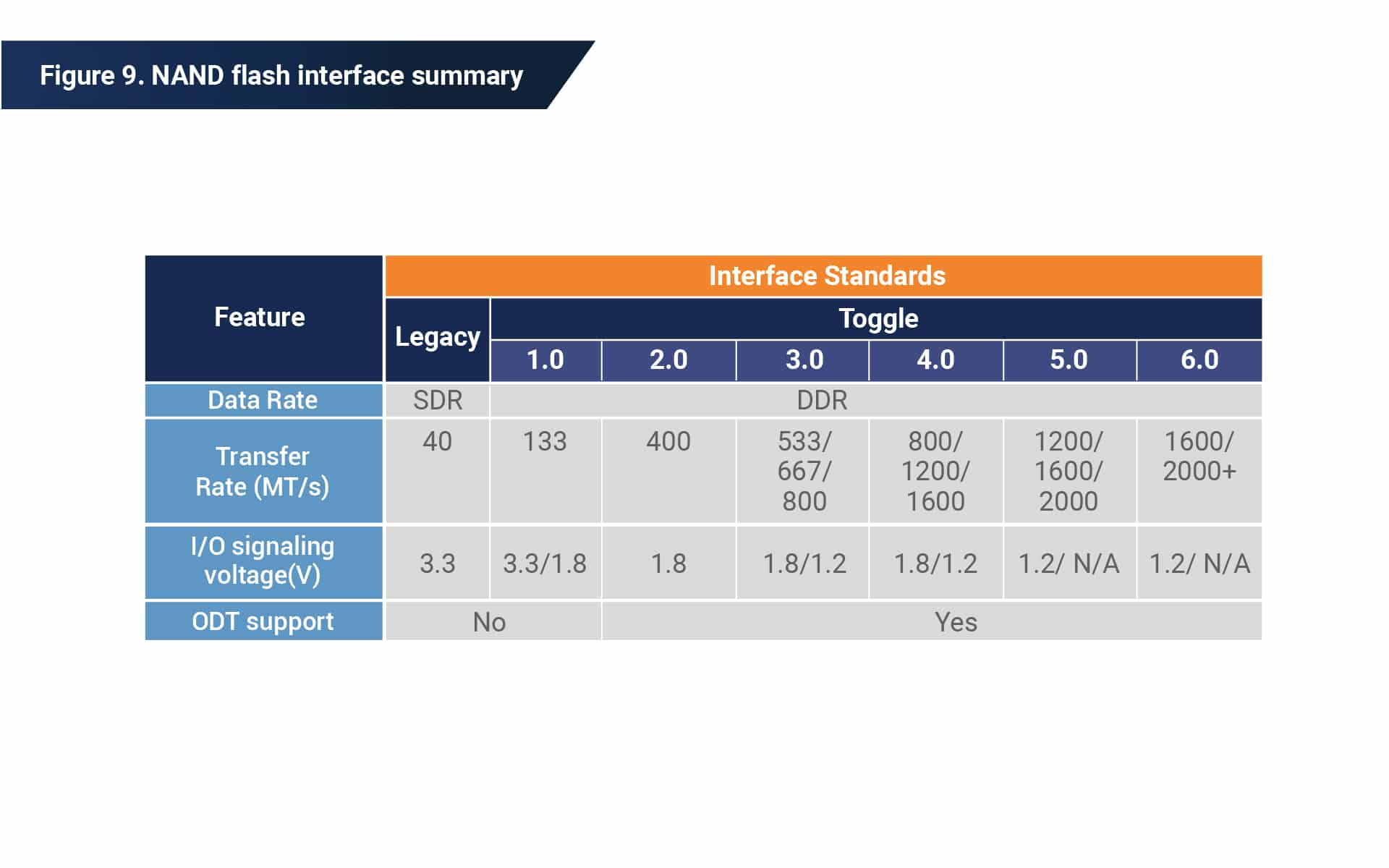

첫 번째 모습부터 1세대 Toggle DDR 인터페이스는 ONFI 2.0 개정판과 공통된 일반적인 특성을 가지고 있었습니다. 토글 1.0은 양방향 DQS 스트로브 신호를 사용하여 최대 133MT/s의 데이터 전송 속도를 허용하며 각 상승 및 하강 에지는 하나의 데이터 전송과 연결됩니다. 그러나 ONFI와 Toggle의 차이점은 Toggle 데이터 전송은 클록 신호 없이 동작하기 때문에 읽기 및 쓰기 작업 발생 시에만 전력 소비와 비동기화된다는 것입니다. ONFI는 개정판 3.0에서 전력 효율성과 디자인 단순성 측면에서 이러한 구현을 채택했습니다.

2.0 / 3.0 / 4.0 전환

Toggle 2.0에서 지원하는 장치는 최대 400MT/s의 처리량을 허용하여 ONFI 3.0에서 작동하는 장치와 비교할 수 있습니다. 그러나 출시 시기에 따라 ODT 기능을 지원하는 토글 2.0 기기는 일부에 불과했다.

Toggle 3.0 장치는 2015년에 533MT/s 및 667MT/s의 지원되는 전송 속도 옵션과 ODT 및 ZQ 보정 기능의 전체 지원과 함께 출시되었지만 주류 Toggle 표준 개정판은 Toggle 4.0 표준입니다. 초기 릴리스에서 Toggle 4.0 인터페이스는 최대 800MT/s 및 1200MT/s의 전송 속도를 지원하는 동시에 ONFI와 일치하는 필수 기능을 지원하지만 제품에 따라 그림이 다릅니다.

물론 인터페이스 표준은 가장 최신 NAND 플래시 기술, 즉 Kioxia(이전 TMC) 및 Western Digital의 BiCS 시리즈와 삼성 및 SK 하이닉스와 같은 한국 공급업체의 V-NAND 시리즈를 대상으로 설계되었습니다. 사실, 새로운 플래시 디자인과 기술이 출시되면서 플래시 공급업체는 동일한 세대 인터페이스 내에서 반복적인 시행착오를 통해 플래시 동작을 보정하여 전송 속도를 조정할 수 있었습니다. Phison은 플래시 공급업체 파트너와 협력하여 시스템 프런트 엔드 성능이 차세대 상호 연결의 문제에 직면함에 따라 완벽한 타이밍에 제공되는 다양한 설계 개선과 함께 2000MT/s 이상의 전송 속도 돌파구를 확인했습니다.

5.0 / 6.0 전환

개발자들이 플래시 인터페이스에 대한 표준 책의 빌딩 블록을 부지런히 쌓고 있기 때문에 미래는 밝습니다. 3D 플래시 기술이 100층 이상 적층 시대에 공식적으로 진입함에 따라 업계에서는 더욱 빠르고 최첨단 인터페이스 교환 속도로의 전환이 임박한 것으로 보고 있습니다. 곧 Toggle 5.0 및 6.0 인터페이스는 2400MT/s 이상의 전송 속도로 실행되어 다이당 250MB/s 이상으로 변환될 것으로 예상됩니다. 플래시 토폴로지 및 설계 변경 논의가 진행됨에 따라 업계에서는 주류 표준을 발전시키기 위해 더 많은 기능이 추가되고 개선될 것으로 예상합니다.

낸드플래시의 미래

지난 20년 동안 ONFI 및 Toggle NAND 플래시 인터페이스는 번성했으며 NAND 플래시 애플리케이션 개발을 위한 업계 표준으로 인식되었습니다. 2021년 현재 두 표준의 최신 릴리스는 NAND 플래시 성능을 기존 레거시 기능보다 최대 10배 이상 끌어올리는 동시에 더 높은 모듈 용량과 낮은 전력 소비를 가능하게 합니다. 1900개 이상의 전 세계 특허와 20년의 플래시 업계 경험을 보유한 Phison은 두 가지 기본 인터페이스 중 하나에서 모든 애플리케이션의 요구 사항을 해결하기 위해 메모리 컨트롤러 지원을 제공할 준비가 되어 있습니다.