基於業界的大量投入,NAND閃存技術的發展一直在穩步向前發展。主機設備解決方案提供商和存儲設備製造商之間的合作促進了標準化接口的建立,這些接口被遵循並共同構建,直到今天的生態系統。

兩個最著名的公開接口標準是開放式 NAND 閃存接口 (ONFI) 和 Toggle 標準,每個標準均由其各自享有盛譽的工作組開發並不斷擴展。雖然兩個標準之間可以進行對比和比較,但公認的“共同點”是聯合電子器件工程委員會 (JEDEC) 發布的 JESD230 標準,開發人員可以從該標準中提取該標準作為參考套。

每套標準的獨特發展通過命令、尋址、計時、格式化和物理配置方面的差異顯而易見,這是由於閃存和存儲行業領導者群體的不同範圍和知識所形成的。儘管如此,這兩個標準都在努力實現不同技術之間的兼容性和互操作性方面具有凝聚力。

遺留接口

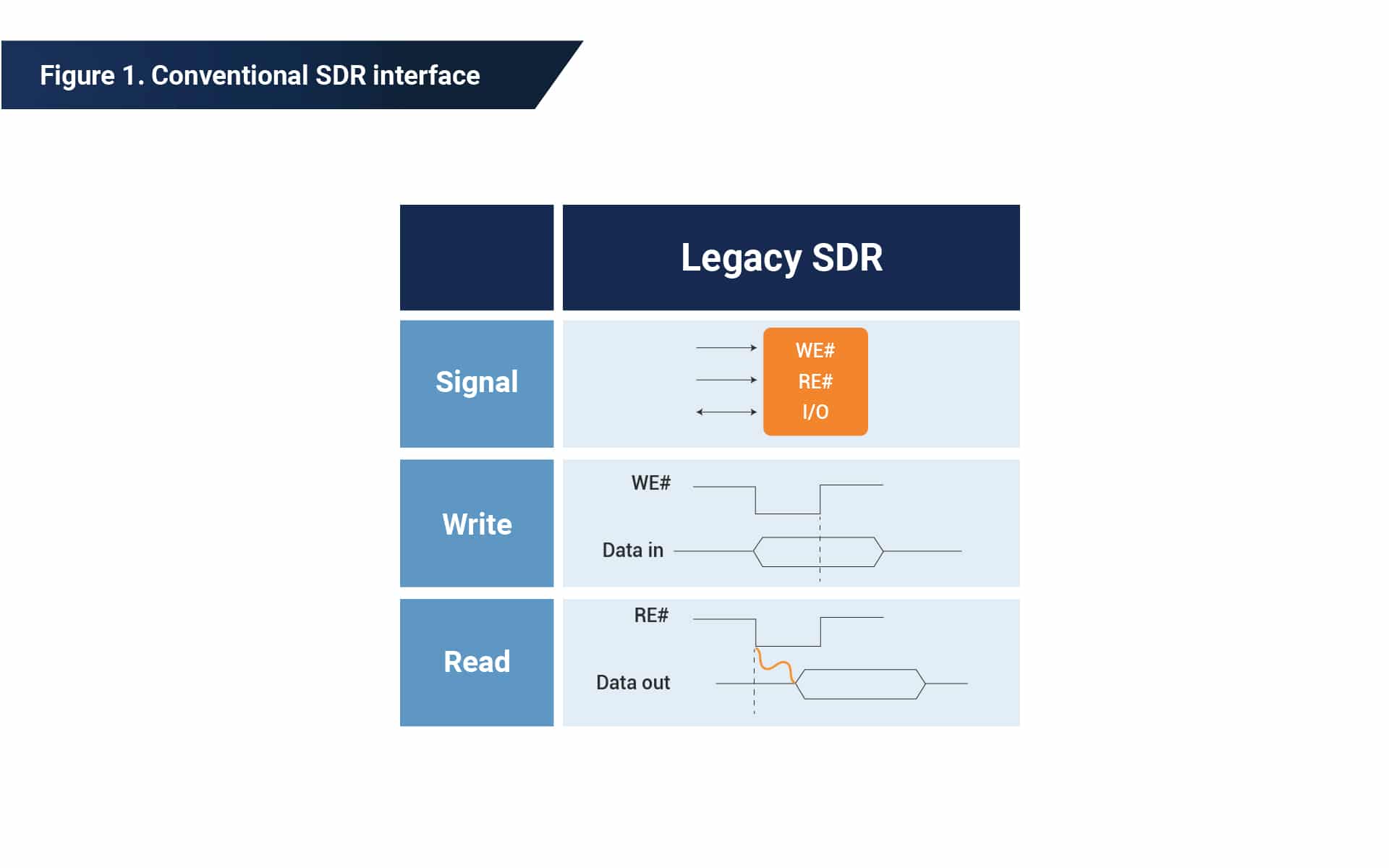

深入研究閃存接口知識庫,您可以立即識別同步和異步數據傳輸方案之間的比較。第一個 NAND 閃存設備接口(稱為 Legacy)被配置為利用與數據傳輸時序標準相關的異步傳輸方案。為了增強信號完整性和準確性,使用同步方案來控制需要與連續時鐘信號同步的信號。異步方案允許傳輸任務的觸發完全依賴於“寫使能(WE)”和“讀使能(RE)”控制信號,而不需要時鐘。

此外,Legacy 支持單數據速率 (SDR) 數據傳輸,僅在控制信號的一個邊沿處理數據傳輸。具體來說,當數據“移入”和移出設備時,該接口僅在寫入信號的上升沿和讀取信號的下降沿強制執行製定的信號對齊。

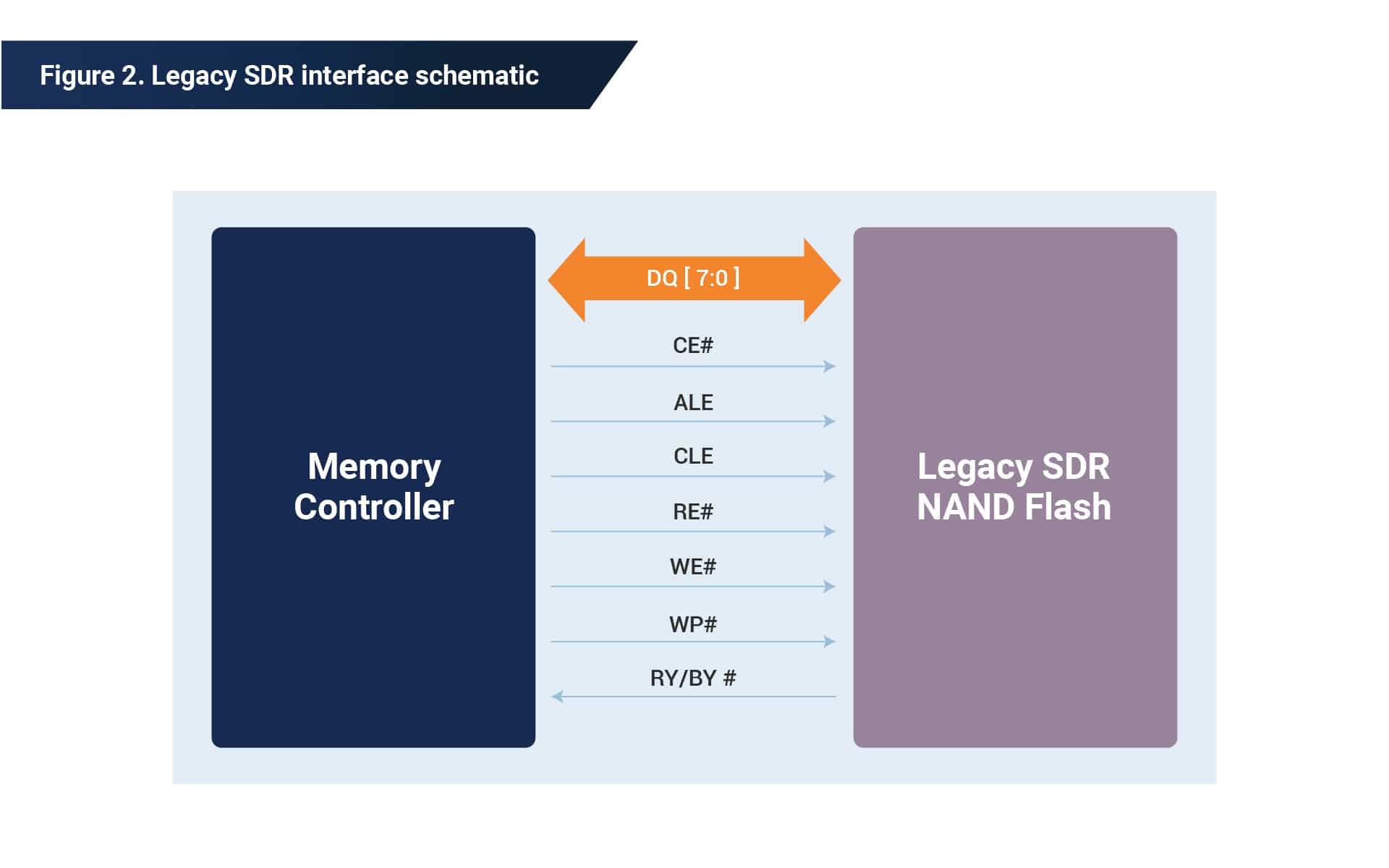

除了用於I/O 信號(DQ) 的8 位(b) 雙向數據總線外,15 引腳接口還具有7 個控制信號引腳,可在25 納秒(ns) 的傳輸時間內完成字節( B) 的傳輸)。基於此屬性,最大帶寬可計算為每個數據引腳 40MB/s 或 40Mb/s。 (1B/25ns = 0.04×109 B/s = 40 MB/s,1B = 8b)

ONFI接口

2006年,一大批科技公司成立了開放式NAND閃存接口(ONFI)工作組,其中包括SK海力士、英特爾、美光、閃迪、群聯、索尼等。同年晚些時候,第一版ONFI標準起草並發布,旨在提供一個統一的標準,以應對閃存市場的無組織性(源於存儲產品、閃存供應商和下游之間閃存接口標準不一致)產品製造商)。

多方面的 ONFI 標準闡明了市場迫切需要的適當接口的關鍵方面,包括但不限於功能特徵、功能/命令集調節、信號描述/時序條件、行為流程以及寄存器級/物理規範。今天,ONFI 工作組繼續發布更新以擴展標準集,最新草案是 2021 年的 ONFI 5.0。

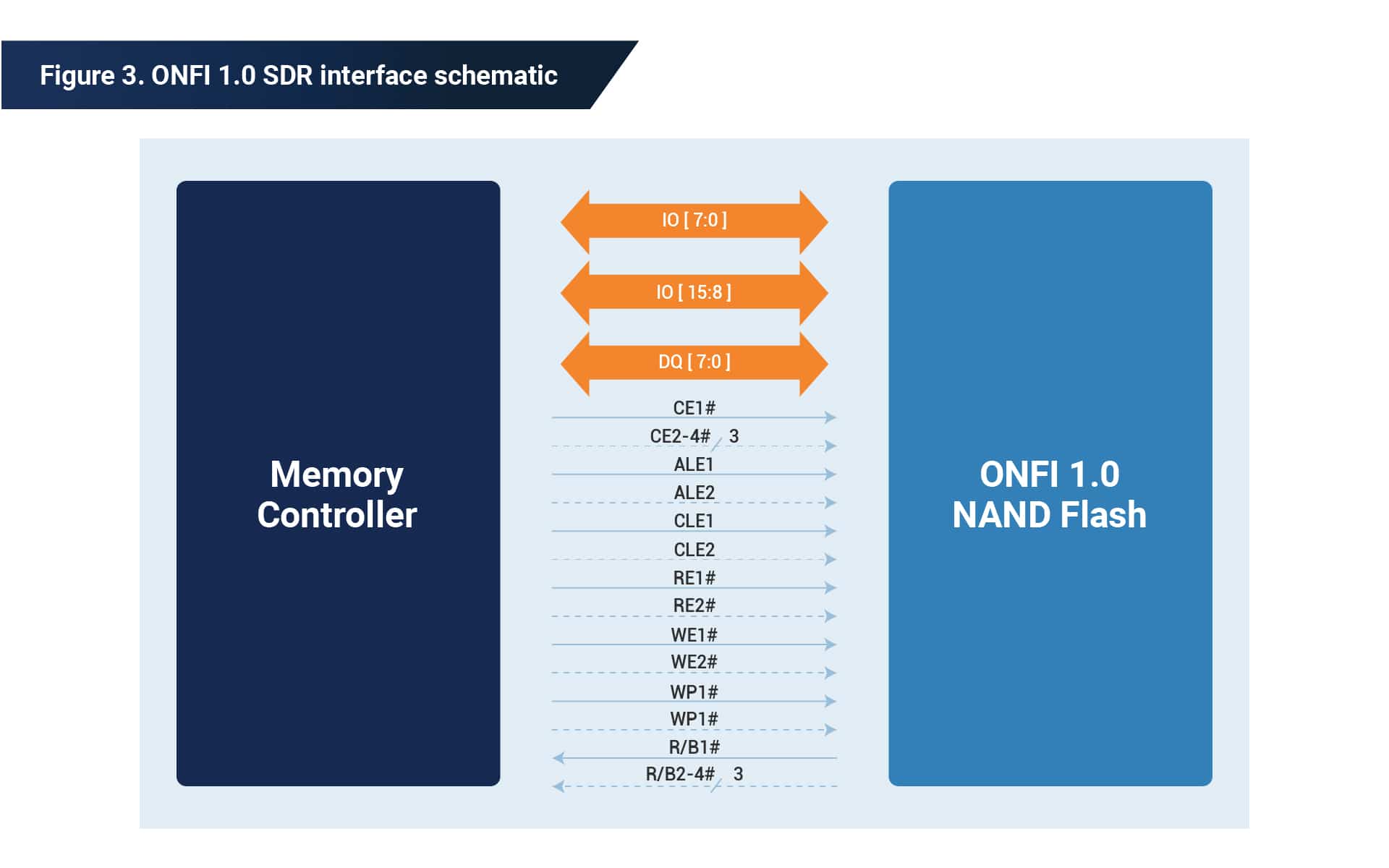

網絡FI 1.0

第一個版本的主要目的是提供從舊版本擴展的快速接口標準化。在採用異步 SDR 傳輸方案的同時,1.0 版本描述了類似於傳統傳統的電氣接口,但可選擇支持尖端技術,例如具有控制信號放大功能的 16 位數據總線。 50MB/s 的帶寬標誌著 20% 比 Legacy 之前的 40MB/s 性能有了改進。

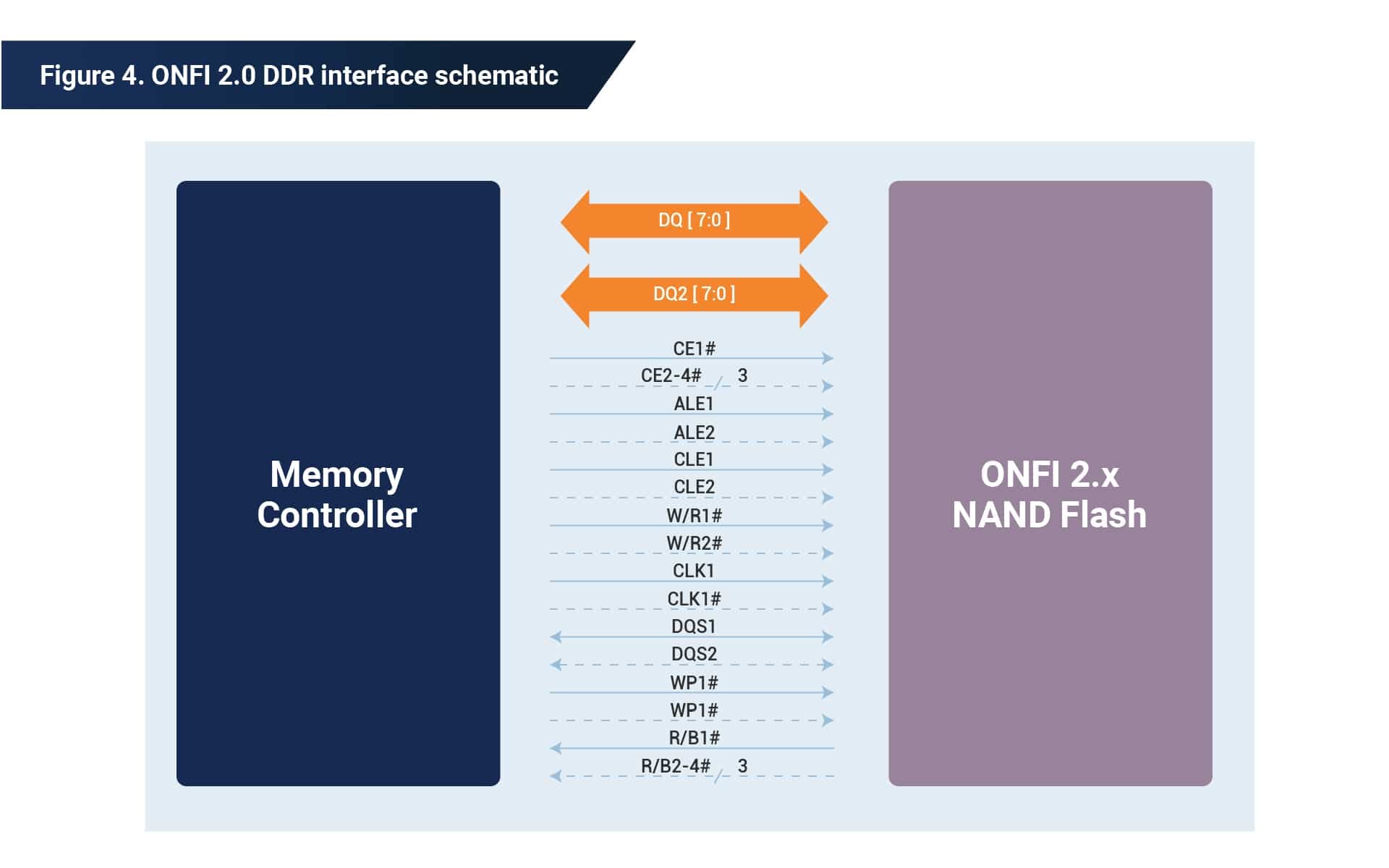

網絡FI 2.0

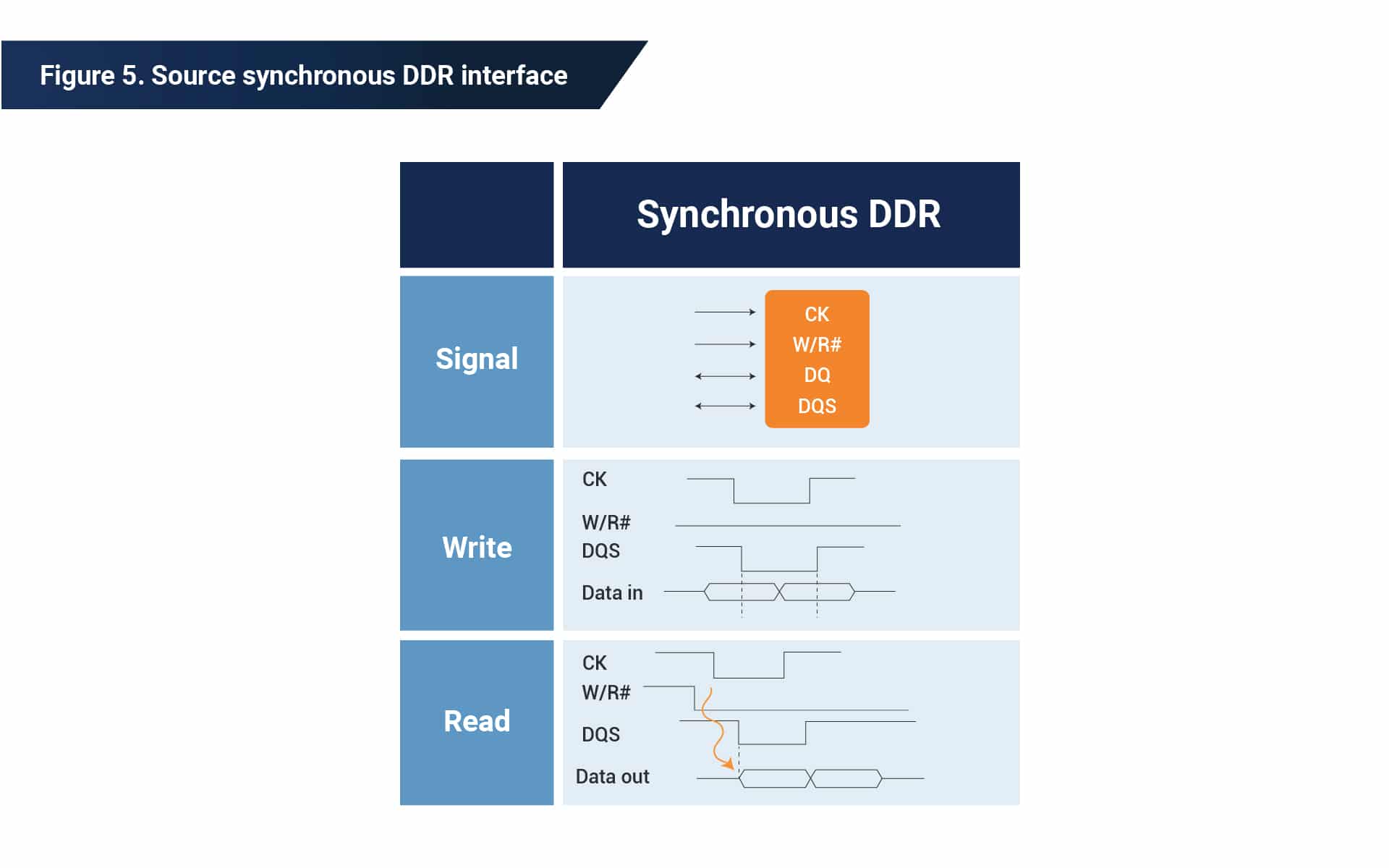

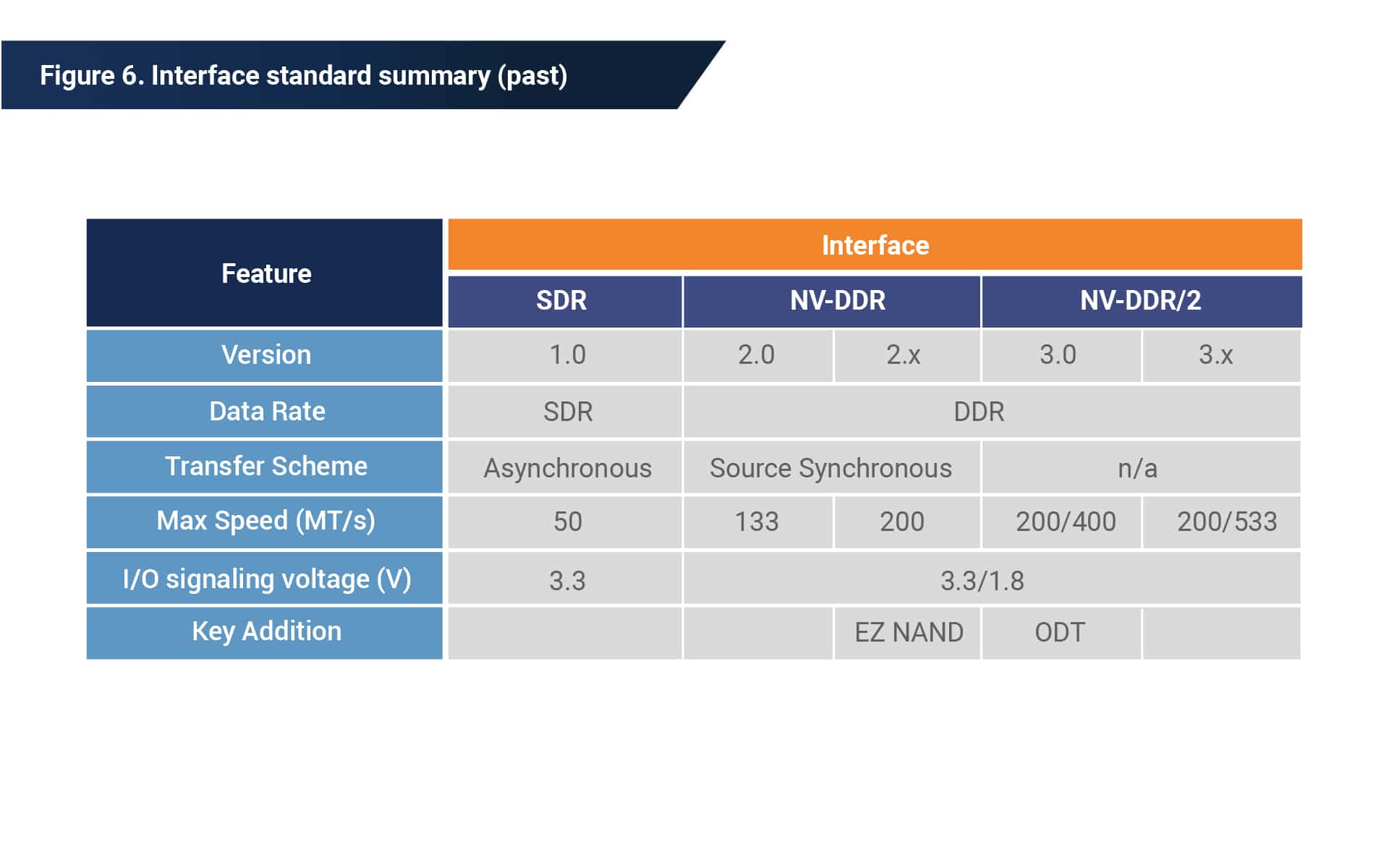

ONFI 2.0 於 2008 年 2 月發布。最重要的變化是採用了雙倍數據速率 (DDR) 傳輸方案,該方案允許在控制信號的兩個邊沿上進行數據傳輸,從而大幅提高設備最大吞吐量。此外,ONFI標準將本規範中的DDR閃存接口修正為NV-DDR(非易失性DDR)接口,使其與隨機存取存儲器(RAM)使用的易失性存儲器DDR接口區分開來。

儘管NV-DDR保留了異步工作方案以向後兼容之前的SDR修訂版,但仍進行了調整以支持源同步方案。具體而言,前WE控制信號成為時鐘信號(CLK),而RE控制信號成為選擇讀寫操作的方向信號。此外,現在數據在新添加的數據選通信號 (DQS) 的上升沿和下降沿上進行傳輸,以實現高達 133MT/s 的雙倍傳輸速率。吞吐量的增加迅速解決了更大尺寸數據傳輸和隨機性能改進的趨勢。

網絡接口2.1

ONFI 2.1 於 2009 年獲得批准,並對 2.0 修訂版的多個部分進行了擴展。 2.1 標準除了提供操作靈活性空間的新功能外,還使最大傳輸速率升級至 200MT/s。

ONFI 規範中的多個部分得到了擴展,首先是報告糾錯編碼 (ECC) 功能的擴展參數頁。作為修訂版 2.1 中的關鍵補充,擴展 ECC 信息允許在 ECC 參數與其他設備參數(例如有效塊數量和支持的編程/擦除週期數量)的指定配對下對 NAND 設備採用多種有效使用方法。

轉向內存組織,交錯尋址和邏輯單元號 (LUN) 的引入除了減少封裝引腳(特別是芯片使能引腳)之外還開闢了工程機會,從而減少了複雜硬件設計的冗餘。

“小數據移動”和“更改行地址”作為設備控制命令引入。 “小數據移動”命令通過縮小設備控制命令中的數據塊來解決低端消費應用程序的 ECC 限制。 “更改行地址”命令旨在通過提高設備操作靈活性來減少工作負載開銷。

網絡接口2.2

基於先前版本的更改,ONFI 2.2 於 2009 年底發布,並提供了有關內存組織的附加指南。規定了對先前引入的交錯尋址的限制,並添加了針對各個 LUN 的重置命令。該修訂還在規範的附錄中定義了當前的測量方法。

網絡接口2.3

ONFI 2.3 於 2010 年 8 月在閃存峰會 (FMS) 上發布,重點關注 EZ-NAND(ECC 零 NAND)協議。該協議建議將ECC管理單元從存儲控制器側轉移到閃存側,從而減輕負擔過重的控制單元的壓力。

ONFI 3.x

ONFI 3.0於2011年3月發布,支持傳輸速率高達400MT/s,適合當時青睞的8K頁面數據對齊大小增加趨勢。吞吐量升級還伴隨著信號電壓降低至 1.8 伏,作為功耗優化的一步。

許多其他新功能的推出提高了閃存創新的上限。片上端接 (ODT) 是本規範修訂版中最具影響力的補充,它是一種通過允許控制器打開和關閉封裝內獨立或所有器件的端接電阻來提高內存通道信號完整性的設計。 。此版本中詳細解決了 ODT 等多芯片封裝功能,以管理精細的芯片級操作和行為。

其他功能包括卷尋址增強和所需芯片使能引腳數量的減少,從而提高了電路佈線效率。然而,隨著版本 3.2 的發布,傳輸速率升級再次成為人們關注的焦點,NV-DDR2 接口下的吞吐量達到 533MT/s,這在當時使同代設備中的閃存升級合法化。

ONFI 4.0

ONFI 4.0 規範於 2012 年推出,將以前已知的 NV-DDR2 的傳輸速率升級至 667 MT/s,將新推出的 NV-DDR3 的傳輸速率升級至 800MT/s。引入了一種稱為 ZQ 校準的技術作為 ODT 輔助工具來校準終端電阻。該規範限制了電壓或溫度變化時信號完整性的損害。此外,這些增強功能使 I/O 電源 (VCCQ) 要求降至 1.2 伏,從而改善功耗。

ONFI 4.x

從 4.0 版開始擴展的 ONFI 規範包含了多項變化,包括電源配置靈活性、補貼功能參數定義以及額外的物理引腳分配選項。

從ONFI 4.1開始,核心控制電壓(VCC)的選項開放為2.5伏,並在原來的3.3/1.8/1.2設置的基礎上增加了從2.35伏到3.6伏的一系列配置。

在 ZQ 校準之上添加了佔空比校正 (DCC) 和 DQ 讀/寫訓練,作為在初始化過程中促進 NAND 器件調整的功能。此更改專門針對運行速度超過 800MT/s、工作負載繁重的設備。 DCC 訓練的目的是補償“讀啟用補充”信號(“讀啟用”信號的補充信號)的潛在佔空比不匹配。這

DQ 培訓旨在嘗試將 DQS 和 DQ 信號與主機端系統保持一致。

在 4.2 版本中,對 DCC 培訓規範的細節進行了修改,同時物理引腳分配選項也發生了其他變化。具體來說,252 球球柵陣列 (BGA) 分配加入了以前的 BGA-272 和 BGA-316 分配,作為物理接口的新選項。

光網絡FI 5.0

ONFI 5.0 於 2021 年初發布。新發布的標準規範中還揭示了另外三個引腳分配選項,以及正確採用所需更改的說明。但更重要的是NV-LPDDR4接口,強調降低整體功耗,同時提高每個接口的傳輸速率,即NV-DDR2為800MT/s,NV-DDR3和NV-LPDDR4高達2400MT/s。由於傳輸速率提高,支持 NV-LPDDR4 的設備可以利用數據總線反轉 (DBI) 功能,通過控制信號方向和電流量來限制功耗。

另一方面,NV-LPDDR4的到來引發了ODT功能修改的又一次推動。 ODT 禁用/啟用和通道 ODT 等附加功能解決了新 NV-LPDDR4 接口對 ODT 的潛在影響。

在啟用 NV-LPDDR4 時,NAND 器件和控制器之間的內部參考電壓可能會處於未經訓練的狀態,但 ODT 引起的小信號擺幅可能會導致命令序列失敗。因此,正確定時禁用/啟用 ODT 可以顯著影響新接口下的操作。

除了這種類似開關的功能之外,通道 ODT 設置還可以控制 NAND 輸出上拉電阻的強度,從而控制信號終端電阻。換句話說,該設置實質上允許主機端在數據輸出操作期間決定每個通道內的最佳ODT強度。同時,NAND 器件會根據供應商特定的設置值進行相應調整。

切換界面

在 ONFI 1.0 發布後的第二年,世界領先的兩家 NAND 閃存製造商三星半導體和東芝存儲器公司 (TMC) 推出了 Toggle 接口標準,作為驅動閃存設備操作超越傳統功能的替代方案。使用 Toggle 接口的設備還在各種硬件配置、信號模式和電氣特性中按照一組可擴展、精心編織的準則進行操作。 Toggle 標準的演變發生在三星和 TMC 向客戶特定發布的 NAND 設備規範中,而不是向公眾發布。這與 ONFI 標準形成鮮明對比,ONFI 標準是根據其工作組的統一公開版本進行更新的。

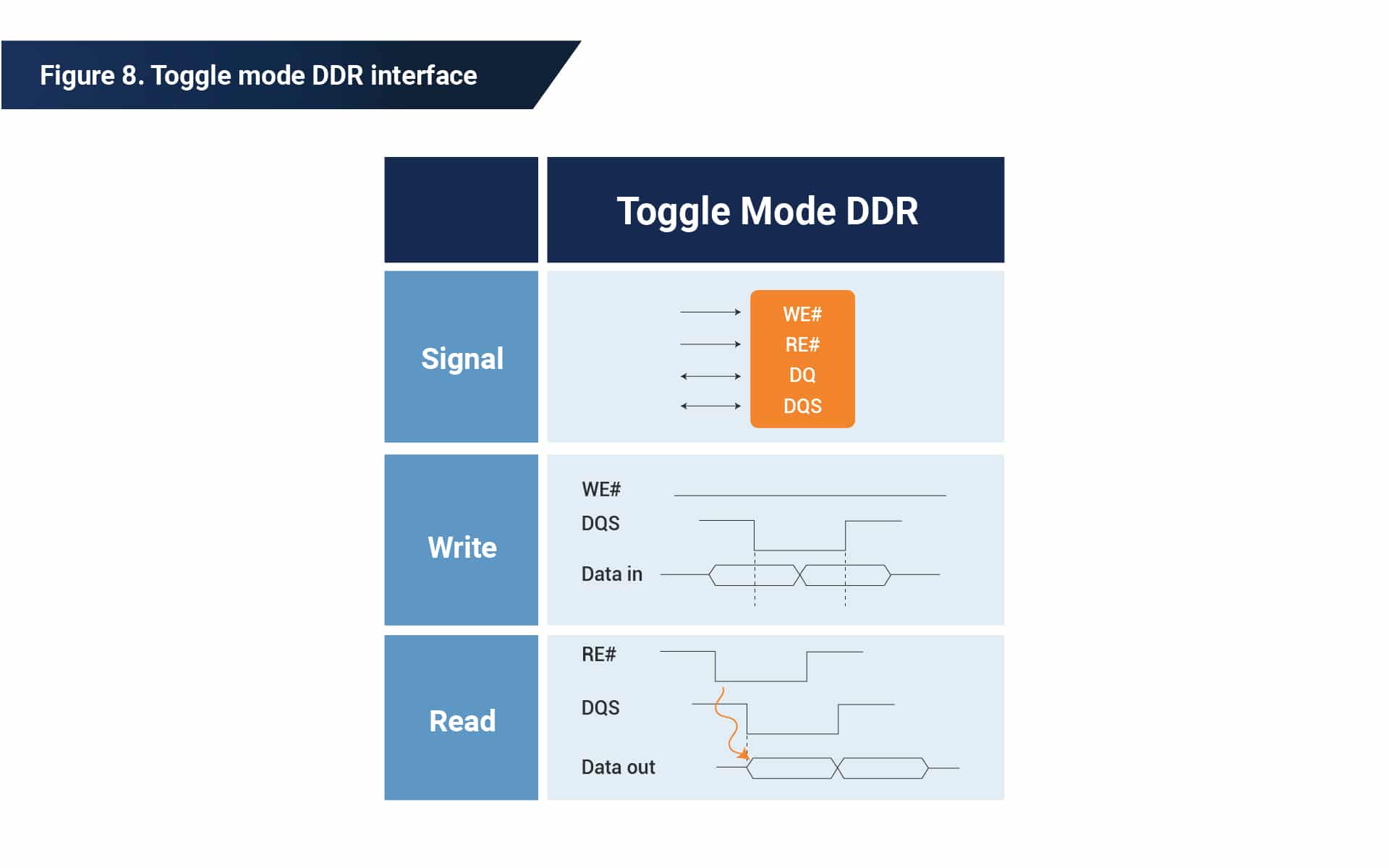

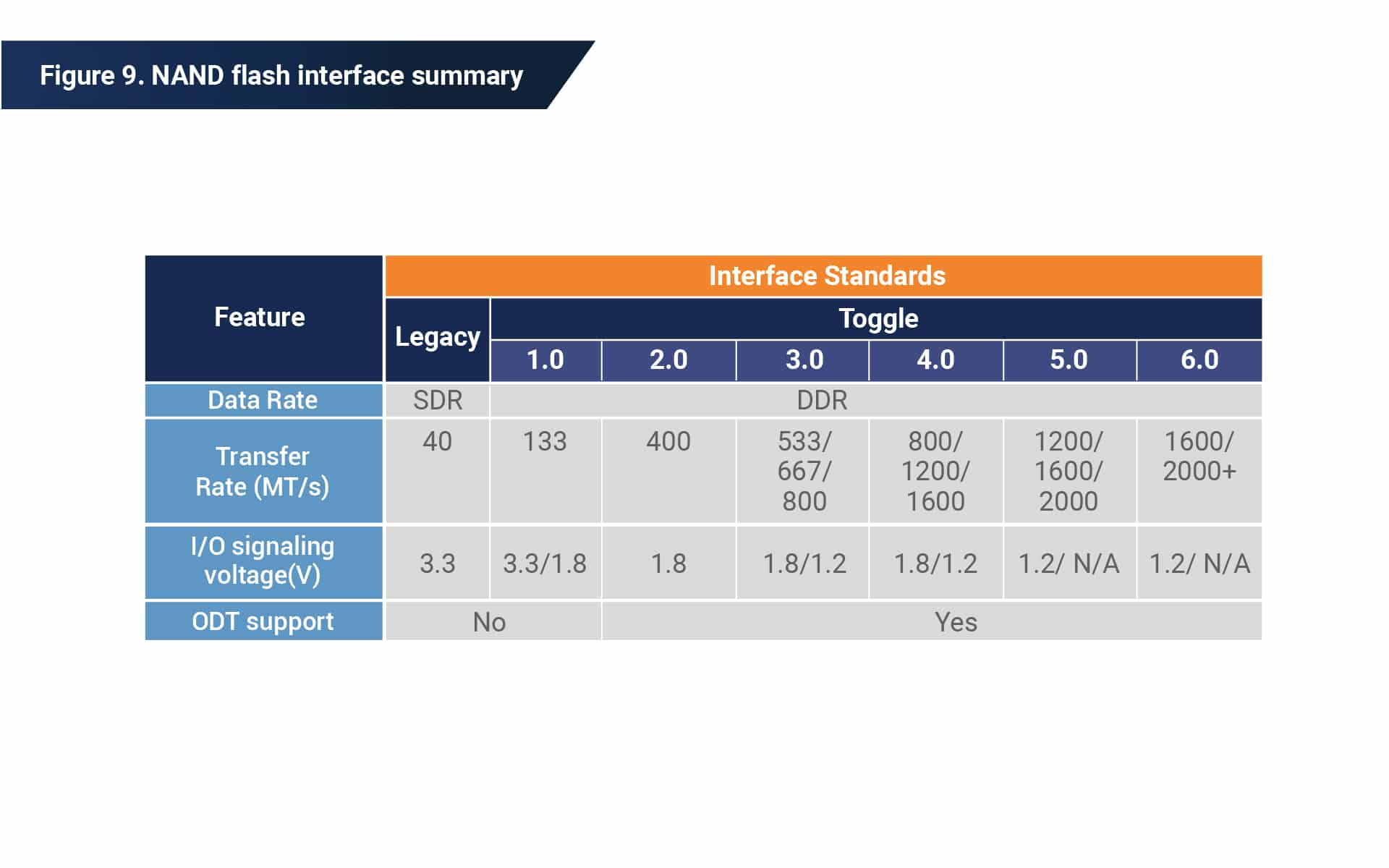

切換1.0

乍一看,第一代 Toggle DDR 接口具有與 ONFI 2.0 修訂版相同的一般特徵。 Toggle 1.0 使用雙向 DQS 選通信號實現高達 133MT/s 的數據傳輸速率,每個上升沿和下降沿都與一次數據傳輸相關。然而,ONFI 和 Toggle 之間的區別在於,Toggle 數據傳輸在沒有時鐘信號的情況下進行操作,使其僅在發生讀寫操作時與功耗異步。 ONFI 在 3.0 版本中也採用了這種實現方式,以其在功效方面的優勢和設計簡單性。

切換 2.0 / 3.0 / 4.0

Toggle 2.0 支持的設備允許吞吐量高達 400 MT/s,與在 ONFI 3.0 下運行的設備相當。然而,根據發佈時間,只有部分 Toggle 2.0 設備支持 ODT 功能。

雖然 Toggle 3.0 設備於 2015 年推出,支持 533MT/s 和 667MT/s 的傳輸速率選項,並完全支持 ODT 和 ZQ 校準功能,但主流的 Toggle 標準修訂版是 Toggle 4.0 標準。在其最早版本中,Toggle 4.0 接口可實現高達 800MT/s 和 1200MT/s 的傳輸速率,同時支持與 ONFI 匹配的必要功能,但根據產品的不同,插圖也有所不同。

當然,接口標準是針對最新的 NAND 閃存技術而設計的,即 Kioxia(以前稱為 TMC)和 Western Digital 的 BiCS 系列,以及三星和 SK Hynix 等韓國供應商的 V-NAND 系列。事實上,隨著新的閃存設計和技術的推出,閃存供應商已經能夠通過在同一代接口中反複試錯來校準閃存行為來調整傳輸速率。群聯一直與其閃存供應商合作夥伴合作,以實現傳輸速率突破 2000MT/s 以上,並在系統前端性能面臨下一代互連挑戰的最佳時機進行各種設計改進。

切換 5.0 / 6.0

隨著開發人員孜孜不倦地構建閃存接口標準手冊中的構建塊,未來是光明的。隨著3D閃存技術正式進入百層堆疊時代,業界正在期待向更快、更前沿的接口交換速度過渡。不久之後,Toggle 5.0 和 6.0 接口預計將以高於 2400 MT/s 的傳輸速率運行,即每個芯片的傳輸速率高於 250 MB/s。隨著閃存拓撲和設計變更討論的持續進行,業界預計會有更多功能添加和改進,以推進主流標準。

NAND閃存的未來

在過去的20年裡,ONFI和Toggle NAND閃存接口蓬勃發展,並被公認為開發NAND閃存應用的行業標準。截至 2021 年,這兩個標準的最新版本已將 NAND 閃存性能提升至傳統傳統功能的十倍以上,同時實現更高的模塊容量並降低功耗。群聯電子擁有 1900 多項全球專利和 20 年閃存行業經驗,已準備好提供內存控制器支持,以滿足兩種主要接口下任何應用程序的需求。