NAND フラッシュ技術の開発は、業界からの多数の意見に基づいて着実に前進しています。ホスト デバイス ソリューション プロバイダーとストレージ デバイス メーカーとのコラボレーションにより、標準化されたインターフェイスの確立が促進され、今日のエコシステムに至るまで共同で構築されてきました。

一般に公開されている最も有名な 2 つのインターフェイス標準は、Open NAND Flash Interface (ONFI) と Toggle 標準の 2 つで、それぞれの権威あるワークグループによって開発され、継続的に拡張されています。 2 つの規格間には対比や比較が可能ですが、広く認識されている「共通点」は、Joint Electron Device Engineering Council (JEDEC) によって発行された JESD230 規格であり、開発者が規格から抽出する参照として利用できます。セット。

各標準セットの独自の開発は、フラッシュおよびストレージ業界のリーダーのグループの異なる範囲と知識の下で形成されているため、コマンド、アドレス指定、タイミング、フォーマット、および物理構成の違いによって明らかです。それにも関わらず、両方の標準は、異なるテクノロジー間の互換性と相互運用性を目指して一貫性を保っています。

従来のインターフェイス

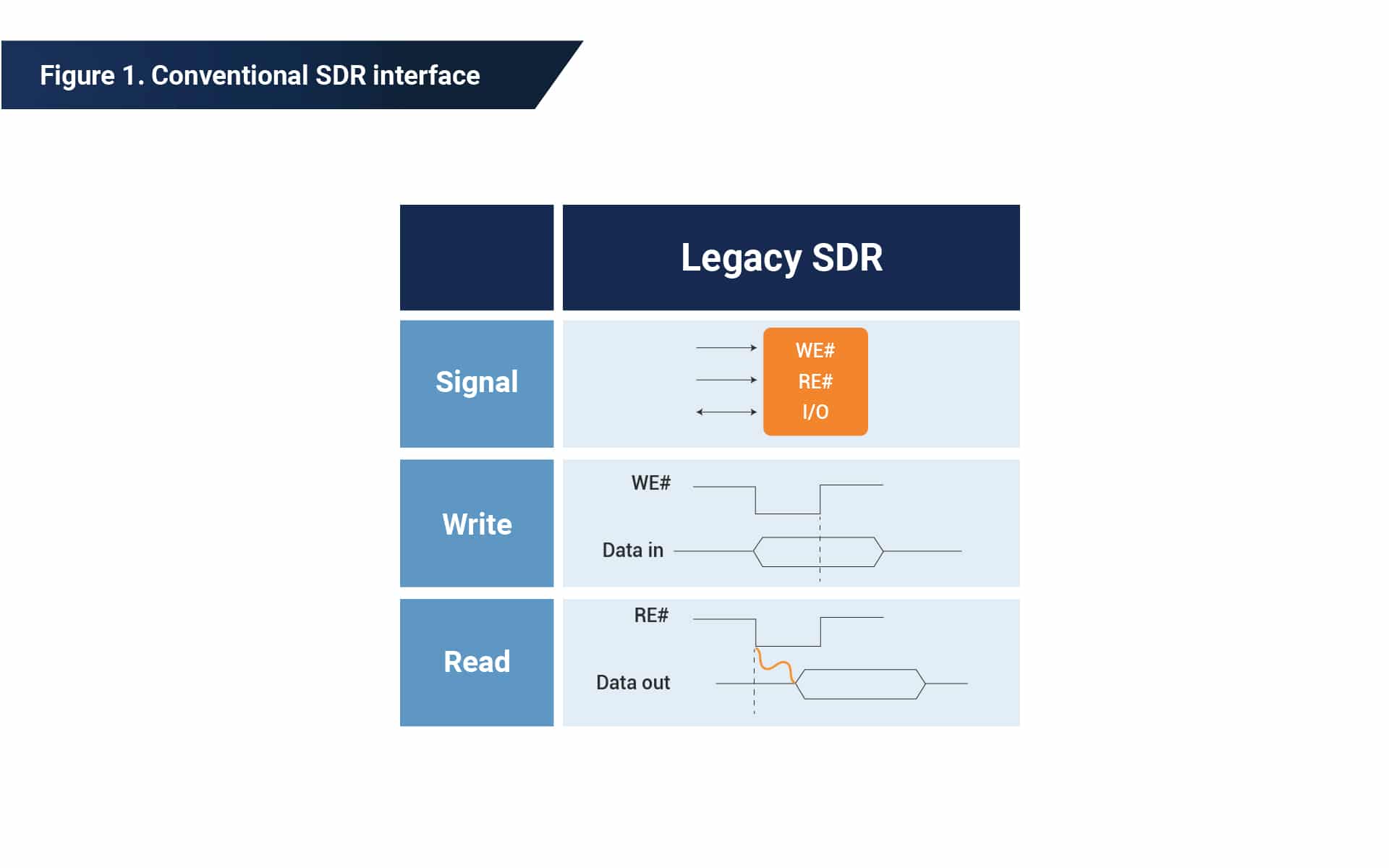

フラッシュ インターフェイスの知識を詳しく調べると、同期データ転送方式と非同期データ転送方式の比較をすぐに特定できます。レガシーとして知られる最初の NAND フラッシュ デバイス インターフェイスは、データ転送のタイミング基準に関連する非同期転送スキームを利用するように構成されました。信号の完全性と精度を向上させるために、同期方式を使用して、連続クロック信号と同期する必要がある信号を制御します。非同期方式により、クロックを必要とせずに、転送タスクのトリガーを「書き込みイネーブル (WE)」および「読み取りイネーブル (RE)」制御信号に完全に依存させることができます。

さらに、レガシーはシングル データ レート (SDR) でのデータ転送をサポートし、制御信号の 1 つのエッジでのみデータ転送を処理します。具体的には、インターフェイスは、データがデバイスの内外に「移動」されるときに、書き込み信号の立ち上がりエッジと読み取り信号の立ち下がりエッジでのみ、定式化された信号アライメントを強制します。

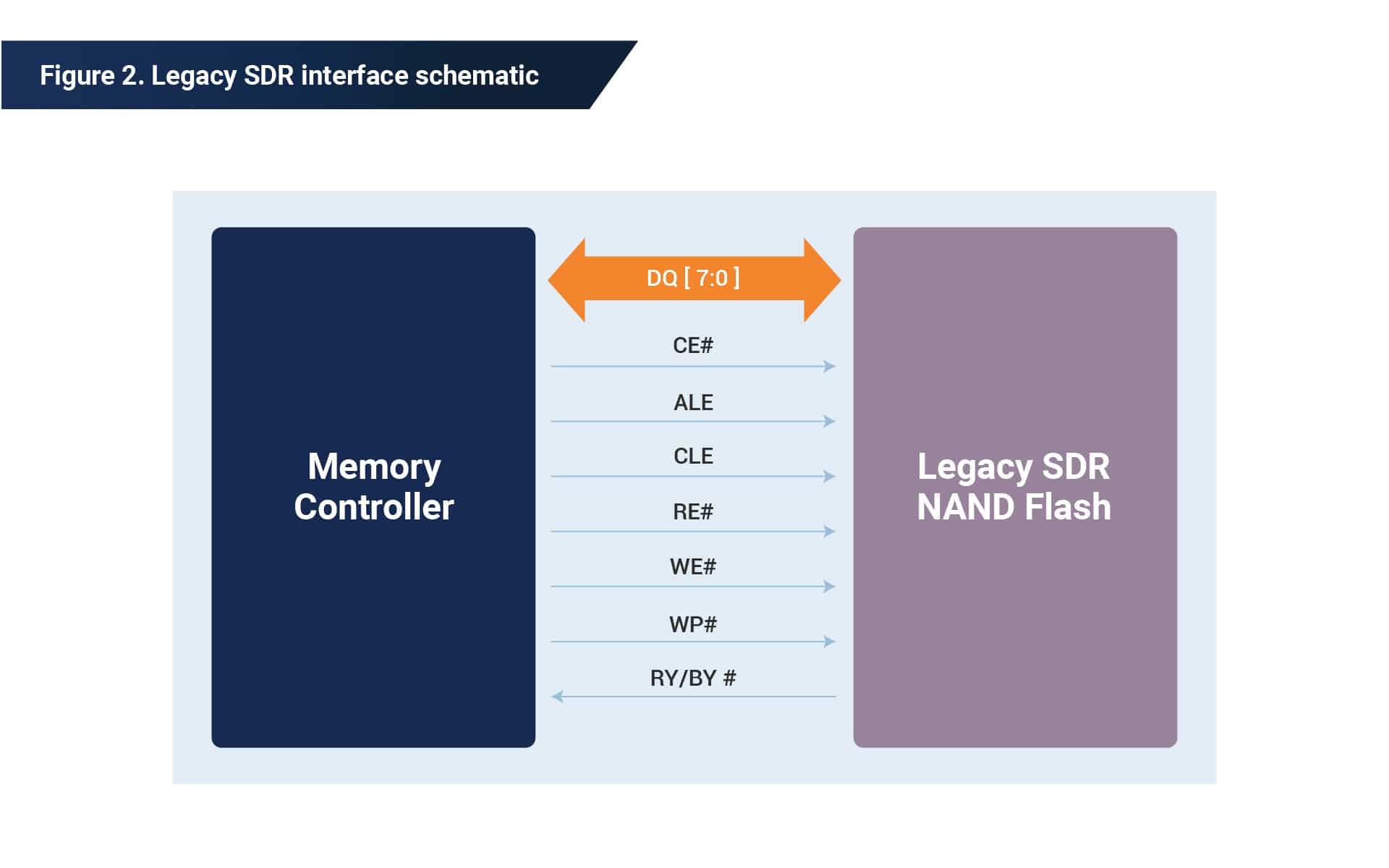

I/O シグナリング (DQ) 用の 8 ビット (b) 双方向データ バスに加えて 7 つの制御信号ピンを備えた 15 ピン インターフェイスは、25 ナノ秒 (ns) の転送時間内でバイト (B) の配信を実現します。 )。この属性に基づいて、最大帯域幅は 40MB/s、またはデータ ピンごとに 40Mb/s として計算できます。 (1B/25ns = 0.04×109 B/s = 40 MB/s、1B = 8b)

ONFI インターフェース

2006 年、SK Hynix、Intel、Micron、SanDisk、Phison、Sony などの大規模なテクノロジー企業グループが Open NAND Flash Interface (ONFI) Working Group を結成しました。その年の後半、ONFI 標準の最初のバージョンが起草され、リリースされました。これは、フラッシュ市場の組織化されていない性質 (ストレージ製品、フラッシュ ベンダー、およびダウンストリーム間のフラッシュ インターフェイスの基準が一貫していないことに起因する) に対応する統一標準を提供することを目的としていました。製品メーカー)。

多面的な ONFI 標準は、機能の特性評価、機能/コマンド セットの調整、信号の説明/タイミング条件、動作フロー、レジスタ レベル/物理仕様など、市場が切実に必要としている適切なインターフェイスの重要な側面を示しました。現在、ONFI ワークグループは一連の標準を拡張するアップデートをリリースし続けており、2021 年の最新のドラフトは ONFI 5.0 です。

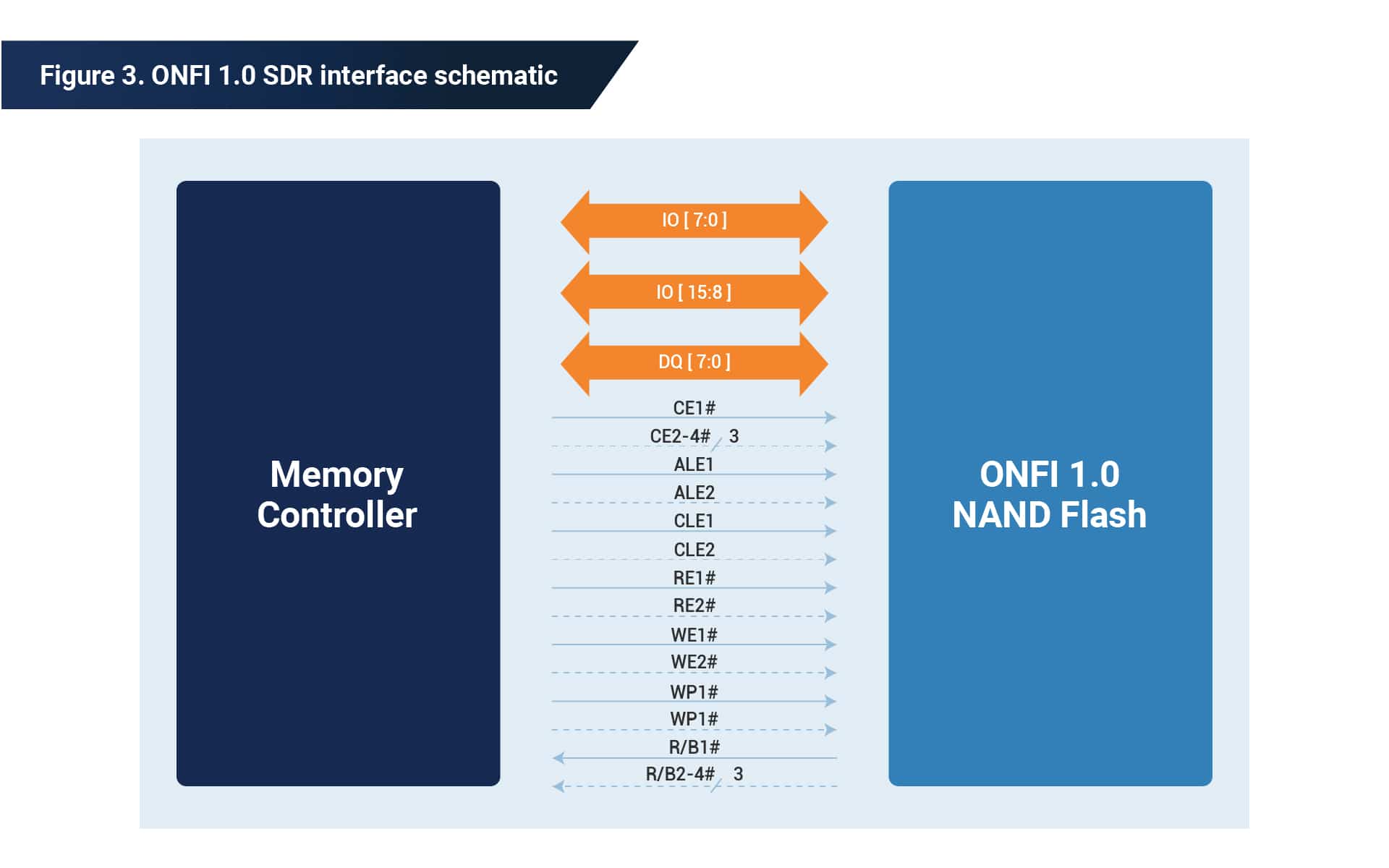

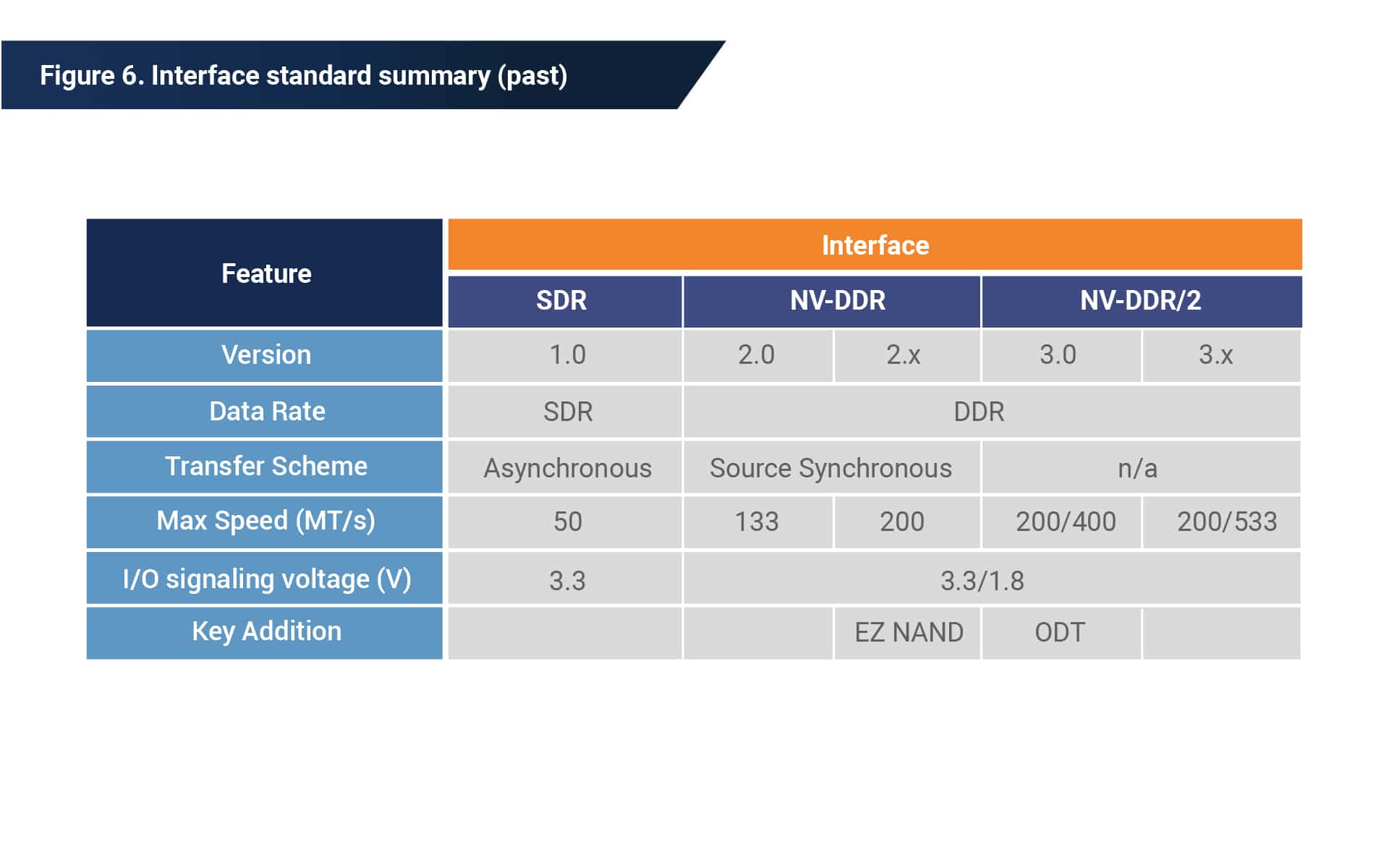

ONFI 1.0

最初のリリースの主な目的は、レガシーから拡張された迅速なインターフェイス標準化を提供することでした。バージョン 1.0 では、非同期 SDR 転送方式を採用しながら、従来のレガシーと同様の電気インターフェイスについて説明しましたが、オプションで制御信号のアップスケーリングを備えた 16 ビット データ バスなどの最先端技術をサポートしました。 50MB/秒の帯域幅は、レガシーの以前の 40MB/秒パフォーマンスよりも 20% の向上をマークしました。

ONFI 2.0

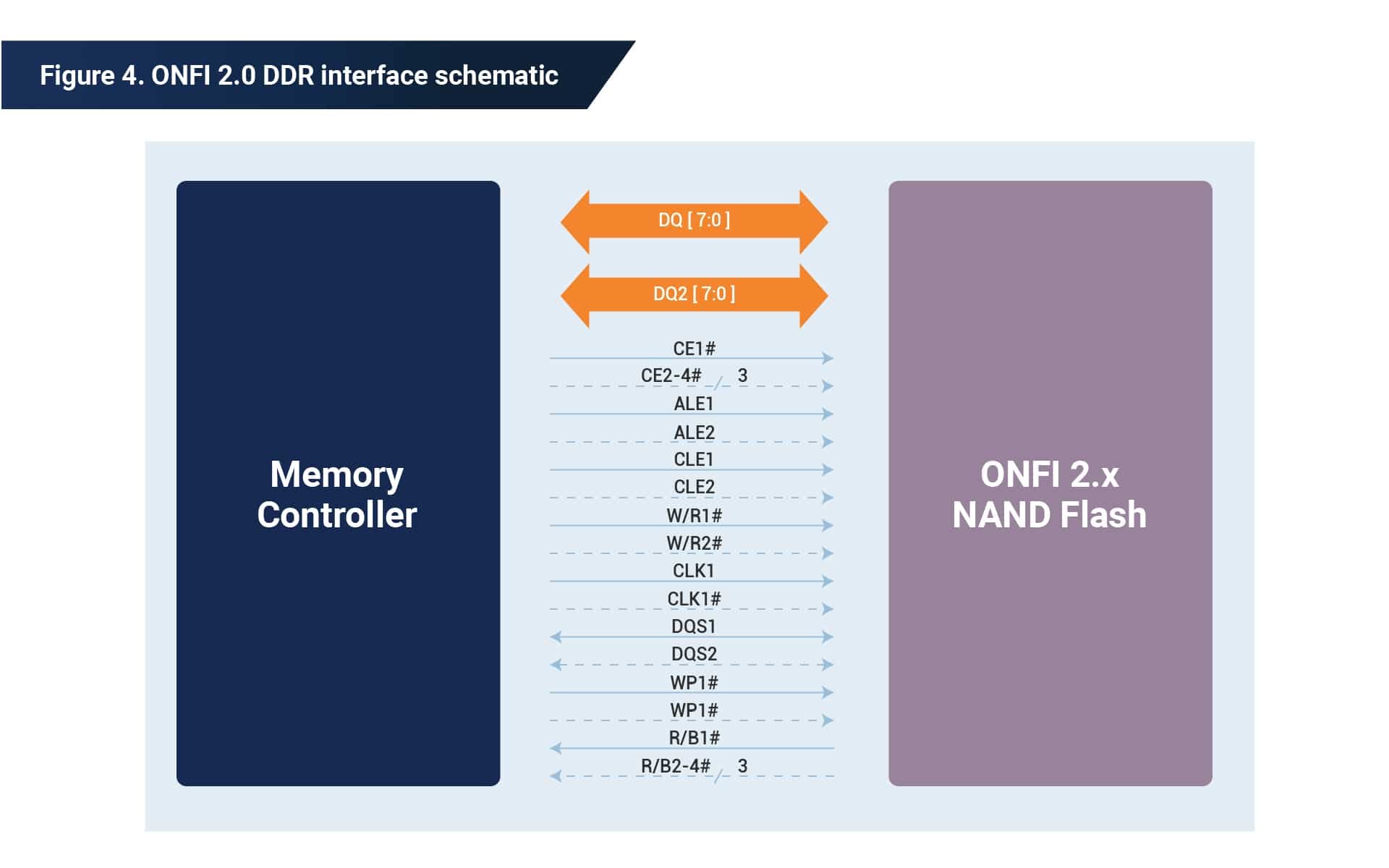

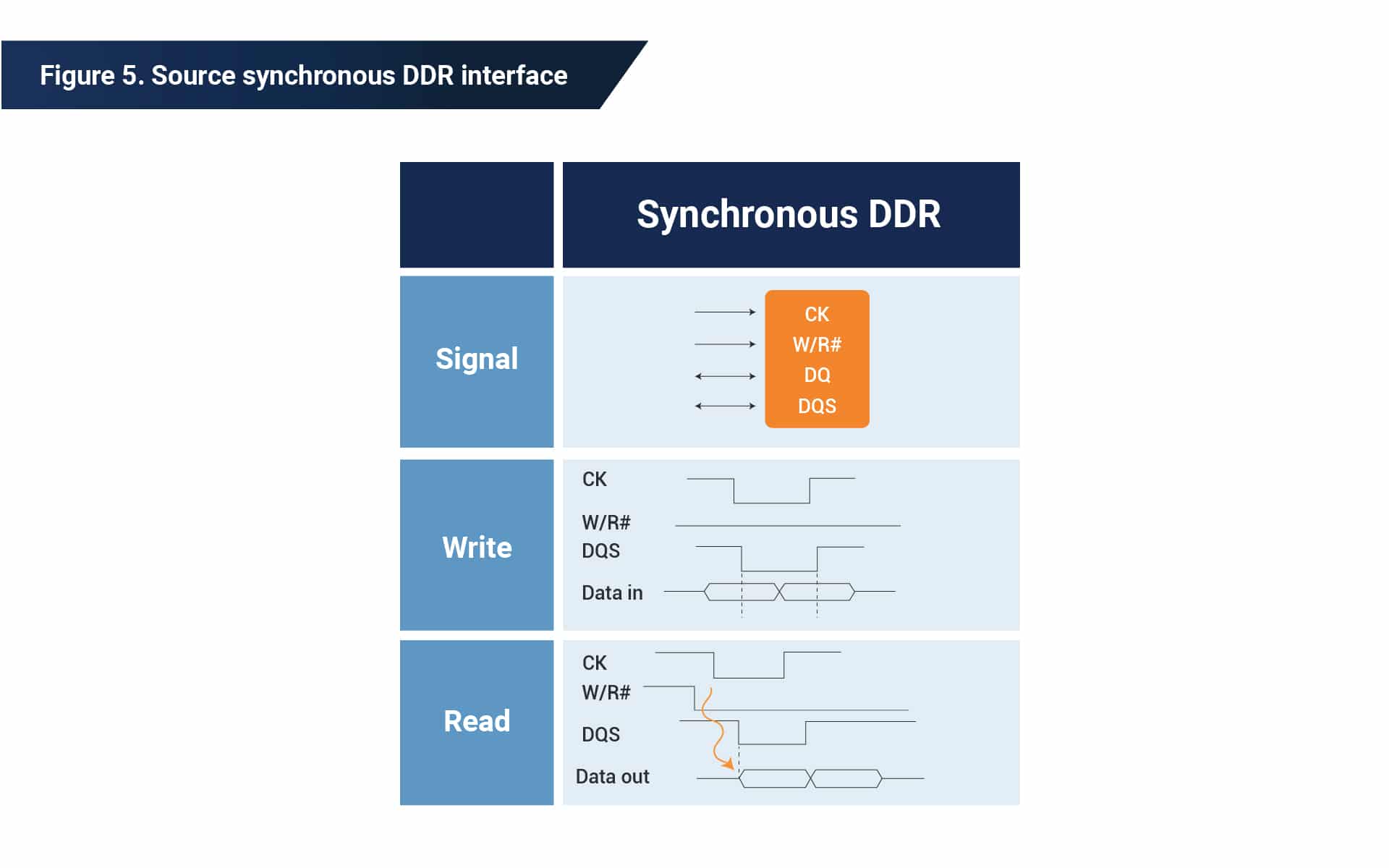

ONFI 2.0 は 2008 年 2 月にリリースされました。最も重要な変更は、制御信号の両端でのデータ転送を可能にすることでデバイスの最大スループットの大幅な増加を可能にするダブル データ レート (DDR) 転送スキームの採用でした。さらに、ONFI 標準は、この仕様内の DDR フラッシュ インターフェイスを NV-DDR (不揮発性 DDR) インターフェイスとして修正し、ランダム アクセス メモリ (RAM) で使用される揮発性メモリ DDR インターフェイスと区別できるようにしました。

NV-DDR は、以前の SDR リビジョンとの下位互換性のために非同期動作スキームを保持していましたが、ソース同期スキームをサポートするために調整が行われました。具体的には、前者のWE制御信号はクロック信号(CLK)となり、RE制御信号は読み出し動作と書き込み動作を選択する方向信号となりました。さらに、新たに追加されたデータ ストローブ信号 (DQS) の立ち上がりエッジと立ち下がりエッジの両方でデータが転送されるようになり、最大 133MT/s まで 2 倍の転送速度を達成しました。スループットの向上により、より大きなサイズのデータ転送とランダムなパフォーマンスの向上の傾向に即座に対応しました。

ONFI 2.1

ONFI 2.1 は、2.0 リビジョンの複数のセクションを拡張して 2009 年に承認されました。 2.1 規格では、運用の柔軟性を高める新機能に加えて、最大転送速度が 200MT/s にアップグレードされました。

ONFI 仕様内の複数のセクションが拡張され、まず、誤り訂正符号化 (ECC) 機能を報告する拡張パラメータ ページが追加されました。リビジョン 2.1 での重要な追加点として、拡張 ECC 情報により、有効なブロック数やサポートされるプログラム/消去サイクル数など、ECC パラメーターと他のデバイス パラメーターの指定された組み合わせの下で、NAND デバイスの複数の有効な使用方法が可能になりました。

メモリ構成に移ると、インターリーブ アドレッシングと論理ユニット番号 (LUN) の導入により、パッケージ ピン、特にチップ イネーブル ピンの削減に加えて、エンジニアリングの機会が開かれ、複雑なハードウェア設計の冗長性が減少しました。

デバイス制御コマンドとして「Small Data Move」と「Change Row Address」が導入されました。 「Small Data Move」コマンドは、デバイス制御コマンドのデータ チャンクを縮小することで、ローエンドのコンシューマ アプリケーションの ECC 制限に対処しました。 「行アドレス変更」コマンドは、デバイスの動作の柔軟性を高めることでワークロードのオーバーヘッドを削減することを目的としています。

ONFI 2.2

前のリビジョンからの変更点に基づいて、メモリ構成に関する追加のガイドラインを備えた ONFI 2.2 が 2009 年末にリリースされました。以前に導入されたインターリーブ アドレッシングに対する制限が記載され、個々の LUN に対するリセット コマンドが追加されました。この改訂版では、仕様の付録内で電流測定方法も定義されました。

ONFI 2.3

ONFI 2.3 は、EZ-NAND (ECC Zero NAND) プロトコルに焦点を当て、2010 年 8 月のフラッシュ メモリ サミット (FMS) でリリースされました。このプロトコルでは、ECC 管理ユニットをストレージ コントローラー側からフラッシュ側に移行し、負担のかかるコントロール ユニットからの負担を軽減することが推奨されています。

ONFI 3.x

ONFI 3.0 は 2011 年 3 月に発表され、サポートされる転送速度が最大 400MT/s まで野心的に向上し、当時好まれていた 8K ページ データ アライメント サイズの増加傾向に適していました。スループットのアップグレードには、消費電力の最適化に向けたステップとして、信号電圧が 1.8 ボルトに低減されたことも含まれています。

フラッシュのイノベーションの限界を高めるために、他にも多くの新機能が導入されました。オンダイターミネーション (ODT) は、コントローラーがパッケージ内の独立したデバイスまたはすべてのデバイスの終端抵抗をオン/オフできるようにすることで、メモリ チャネルの信号整合性を向上させる設計として、この仕様改訂におけるより影響力のある追加として先導しました。 。 ODT のようなマルチダイ パッケージ機能は、繊細なダイ レベルの動作と動作を管理するために、このリビジョン内で詳細に取り上げられました。

その他の機能としては、ボリューム アドレッシングの強化や、必要なチップ イネーブル ピンの数の減少が含まれており、これにより回路配線の効率が向上しました。しかし、リビジョン 3.2 がリリースされると、NV-DDR2 インターフェイスで 533MT/s のスループットが利用可能になり、転送速度のアップグレードが再び注目を集めました。これにより、当時、同世代のデバイス内でのフラッシュのアップグレードが合法化されました。

ONFI 4.0

ONFI 4.0 仕様は 2012 年に導入され、転送速度が以前の NV-DDR2 では 667 MT/s、新しく導入された NV-DDR3 では 800 MT/s にアップグレードされました。 ZQ キャリブレーションと呼ばれる手法は、終端抵抗をキャリブレーションするための ODT 容易化ツールとして導入されました。この仕様は、電圧または温度が変化した場合の信号の完全性の低下を制限しました。さらに、これらの機能強化により、I/O 電力 (VCCQ) 要件が 1.2 ボルトまで低下し、消費電力が改善されました。

ONFI 4.x

バージョン 4.0 から拡張された ONFI 仕様には、電源構成の柔軟性、機能パラメータ定義の補助、追加の物理ピン割り当てオプションなど、いくつかの変更が含まれています。

ONFI 4.1 以降、コア制御電圧 (VCC) のオプションが 2.5 ボルトとして開放され、2.35 ボルトから 3.6 ボルトまでの設定範囲が元の 3.3/1.8/1.2 設定に追加されました。

初期化プロセス中の NAND デバイスの調整を容易にする機能として、ZQ キャリブレーションに加えて、デューティ サイクル補正 (DCC) と DQ 読み取り/書き込みトレーニングが追加されました。この変更は、特に、重いワークロードで 800MT/秒を超えて動作するデバイスを対象としています。 DCC トレーニングは、「Read Enable Complement」信号 (「Read Enable」信号の相補信号) の潜在的なデューティ サイクルの不一致を補償することを目的としています。の

DQ トレーニングは、DQS 信号と DQ 信号をホスト側システムに合わせて調整する試みとして機能しました。

4.2 リビジョンでは、DCC トレーニング仕様の詳細に変更が加えられ、物理的なピン割り当てオプションにもその他の変更が加えられました。具体的には、252 ボールのボール グリッド アレイ (BGA) 割り当てが、物理インターフェイスの新しいオプションとして、以前の BGA-272 および BGA-316 割り当てに加わりました。

ONFI 5.0

ONFI 5.0 のリリースは 2021 年初頭に行われました。新たにリリースされた標準仕様では、さらに 3 つのピン割り当てオプションが明らかになり、適切な採用に必要な変更手順も明らかにされました。しかし、より重要なのは NV-LPDDR4 インターフェイスであり、各インターフェイスの転送速度をアップスケーリングしながら全体の消費電力を削減すること、つまり NV-DDR2 で 800 MT/s、NV-DDR3 と NV-LPDDR4 で最大 2400MT/s を強調しました。転送速度の向上により、NV-LPDDR4 をサポートするデバイスはデータ バス反転 (DBI) 機能を利用して、信号の方向と電流量を制御することで消費電力を制限できます。

一方で、NV-LPDDR4 の登場により、ODT の機能変更がさらに推進されるようになりました。 ODT の無効化/有効化やチャネル ODT などの追加機能は、新しい NV-LPDDR4 インターフェイスによって ODT が受ける潜在的な影響に対処しました。

NV-LPDDR4 を有効にすると、NAND デバイスとコントローラー間の内部基準電圧がトレーニングされていない状態のままになる可能性がありますが、ODT によって引き起こされる小さな信号振幅により、コマンド シーケンスの失敗が発生する可能性があります。したがって、適切なタイミングで ODT を無効化/有効化すると、新しいインターフェイスでの操作に大きな影響を与える可能性があります。

このスイッチのような機能とは別に、チャネル ODT 設定により、NAND 上の出力プルアップ抵抗の強度、つまり信号終端抵抗を制御できるようになります。言い換えれば、この設定により、ホスト側はデータ出力操作中に各チャネル内の最適な ODT 強度を決定できるようになります。同時に、NAND デバイスはベンダー固有の設定値に基づいて調整されます。

トグルインターフェイス

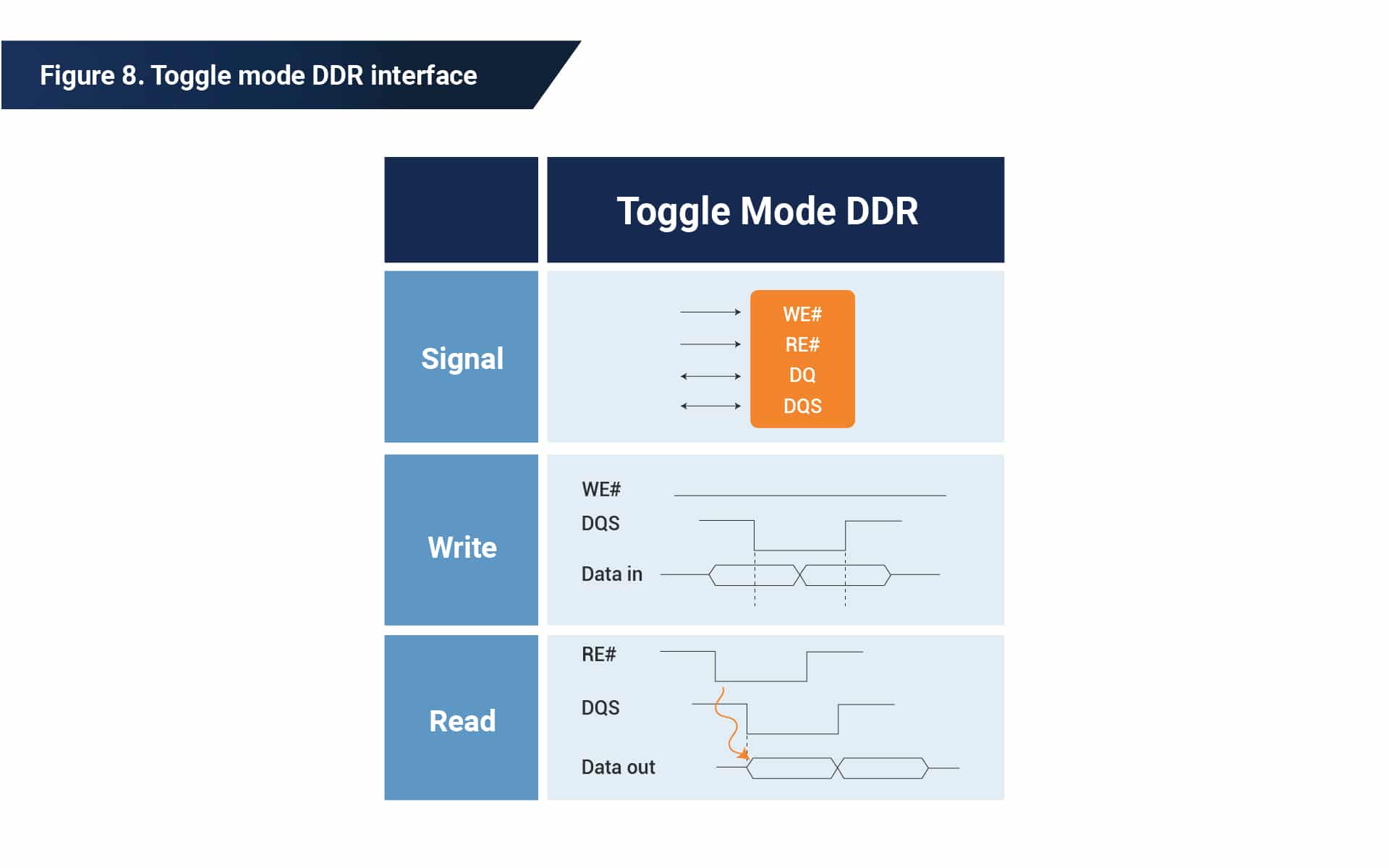

ONFI 1.0 のリリース直後の年に、世界をリードする NAND フラッシュ メーカーの 2 社であるサムスン セミコンダクターズと東芝メモリ コーポレーション (TMC) は、レガシー機能を超えてフラッシュ デバイスの動作を推進する代替手段として Toggle インターフェイス標準を導入しました。 Toggle インターフェイスを利用するデバイスは、さまざまなハードウェア構成、信号パターン、および電気特性における、拡張可能で綿密に編まれた一連のガイドラインにも基づいて動作します。 Toggle 標準の進化は、一般公開ではなく、Samsung と TMC からの NAND デバイス仕様の顧客固有のリリースの中で発生しました。これは、ワークグループからの統一公開リリースに基づいて更新された ONFI 標準とは対照的でした。

1.0を切り替える

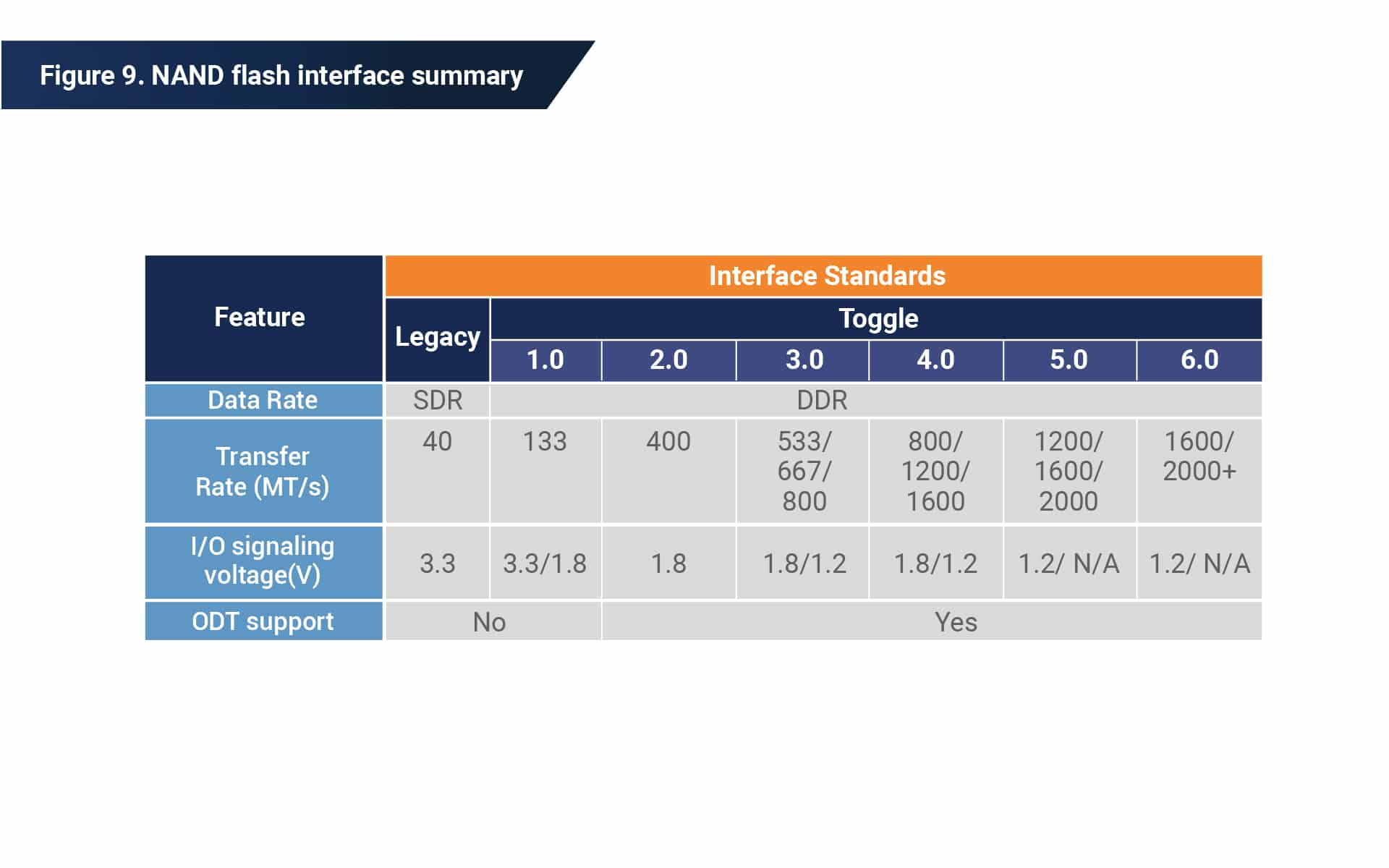

一見すると、第 1 世代の Toggle DDR インターフェイスには、ONFI 2.0 リビジョンと共通する一般的な特徴がありました。 Toggle 1.0 では、双方向 DQS ストローブ信号を使用し、各立ち上がりエッジと立ち下がりエッジが 1 つのデータ転送に関連付けられ、最大 133MT/s のデータ転送速度が可能になりました。ただし、ONFI と Toggle の違いは、Toggle データ転送はクロック信号なしで動作するため、読み出し動作と書き込み動作の発生時のみ非同期で消費電力が発生することです。 ONFI も、リビジョン 3.0 で電力効率と設計のシンプルさの点で優れたこのような実装を採用しました。

2.0 / 3.0 / 4.0を切り替え

Toggle 2.0 でサポートされているデバイスでは、最大 400 MT/秒のスループットが可能であり、ONFI 3.0 で動作するデバイスと同等になります。ただし、リリースのタイミングによっては、Toggle 2.0 デバイスの一部のみが ODT 機能をサポートしていました。

Toggle 3.0 デバイスは 533MT/s および 667MT/s の転送速度オプションをサポートし、ODT および ZQ キャリブレーション機能を完全にサポートして 2015 年に登場しましたが、主流の Toggle 標準リビジョンは Toggle 4.0 標準です。初期のリリースでは、Toggle 4.0 インターフェイスは最大 800MT/s および 1200MT/s の転送速度を可能にし、ONFI に一致する必要な機能をサポートしましたが、図は製品によって異なります。

もちろん、インターフェイス規格は、最新の NAND フラッシュ テクノロジー、つまり Kioxia (旧 TMC) および Western Digital 向けの BiCS シリーズと、Samsung や SK Hynix などの韓国のサプライヤー向けの V-NAND シリーズをターゲットとして設計されました。実際のところ、新しいフラッシュの設計とテクノロジーが展開されるにつれ、フラッシュ ベンダーは、同じ世代のインターフェイス内で試行錯誤を繰り返してフラッシュの動作を調整することで、転送速度を調整することができました。 Phison は、フラッシュ ベンダー パートナーと協力して、システム フロントエンドのパフォーマンスが次世代相互接続の課題に直面する中で、完璧なタイミングで実現したさまざまな設計改善とともに、2000MT/s を超える転送速度の飛躍的な進歩を実現してきました。

5.0 / 6.0を切り替えます

開発者がフラッシュ インターフェイスの標準規格の基礎となる要素を熱心に積み上げているため、未来は明るいです。 3D フラッシュ テクノロジーが正式に 100 層以上の積層時代に突入したため、業界はさらに高速で最先端のインターフェイス交換速度への移行が差し迫っていると考えています。間もなく、Toggle 5.0 および 6.0 インターフェイスは 2400 MT/s 以上の転送速度で動作する予定で、これはダイあたり 250 MB/s 以上に相当します。フラッシュ トポロジと設計変更の議論が進行中であるため、業界は主流の標準を前進させるためにさらなる機能の追加と改善を期待しています。

NANDフラッシュの未来

過去 20 年間で、ONFI および Toggle NAND フラッシュ インターフェイスが普及し、NAND フラッシュ アプリケーション開発の業界標準として認識されました。 2021 年の時点で、両方の規格の最新リリースでは、NAND フラッシュのパフォーマンスが従来のレガシー機能の最大 10 倍以上になり、モジュール容量の増加と消費電力の削減が可能になりました。 Phison は、1900 を超える世界中の特許と 20 年間のフラッシュ業界の経験を持ち、2 つの主要なインターフェイスのいずれかであらゆるアプリケーションのニーズに対応するメモリ コントローラー サポートを提供する準備ができています。