基于业界的大量投入,NAND闪存技术的发展一直在稳步向前发展。主机设备解决方案提供商和存储设备制造商之间的合作促进了标准化接口的建立,这些接口被遵循并共同构建,直到今天的生态系统。

两个最著名的公开接口标准是开放式 NAND 闪存接口 (ONFI) 和 Toggle 标准,每个标准均由其各自享有盛誉的工作组开发并不断扩展。虽然两个标准之间可以进行对比和比较,但公认的“共同点”是联合电子器件工程委员会 (JEDEC) 发布的 JESD230 标准,开发人员可以从该标准中提取该标准作为参考套。

每套标准的独特发展通过命令、寻址、计时、格式化和物理配置方面的差异显而易见,这是由于闪存和存储行业领导者群体的不同范围和知识所形成的。尽管如此,这两个标准都在努力实现不同技术之间的兼容性和互操作性方面具有凝聚力。

遗留接口

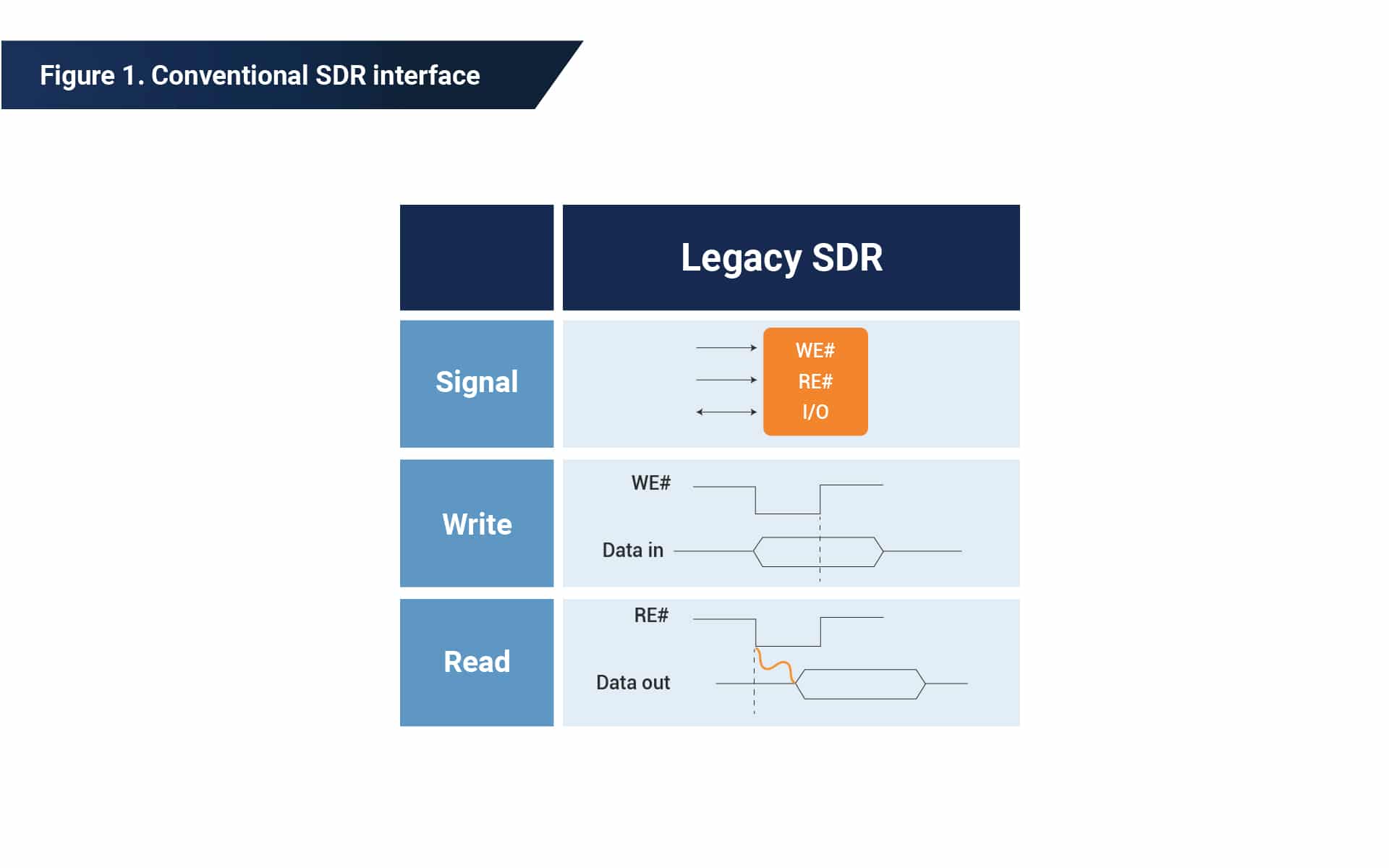

深入研究闪存接口知识库,您可以立即识别同步和异步数据传输方案之间的比较。第一个 NAND 闪存设备接口(称为 Legacy)被配置为利用与数据传输时序标准相关的异步传输方案。为了增强信号完整性和准确性,使用同步方案来控制需要与连续时钟信号同步的信号。异步方案允许传输任务的触发完全依赖于“写使能(WE)”和“读使能(RE)”控制信号,而不需要时钟。

此外,Legacy 支持单数据速率 (SDR) 数据传输,仅在控制信号的一个边沿处理数据传输。具体来说,当数据“移入”和移出设备时,该接口仅在写入信号的上升沿和读取信号的下降沿强制执行制定的信号对齐。

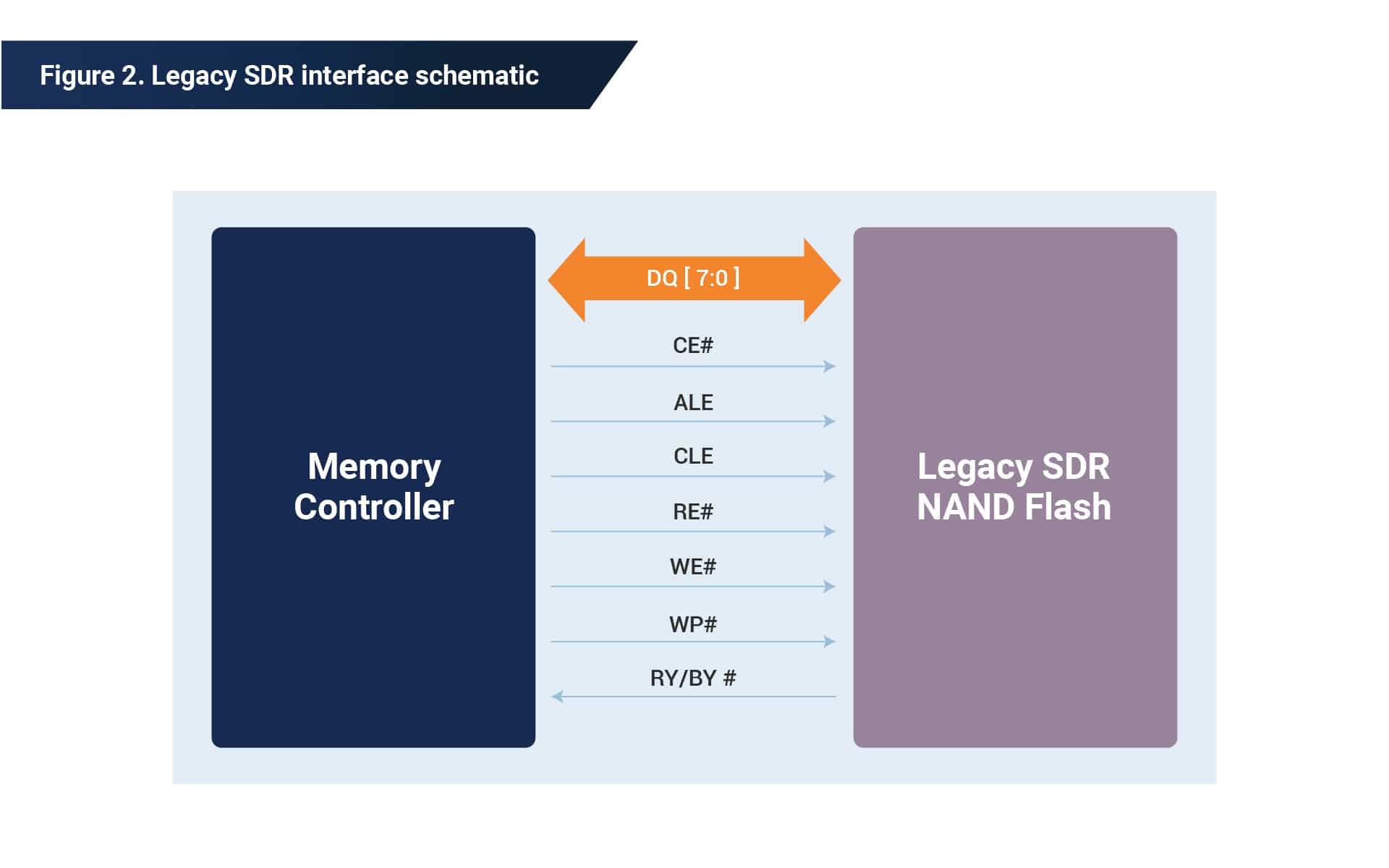

除了用于 I/O 信号 (DQ) 的 8 位 (b) 双向数据总线外,15 引脚接口还具有 7 个控制信号引脚,可在 25 纳秒 (ns) 的传输时间内完成字节 (B) 的传输)。基于此属性,最大带宽可计算为每个数据引脚 40MB/s 或 40Mb/s。 (1B/25ns = 0.04×109 B/s = 40 MB/s,1B = 8b)

ONFI接口

2006年,一大批科技公司成立了开放式NAND闪存接口(ONFI)工作组,其中包括SK海力士、英特尔、美光、闪迪、群联、索尼等。同年晚些时候,第一版ONFI标准起草并发布,旨在提供一个统一的标准,以应对闪存市场的无组织性(源于存储产品、闪存供应商和下游之间闪存接口标准不一致)产品制造商)。

多方面的 ONFI 标准阐明了市场迫切需要的适当接口的关键方面,包括但不限于功能特征、功能/命令集调节、信号描述/时序条件、行为流程以及寄存器级/物理规范。今天,ONFI 工作组继续发布更新以扩展标准集,最新草案是 2021 年的 ONFI 5.0。

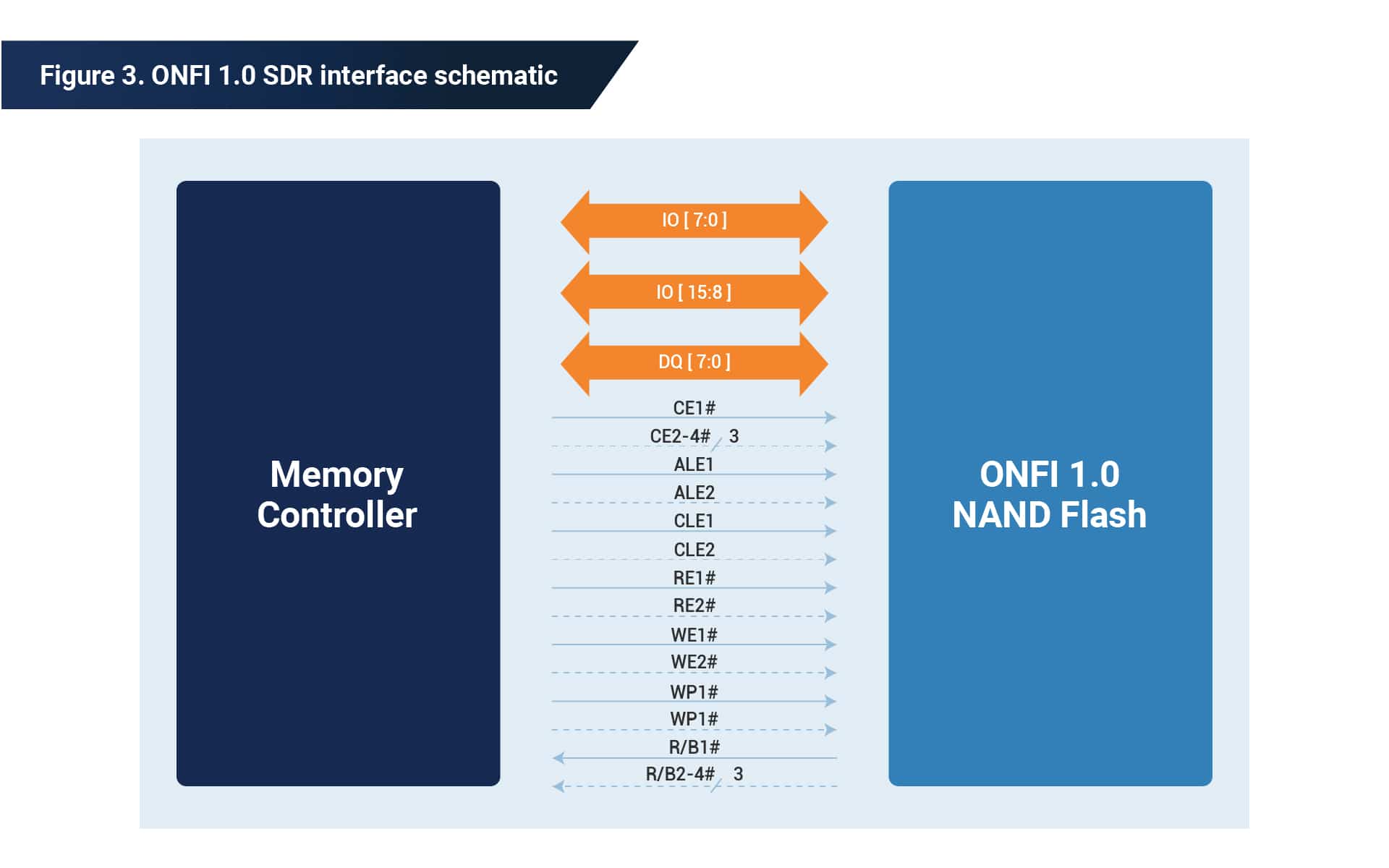

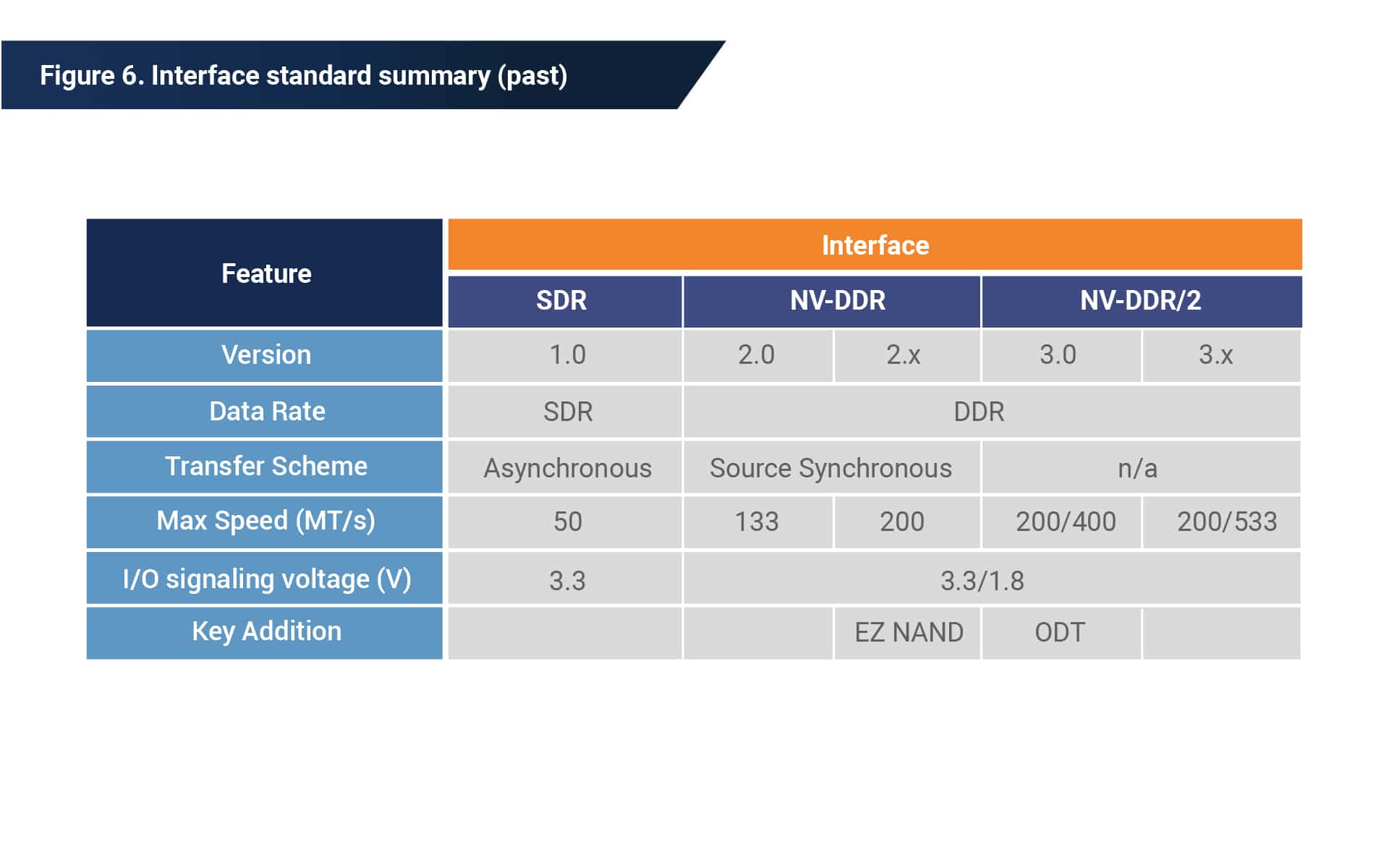

网络FI 1.0

第一个版本的主要目的是提供从旧版本扩展的快速接口标准化。在采用异步 SDR 传输方案的同时,1.0 版本描述了类似于传统传统的电气接口,但可选择支持尖端技术,例如具有控制信号放大功能的 16 位数据总线。 50MB/s 的带宽标志着 20% 比 Legacy 之前的 40MB/s 性能有了改进。

网络FI 2.0

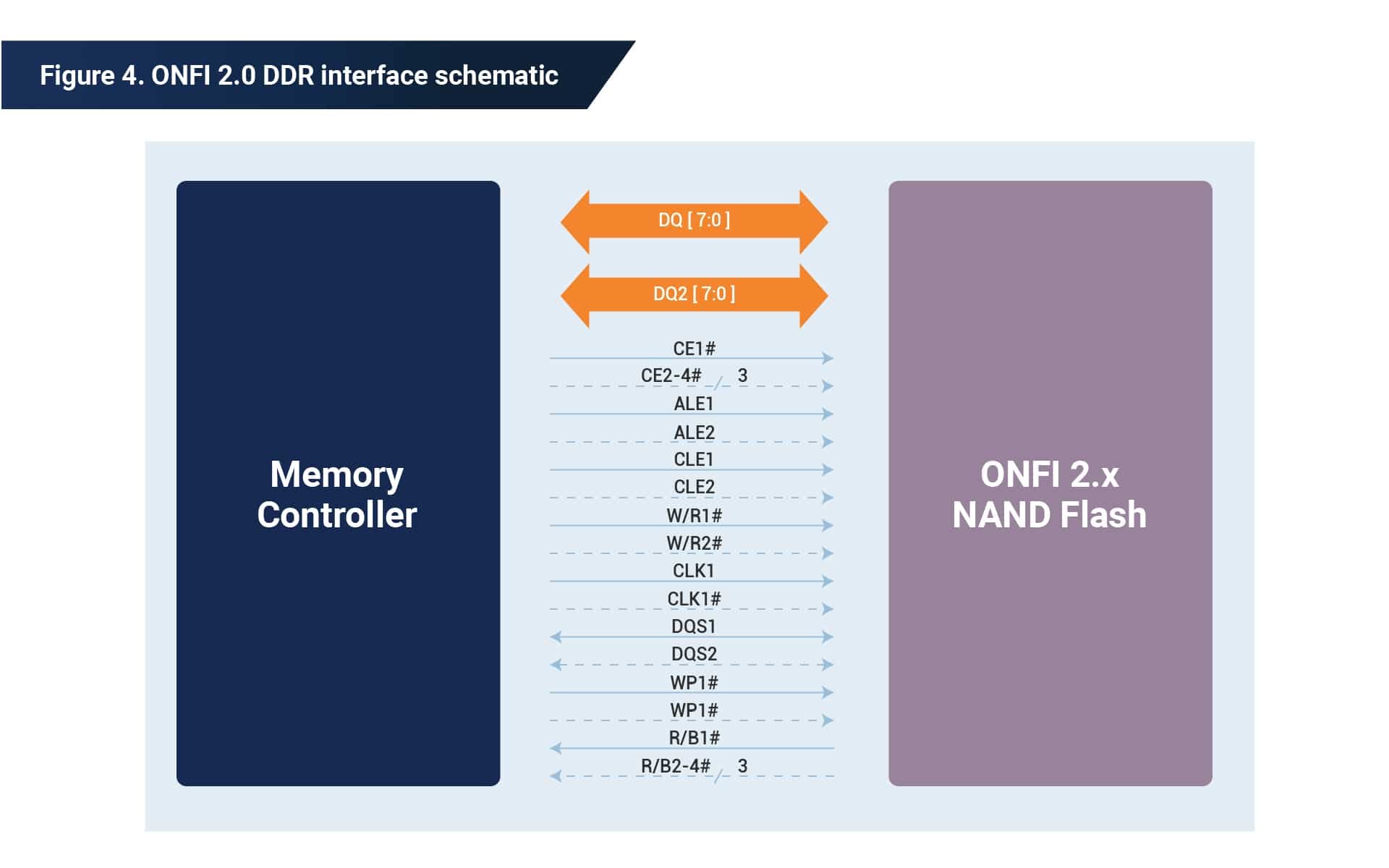

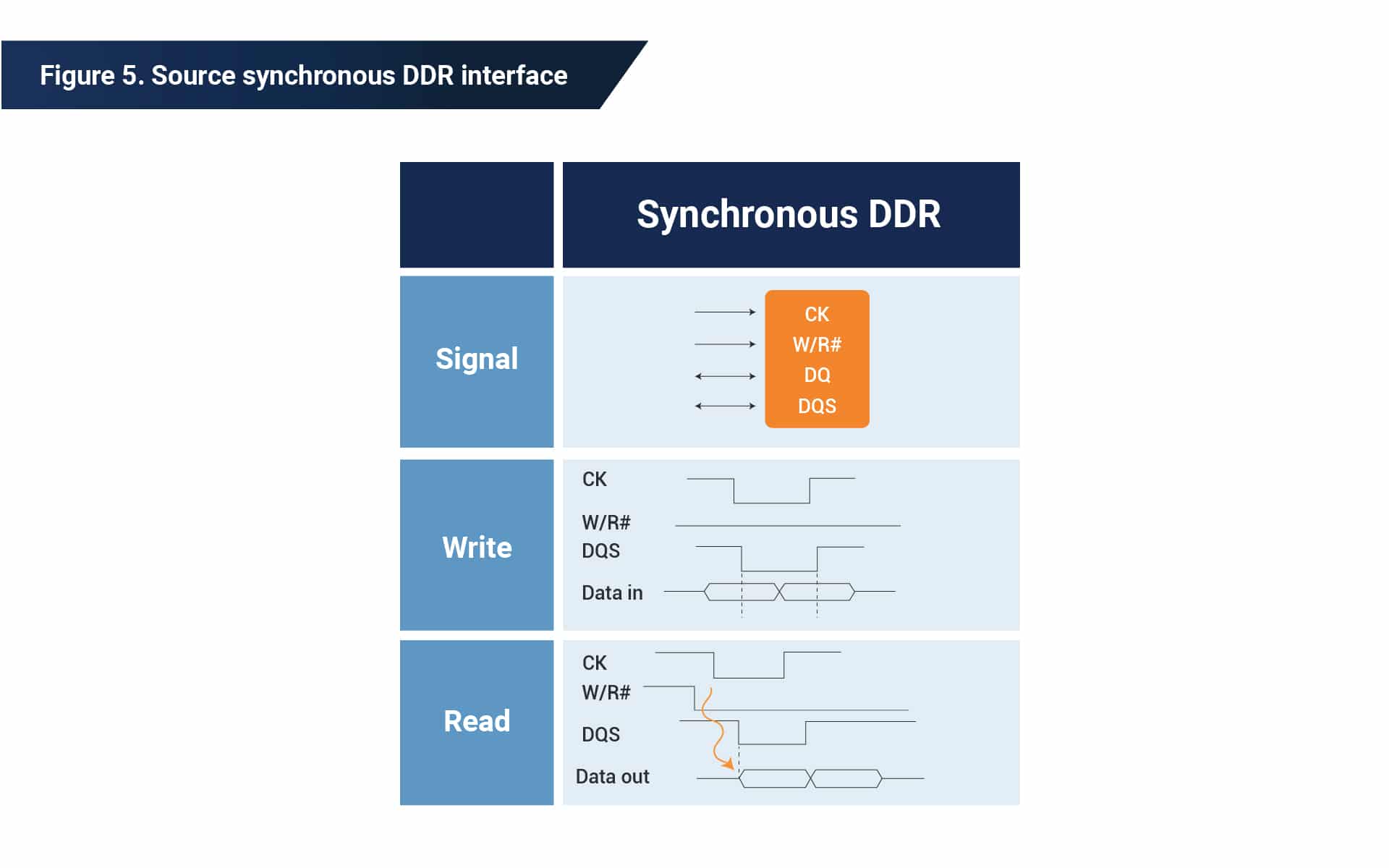

ONFI 2.0 于 2008 年 2 月发布。最重要的变化是采用了双倍数据速率 (DDR) 传输方案,该方案允许在控制信号的两个边沿上进行数据传输,从而大幅提高设备最大吞吐量。此外,ONFI标准将本规范中的DDR闪存接口修正为NV-DDR(非易失性DDR)接口,使其与随机存取存储器(RAM)使用的易失性存储器DDR接口区分开来。

尽管NV-DDR保留了异步工作方案以向后兼容之前的SDR修订版,但仍进行了调整以支持源同步方案。具体而言,前WE控制信号成为时钟信号(CLK),而RE控制信号成为选择读写操作的方向信号。此外,现在数据在新添加的数据选通信号 (DQS) 的上升沿和下降沿上进行传输,以实现高达 133MT/s 的双倍传输速率。吞吐量的增加迅速解决了更大尺寸数据传输和随机性能改进的趋势。

网络接口2.1

ONFI 2.1 于 2009 年获得批准,并对 2.0 修订版的多个部分进行了扩展。 2.1 标准除了提供操作灵活性空间的新功能外,还使最大传输速率升级至 200MT/s。

ONFI 规范中的多个部分得到了扩展,首先是报告纠错编码 (ECC) 功能的扩展参数页。作为修订版 2.1 中的关键补充,扩展 ECC 信息允许在 ECC 参数与其他设备参数(例如有效块数量和支持的编程/擦除周期数量)的指定配对下对 NAND 设备采用多种有效使用方法。

转向内存组织,交错寻址和逻辑单元号 (LUN) 的引入除了减少封装引脚(特别是芯片使能引脚)之外还开辟了工程机会,从而减少了复杂硬件设计的冗余。

“小数据移动”和“更改行地址”作为设备控制命令引入。 “小数据移动”命令通过缩小设备控制命令中的数据块来解决低端消费应用程序的 ECC 限制。 “更改行地址”命令旨在通过提高设备操作灵活性来减少工作负载开销。

网络接口2.2

基于先前版本的更改,ONFI 2.2 于 2009 年底发布,并提供了有关内存组织的附加指南。规定了对先前引入的交错寻址的限制,并添加了针对各个 LUN 的重置命令。该修订还在规范的附录中定义了当前的测量方法。

网络接口2.3

ONFI 2.3 于 2010 年 8 月在闪存峰会 (FMS) 上发布,重点关注 EZ-NAND(ECC 零 NAND)协议。该协议建议将ECC管理单元从存储控制器侧转移到闪存侧,从而减轻负担过重的控制单元的压力。

ONFI 3.x

ONFI 3.0于2011年3月发布,支持传输速率高达400MT/s,适合当时青睐的8K页面数据对齐大小增加趋势。吞吐量升级还伴随着信号电压降低至 1.8 伏,作为功耗优化的一步。

许多其他新功能的推出提高了闪存创新的上限。片上端接 (ODT) 是本规范修订版中最具影响力的补充,它是一种通过允许控制器打开和关闭封装内独立或所有器件的端接电阻来提高内存通道信号完整性的设计。 。此版本中详细解决了 ODT 等多芯片封装功能,以管理精细的芯片级操作和行为。

其他功能包括卷寻址增强和所需芯片使能引脚数量的减少,从而提高了电路布线效率。然而,随着版本 3.2 的发布,传输速率升级再次成为人们关注的焦点,NV-DDR2 接口下的吞吐量达到 533MT/s,这在当时使同代设备中的闪存升级合法化。

ONFI 4.0

ONFI 4.0 规范于 2012 年推出,将以前已知的 NV-DDR2 的传输速率升级至 667 MT/s,将新推出的 NV-DDR3 的传输速率升级至 800MT/s。引入了一种称为 ZQ 校准的技术作为 ODT 辅助工具来校准终端电阻。该规范限制了电压或温度变化时信号完整性的损害。此外,这些增强功能使 I/O 电源 (VCCQ) 要求降至 1.2 伏,从而改善功耗。

ONFI 4.x

从 4.0 版开始扩展的 ONFI 规范包含了多项变化,包括电源配置灵活性、补贴功能参数定义以及额外的物理引脚分配选项。

从ONFI 4.1开始,核心控制电压(VCC)的选项开放为2.5伏,并在原来的3.3/1.8/1.2设置的基础上增加了从2.35伏到3.6伏的一系列配置。

在 ZQ 校准之上添加了占空比校正 (DCC) 和 DQ 读/写训练,作为在初始化过程中促进 NAND 器件调整的功能。此更改专门针对运行速度超过 800MT/s、工作负载繁重的设备。 DCC 训练的目的是补偿“读启用补充”信号(“读启用”信号的补充信号)的潜在占空比不匹配。这

DQ 培训旨在尝试将 DQS 和 DQ 信号与主机端系统保持一致。

在 4.2 版本中,对 DCC 培训规范的细节进行了修改,同时物理引脚分配选项也发生了其他变化。具体来说,252 球球栅阵列 (BGA) 分配加入了以前的 BGA-272 和 BGA-316 分配,作为物理接口的新选项。

光网络FI 5.0

ONFI 5.0 于 2021 年初发布。新发布的标准规范中还揭示了另外三个引脚分配选项,以及正确采用所需更改的说明。但更重要的是NV-LPDDR4接口,强调降低整体功耗,同时提高每个接口的传输速率,即NV-DDR2为800MT/s,NV-DDR3和NV-LPDDR4高达2400MT/s。由于传输速率提高,支持 NV-LPDDR4 的设备可以利用数据总线反转 (DBI) 功能,通过控制信号方向和电流量来限制功耗。

另一方面,NV-LPDDR4的到来引发了ODT功能修改的又一次推动。 ODT 禁用/启用和通道 ODT 等附加功能解决了新 NV-LPDDR4 接口对 ODT 的潜在影响。

在启用 NV-LPDDR4 时,NAND 器件和控制器之间的内部参考电压可能会处于未经训练的状态,但 ODT 引起的小信号摆幅可能会导致命令序列失败。因此,正确定时禁用/启用 ODT 可以显着影响新接口下的操作。

除了这种类似开关的功能之外,通道 ODT 设置还可以控制 NAND 输出上拉电阻的强度,从而控制信号终端电阻。换句话说,该设置实质上允许主机端在数据输出操作期间决定每个通道内的最佳ODT强度。同时,NAND 器件会根据供应商特定的设置值进行相应调整。

切换界面

在 ONFI 1.0 发布后的第二年,世界领先的两家 NAND 闪存制造商三星半导体和东芝存储器公司 (TMC) 推出了 Toggle 接口标准,作为驱动闪存设备操作超越传统功能的替代方案。使用 Toggle 接口的设备还在各种硬件配置、信号模式和电气特性中按照一组可扩展、精心编织的准则进行操作。 Toggle 标准的演变发生在三星和 TMC 向客户特定发布的 NAND 设备规范中,而不是向公众发布。这与 ONFI 标准形成鲜明对比,ONFI 标准是根据其工作组的统一公开版本进行更新的。

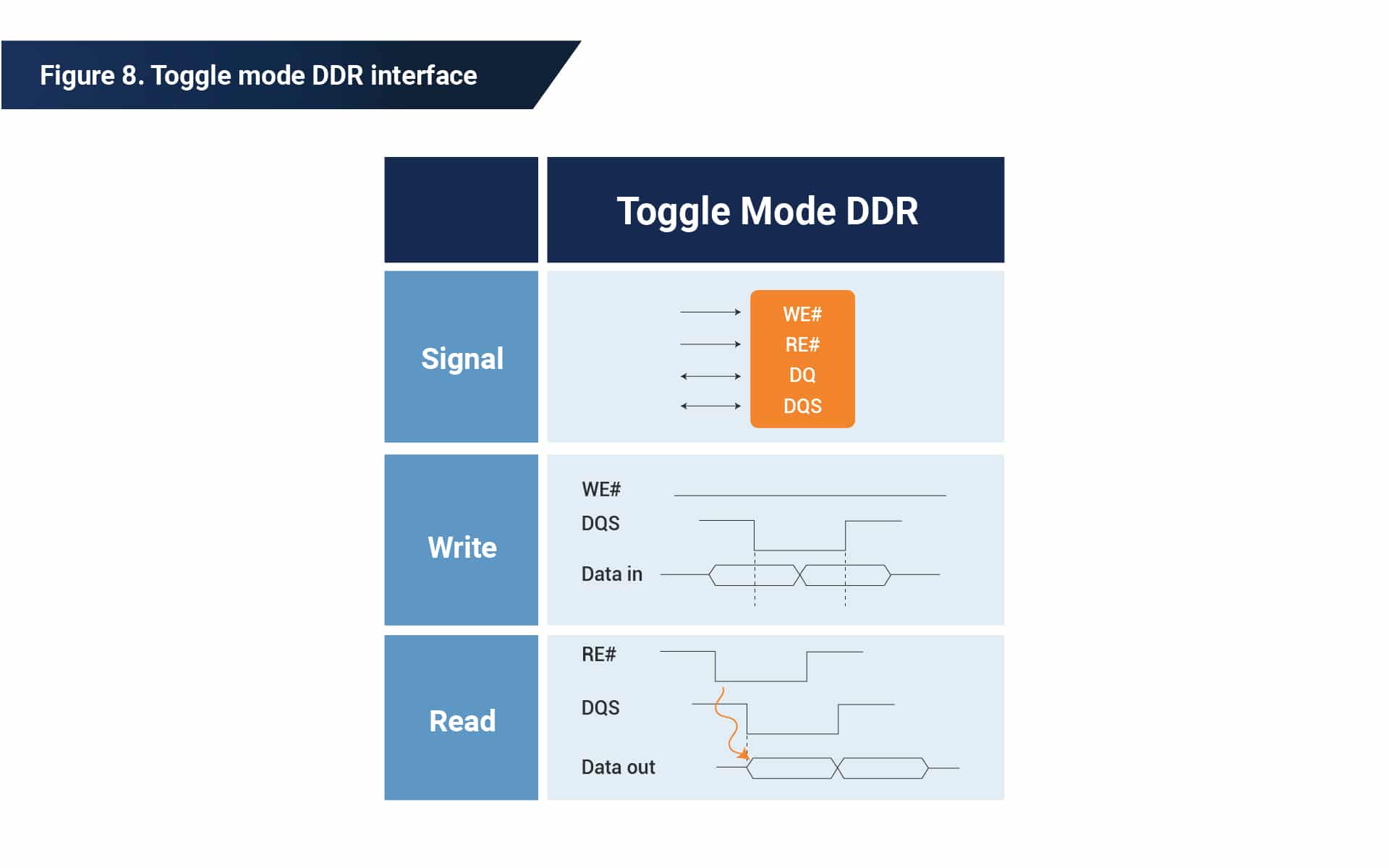

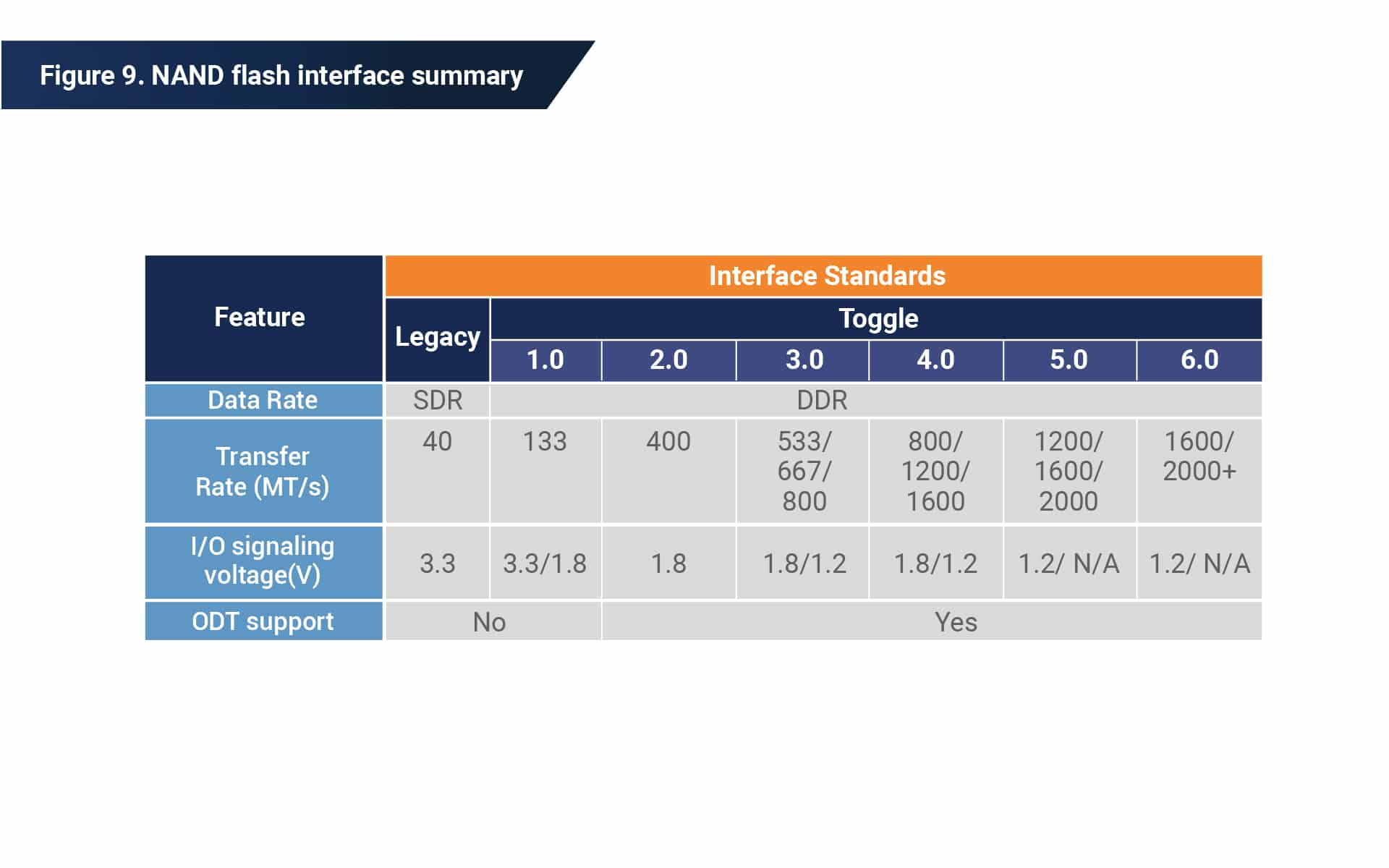

切换1.0

乍一看,第一代 Toggle DDR 接口具有与 ONFI 2.0 修订版相同的一般特征。 Toggle 1.0 使用双向 DQS 选通信号实现高达 133MT/s 的数据传输速率,每个上升沿和下降沿都与一次数据传输相关。然而,ONFI和Toggle之间的区别在于,Toggle数据传输在没有时钟信号的情况下进行操作,使其仅在读写操作发生时与功耗异步。 ONFI 在 3.0 版本中也采用了这种实现方式,以其在功效方面的优势和设计简单性。

切换 2.0 / 3.0 / 4.0

Toggle 2.0 支持的设备允许吞吐量高达 400 MT/s,与在 ONFI 3.0 下运行的设备相当。然而,根据发布时间,只有部分 Toggle 2.0 设备支持 ODT 功能。

虽然 Toggle 3.0 设备于 2015 年推出,支持 533MT/s 和 667MT/s 的传输速率选项,并完全支持 ODT 和 ZQ 校准功能,但主流的 Toggle 标准修订版是 Toggle 4.0 标准。在其最早版本中,Toggle 4.0 接口可实现高达 800MT/s 和 1200MT/s 的传输速率,同时支持与 ONFI 匹配的必要功能,但根据产品的不同,插图也有所不同。

当然,接口标准是针对最新的 NAND 闪存技术而设计的,即 Kioxia(以前称为 TMC)和 Western Digital 的 BiCS 系列,以及三星和 SK Hynix 等韩国供应商的 V-NAND 系列。事实上,随着新的闪存设计和技术的推出,闪存供应商已经能够通过在同一代接口中反复试错来校准闪存行为来调整传输速率。群联一直与其闪存供应商合作伙伴合作,以实现传输速率突破 2000MT/s 以上,并在系统前端性能面临下一代互连挑战的最佳时机进行各种设计改进。

切换 5.0 / 6.0

随着开发人员孜孜不倦地构建闪存接口标准手册中的构建块,未来是光明的。随着3D闪存技术正式进入百层堆叠时代,业界正在期待向更快、更前沿的接口交换速度过渡。不久之后,Toggle 5.0 和 6.0 接口预计将以高于 2400 MT/s 的传输速率运行,即每个芯片的传输速率高于 250 MB/s。随着闪存拓扑和设计变更讨论的持续进行,业界预计会有更多功能添加和改进,以推进主流标准。

NAND闪存的未来

在过去的20年里,ONFI和Toggle NAND闪存接口蓬勃发展,并被公认为开发NAND闪存应用的行业标准。截至 2021 年,这两个标准的最新版本已将 NAND 闪存性能提升至传统传统功能的十倍以上,同时实现更高的模块容量并降低功耗。群联电子拥有 1900 多项全球专利和 20 年闪存行业经验,已准备好提供内存控制器支持,以满足两种主要接口下任何应用程序的需求。