本文是系列文章的第三篇,也是最後一篇,該系列深入探討了群聯最重要的產品之一:積體電路 (IC)。 我們的第二期 介紹了基本的 IC 設計流程,並展示了 NAND 快閃記憶體控制器 IC 功能框圖。在最後一篇文章中,我們將帶您進一步進入群聯 IC 設計世界。

正如我們在我們的 上一篇文章 關於 IC 設計,重要的是「圍繞」目標應用來設計 IC。為此,設計人員必須了解電路需要實現的功能。只有這樣,他們才能整理出一份詳細規範列表,以緊密解決功率參數、記憶體容量、閾值、環境適應性等定量和定性變數。

根據預期的用例和應用,特定的功能塊和要求可能會大不相同。然而,一些通用功能塊可以在特定應用的設計中通用。為了說明這一點,在我們討論快閃記憶體控制器之前,讓我們先來看看一些人工智慧和 5G 應用的 IC 設計範例。

AI 與 5G 應用的 IC 設計

對於許多以人工智慧應用為中心的 IC,一個關鍵的功能區塊是數位訊號處理 (DSP) 引擎。這是一個硬體引擎,負責執行矩陣乘法和卷積等演算法所需的複雜數學運算,這些是電腦機器學習和深度學習期間經常大量發生的計算的基本步驟。

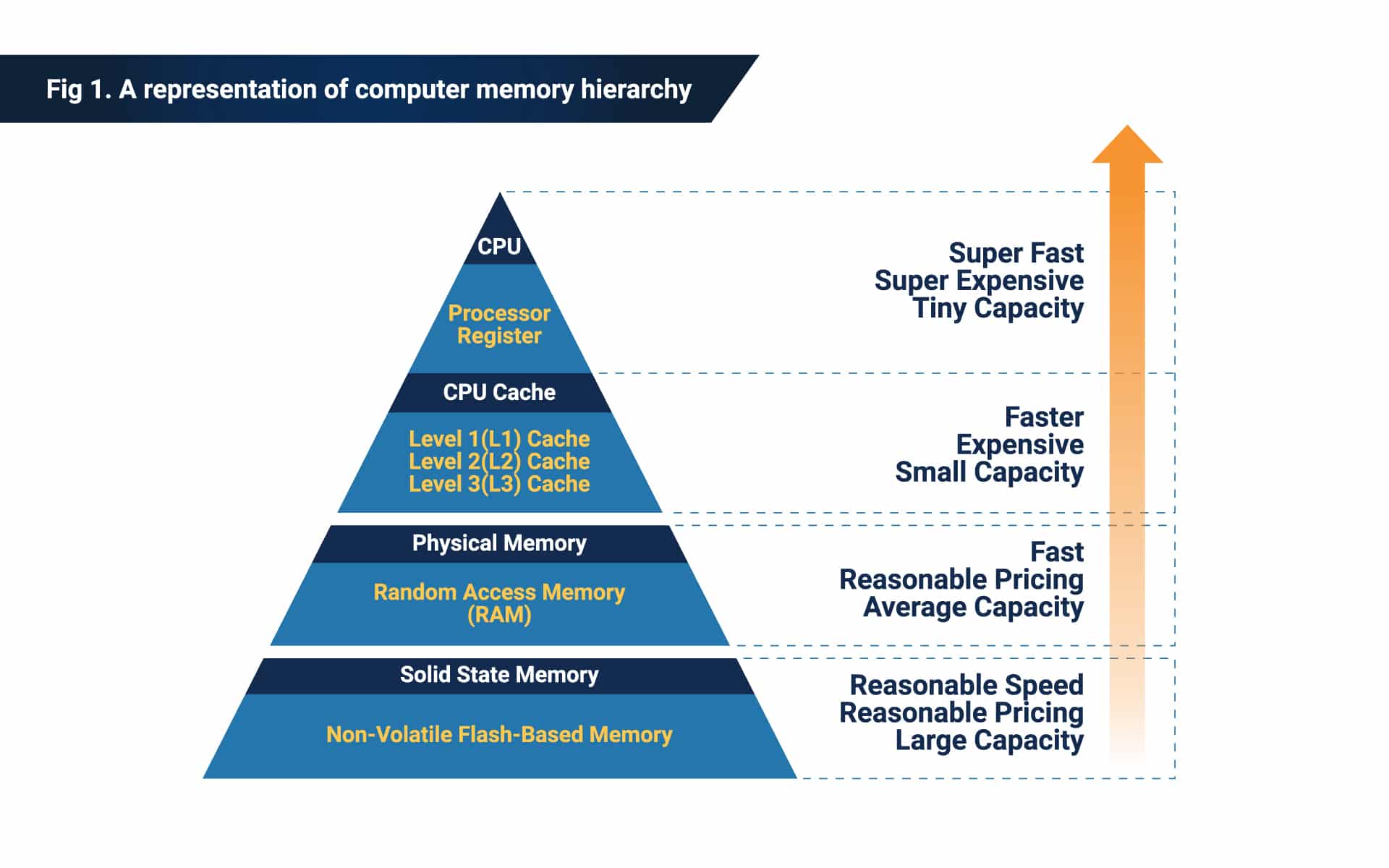

計算系統中計算端的另一面是記憶體端。每個計算系統都需要某種硬體空間來暫時儲存中間參數或計算結果。對於人工智慧應用來說,計算和訓練之間產生的臨時資料能夠快速檢索或保存起來以供以後使用至關重要。因此,大多數為人工智慧應用設計的 IC 晶片都需要頂級的內存硬體和良好的內存接口,以便做出快節奏的決策,同時配備大量寄存器,能夠以極快的速度存儲單個位數據。

除了處理和資料儲存所需的速度之外,一些額外的速度也很有價值,因為以人工智慧應用為中心的 IC 通常配備所謂的「硬體加速器」來支援神經網路推理等高要求的工作負載。這些加速器通常是附加到主處理器的專用電路,這些處理器通常很忙並且因更大的任務而消耗大量資源,以並行執行特定的計算任務。加速器的這種卸載效果有助於提高晶片效率,同時減少主處理器內任務之間切換所造成的能耗和延遲,有助於提高人工智慧應用的整體效能。

再舉一個例子,讓我們考慮一下以 5G 應用程式為中心的 IC。此類 IC 的重點主要是實現高速無線連接和資料傳輸。設計中的關鍵功能區塊可包括負責對無線訊號進行編碼和解碼的數位基頻處理單元,以及負責無線通訊期間所需的天線和類比訊號收發的射頻 (RF) 前端。

此外,為 5G 設計的 IC 通常支援波束成形等高級功能,可透過多個天線的控制將無線訊號引導至特定裝置。為了實現此類控制機制,必須在電路內實現 MIMO(多輸入、多輸出)功能塊,以正確引導來自多個天線的訊號序列。

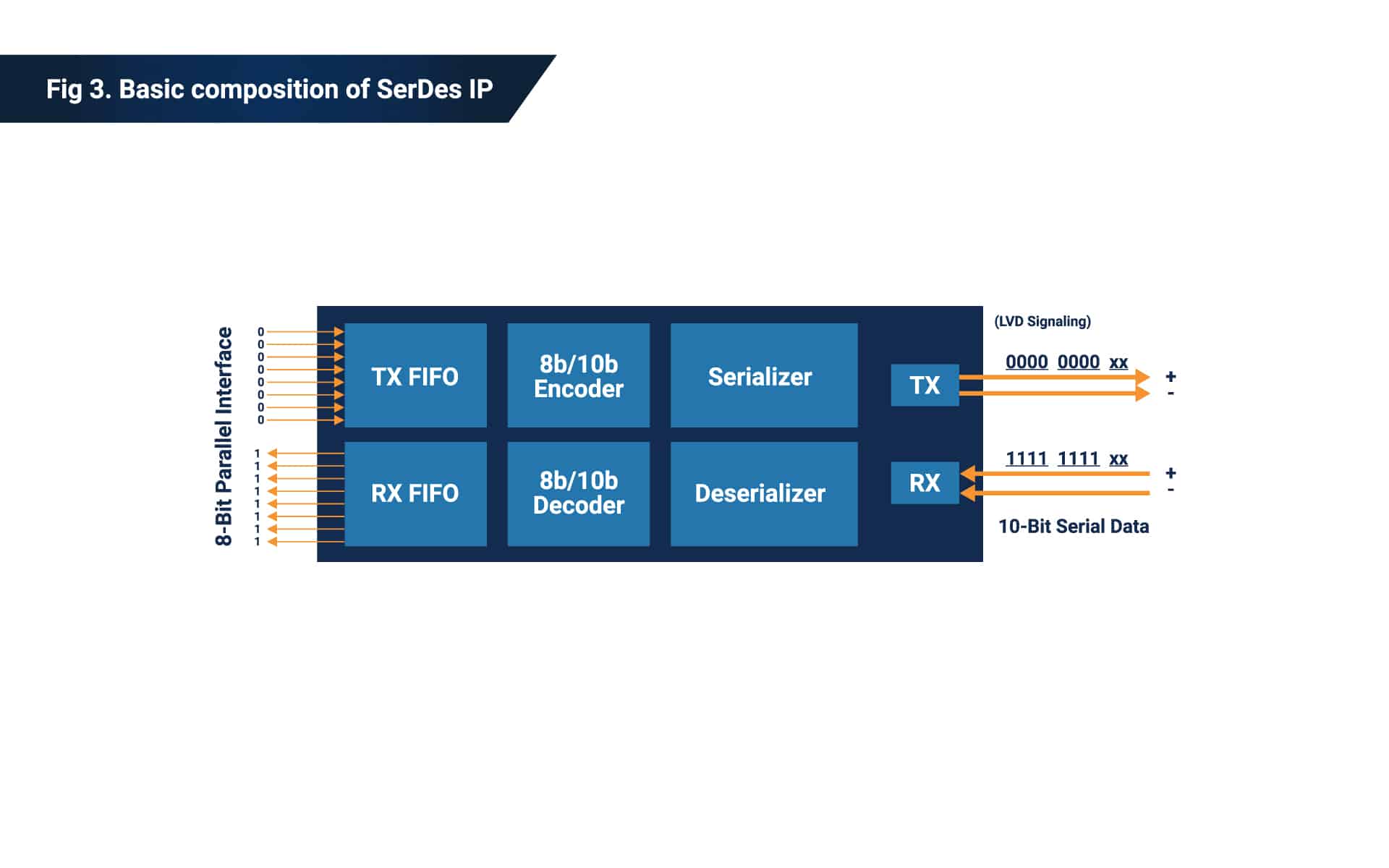

儘管目標應用存在差異,但用於設計 IC 的某些方面和流程在看似不同的 IC 類型之間創建了相關性。例如,人工智慧 IC 和快閃記憶體控制器 IC 都需要高效的記憶體介面才能達到最佳效能。差別僅在於附屬記憶體設備位於記憶體層次結構中的位置。就 5G IC 而言,強大的 MIMO 訊號系統的設計與用於控制 NAND 快閃記憶體儲存前端中的資料流的先進先出 (FIFO) 緩衝區的實現有著微妙的相似之處。雖然這兩種設計之間沒有直接聯繫,但它們都涉及不同的緩衝器電路,這些電路透過操縱輸入產生所需的輸出。

SSD 快閃記憶體控制器的 IC 設計

通用 SSD NAND 快閃記憶體控制器 IC 包含特定功能區塊,例如:

-

-

- 前端互連

- 中央發動機

- 緩衝區和儲存媒體管理單元

- 外圍互連

- 用於可靠性保證和安全功能的多個加密引擎

-

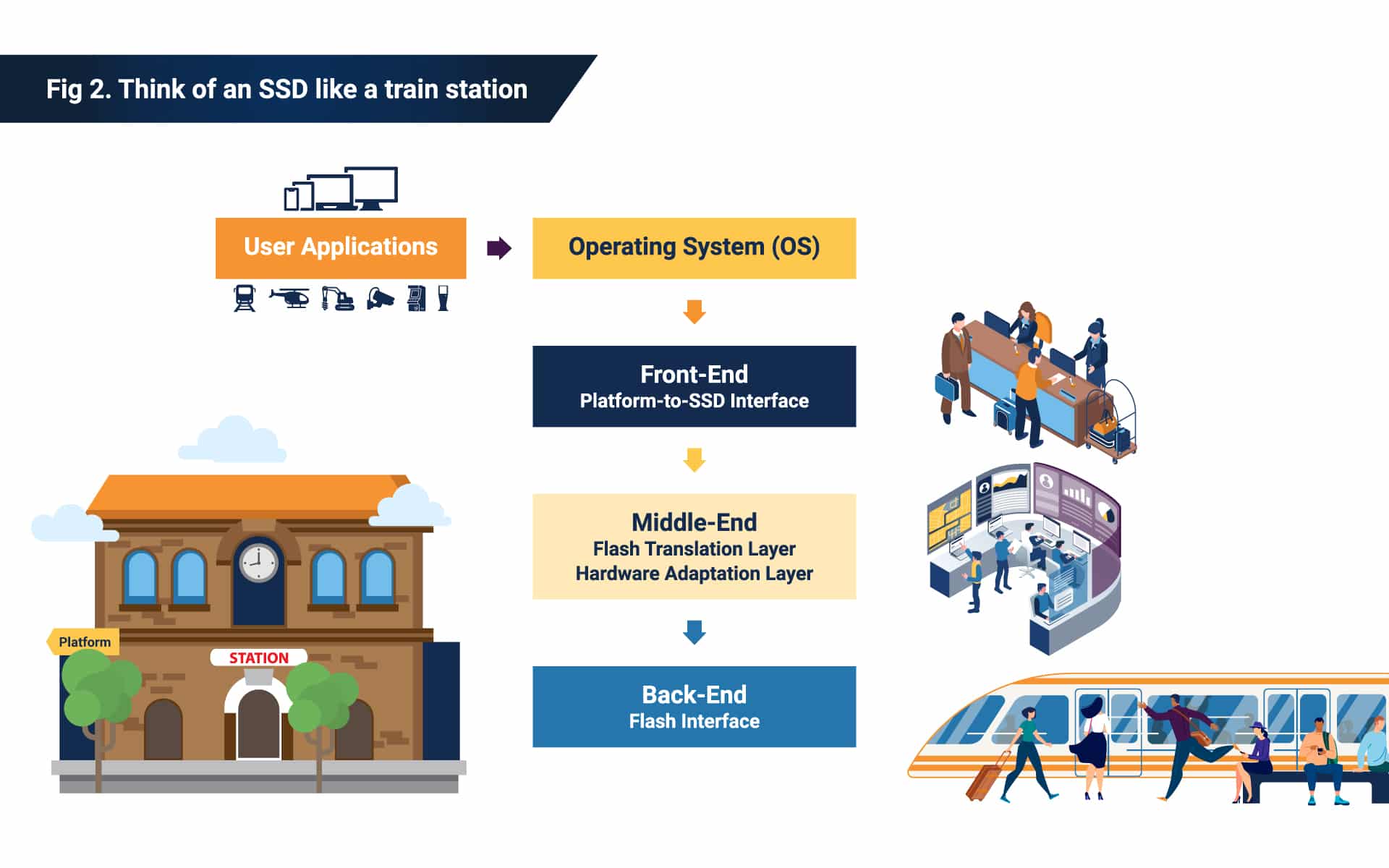

這些區塊協同工作,確保 SSD 作為可靠的資料儲存設備高效運作。為了更好地說明這是如何發生的,我們將使用火車站進行類比。就像火車站內有不同的區域或區域供旅客使用一樣,SSD 提供資料服務的操作也可以分為幾個部分:前端、中端和後端。

前端

將 SSD 的前端想像成火車站的前廳。與車站大廳的服務包括票務、行李寄存甚至清潔服務類似,SSD 的前端充當資料的入口點,為傳入訊號提供許多初步處理服務。這些服務包括透過目標傳輸介面(可能是 SATA、SAS 或 PCIe)建立訊號鏈路、遵守協議的數位訊號轉換以及各種連接驗證例程。

為了提供這些服務,許多通用和專利微型電路(通常縮寫為 IP)必須封裝到 NAND 快閃記憶體控制器 IC 晶片上。 Phison 自有 SSD 控制器解決方案上的前端 IP 的一個例子是 串行解串器 (串列和解串器的縮寫)負責將傳入的平行資料位元(意味著它們同時透過不同的實體引腳傳入)轉換為序列位元流,反之亦然。 SerDes 的組成包括一個用於資料流管理的 FIFO 快取以及一對用於協定一致性的編碼器。群聯擁有針對主流SSD傳輸介面的全面SerDes IP組合,基於業界最佳的奈米級生產製程構建,為其SSD前端提供全面支援。

中端

中台主要負責快取和儲存媒體管理。 SSD 內部有兩個關鍵的記憶體元件:DRAM 和 NAND 快閃記憶體。 DRAM作為快取空間,可以放置臨時數據,NAND快閃記憶體作為儲存介質,可以長期儲存資料。中端對於SSD來說非常重要,它是系統的中心。就像火車站調度員或播音員引導乘客到臨時候車區或長途旅行的火車一樣,SSD IC 將資料引導到 DRAM 進行臨時儲存或 NAND 快閃記憶體進行長期儲存。

為了完成中央調度辦公室的工作,必須實施快閃記憶體轉換層 (FTL) 和硬體適配層,以協作處理儲存裝置上的資料放置。 FTL 負責將其帳本上的資料對應到快閃記憶體上的正確實體位置。同樣,臨時資料到DRAM也採用類似的表管理和映射機制。 FTL 和硬體適配層都是關鍵的韌體功能,可嚴重影響 SSD 的整體效能。它們由強大的中央硬體引擎驅動,必須在控制器 IC 的設計中精心規劃。

為了滿足中階的需求,群聯擁有許多硬體IP,可以提供獨特的方式來協助中央調度員。它們包括 CoX處理器™ 和 記憶體介面 IP 這使得群聯的 NAND 快閃記憶體控制器 IC 的每一代產品都優於其他產品。

後端

NAND 快閃記憶體控制器 IC 的後端全部與 NAND 快閃記憶體有關。如前所述,NAND 快閃記憶體晶片就像我們火車站類比中的火車。就整體旅行體驗而言,列車內服務與車站提供的幫助和指示同樣重要。 NAND 快閃記憶體控制器 IC 設計的很大一部分集中在這些列車內服務,其中包括 NAND 介面協定符合性、耐久性維護和糾錯。

NAND快閃記憶體控制器符合NAND快閃記憶體介面協定的能力就像擁有一位熟練的火車司機,可以完美且有效率地操作不同的火車模型。群聯擁有強大的IP組合,相容於主流協定ONFI和Toggle的最新介面規範。憑藉累積的硬體和韌體 IP,群聯的 NAND 快閃記憶體控制器 IC 能夠輕鬆流暢地驅動 NAND 快閃記憶體。

正如我們在旅行中所經歷的那樣,有時我們會在找到座位甚至登上正確的火車時犯錯誤,NAND 快閃記憶體中電子形式的數據也是如此。由於其固有的物理特性,電子有時會從 NAND 快閃記憶體單元中逸出,這可能會導致操作期間和隨著時間的推移出現資料位元錯誤。因此,保持NAND快閃記憶體的高耐用性和可靠性是良好的NAND快閃記憶體控制器IC後端設計的另一個關鍵要求。

選擇群聯 IC 以獲得高可靠性和品質

群聯 從市場上選擇最優質的 NAND 快閃記憶體解決方案,以確保其高端 SSD 產品擁有最佳的固有使用壽命,並且該公司透過強大的先進產品組合鞏固了其品質傳統。 糾錯碼 (ECC)。就像專業且樂於助人的火車服務人員協助乘客一樣,群聯先進的 ECC 基於幾代不斷改進的韌體演算法和專用數學計算的硬體引擎,可以輕鬆處理這些逃逸的電子和 NAND 閃存位錯誤。