本文是系列文章的第三篇,也是最后一篇,该系列深入探讨了群联最重要的产品之一:集成电路 (IC)。 我们的第二期 介绍了基本的 IC 设计流程,并展示了 NAND 闪存控制器 IC 功能框图。在最后一篇文章中,我们将带您进一步进入群联 IC 设计世界。

正如我们在我们的 上一篇文章 关于 IC 设计,重要的是“围绕”目标应用来设计 IC。为此,设计人员必须了解电路需要实现的功能。只有这样,他们才能整理出一份详细规范列表,以紧密解决功率参数、内存容量、阈值、环境适应性等定量和定性变量。

根据预期的用例和应用,特定的功能块和要求可能会有很大差异。然而,一些通用功能块可以在特定应用的设计中通用。为了说明这一点,在我们讨论闪存控制器之前,让我们先看一些人工智能和 5G 应用的 IC 设计示例。

AI 和 5G 应用的 IC 设计

对于许多以人工智能应用为中心的 IC,一个关键的功能块是数字信号处理 (DSP) 引擎。这是一个硬件引擎,负责执行矩阵乘法和卷积等算法所需的复杂数学运算,这些是计算机机器学习和深度学习期间经常大量发生的计算的基本步骤。

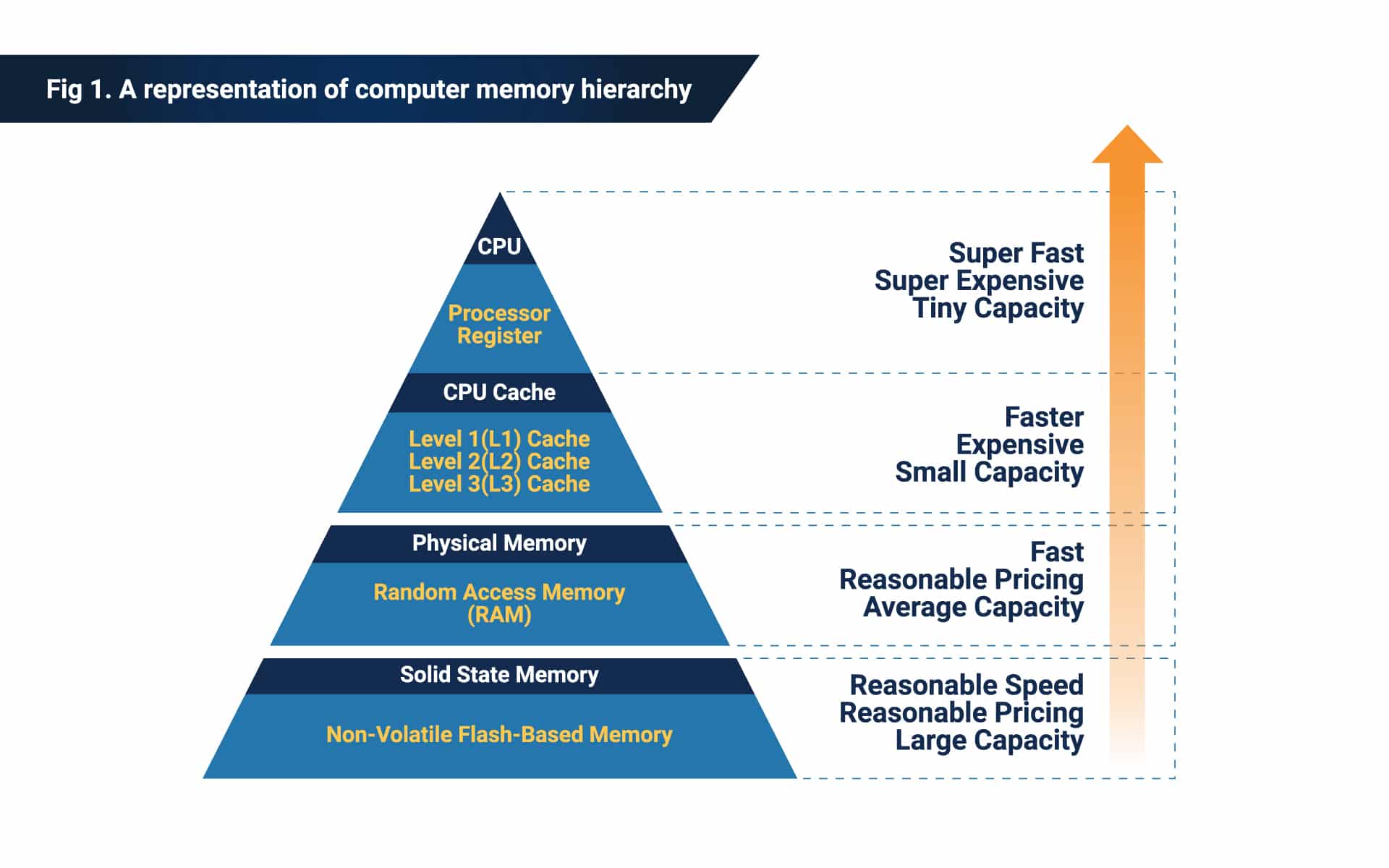

计算系统中计算端的另一面是内存端。每个计算系统都需要某种硬件空间来临时存储中间参数或计算结果。对于人工智能应用来说,计算和训练之间生成的临时数据能够快速检索或保存起来供以后使用至关重要。因此,大多数为人工智能应用设计的 IC 芯片都需要顶级的内存硬件和良好的内存接口,以便做出快节奏的决策,同时配备大量寄存器,能够以极快的速度存储单个位数据。

除了处理和数据存储所需的速度之外,一些额外的速度也很有价值,因为以人工智能应用为中心的 IC 通常配备所谓的“硬件加速器”来支持神经网络推理等高要求的工作负载。这些加速器通常是附加到主处理器的专用电路,这些处理器通常很忙并且因更大的任务而消耗大量资源,以并行执行特定的计算任务。加速器的这种卸载效果有助于提高芯片效率,同时减少主处理器内任务之间切换所造成的能耗和延迟,从而有助于提高人工智能应用的整体性能。

再举一个例子,让我们考虑一下以 5G 应用为中心的 IC。此类 IC 的重点主要是实现高速无线连接和数据传输。设计中的关键功能块可包括负责对无线信号进行编码和解码的数字基带处理单元,以及负责无线通信期间所需的天线和模拟信号收发的射频 (RF) 前端。

此外,为 5G 设计的 IC 通常支持波束成形等高级功能,可通过多个天线的控制将无线信号引导至特定设备。为了实现此类控制机制,必须在电路内实现 MIMO(多输入、多输出)功能块,以正确引导来自多个天线的信号序列。

尽管目标应用存在差异,但用于设计 IC 的某些方面和流程在看似不同的 IC 类型之间创建了相关性。例如,人工智能 IC 和闪存控制器 IC 都需要高效的内存接口才能实现最佳性能。区别仅在于附属存储器设备位于存储器层次结构中的位置。就 5G IC 而言,强大的 MIMO 信号系统的设计与用于控制 NAND 闪存存储前端中的数据流的先进先出 (FIFO) 缓冲区的实现有着微妙的相似之处。虽然这两种设计之间没有直接联系,但它们都涉及不同的缓冲器电路,这些电路通过操纵输入生成所需的输出。

SSD 闪存控制器的 IC 设计

通用 SSD NAND 闪存控制器 IC 包括特定功能块,例如:

-

-

- 前端互连

- 中央发动机

- 缓冲区和存储介质管理单元

- 外围互连

- 用于可靠性保证和安全功能的多个加密引擎

-

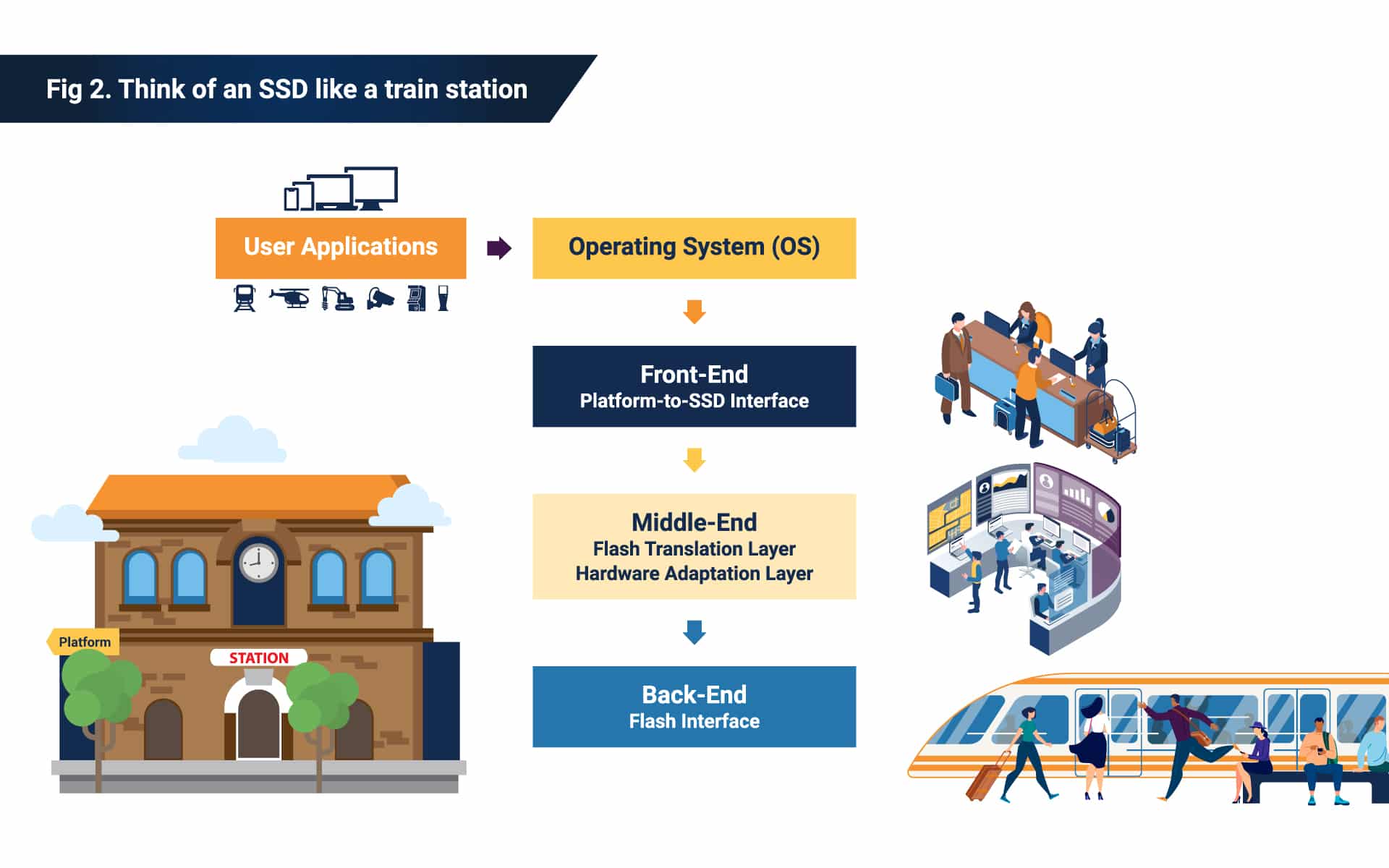

这些块协同工作,确保 SSD 作为可靠的数据存储设备高效运行。为了更好地说明这是如何发生的,我们将使用火车站进行类比。就像火车站内有不同的区域或区域供旅客使用一样,SSD 提供数据服务的操作也可以分为几个部分:前端、中端和后端。

前端

将 SSD 的前端想象成火车站的前厅。与车站大厅的服务包括票务、行李寄存甚至清洁服务类似,SSD 的前端充当数据的入口点,为传入信号提供许多初步处理服务。这些服务包括通过目标传输接口(可能是 SATA、SAS 或 PCIe)建立信号链路、遵守协议的数字信号转换以及各种连接验证例程。

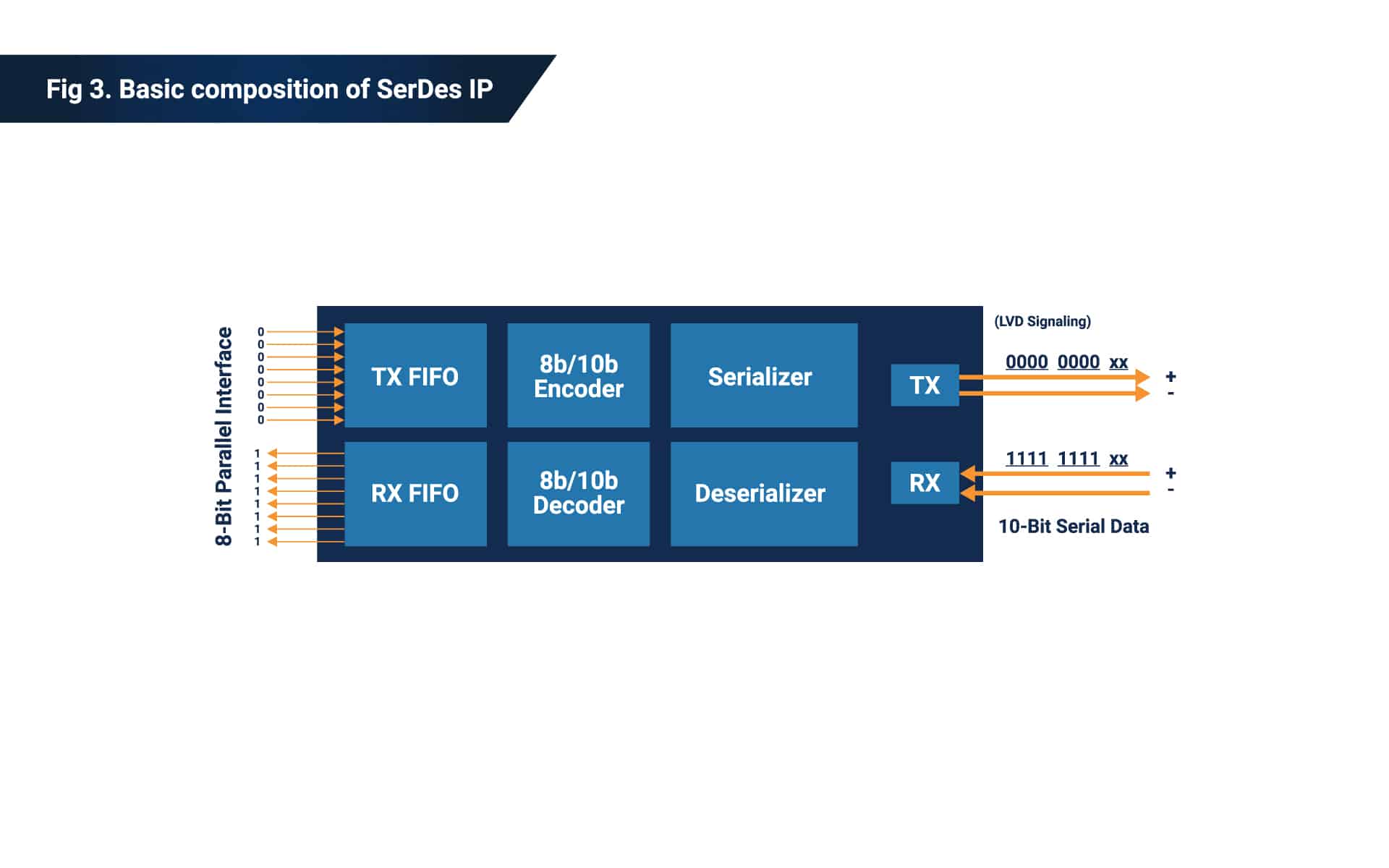

为了提供这些服务,许多通用和专利微型电路(通常缩写为 IP)必须封装到 NAND 闪存控制器 IC 芯片上。 Phison 自有 SSD 控制器解决方案上的前端 IP 的一个示例是 串行解串器 (串行和解串器的缩写)负责将传入的并行数据位(意味着它们同时通过不同的物理引脚传入)转换为串行位流,反之亦然。 SerDes 的组成包括一个用于数据流管理的 FIFO 缓存以及一对用于协议一致性的编码器。群联拥有针对主流SSD传输接口的全面SerDes IP组合,基于业界最佳的纳米级生产工艺构建,为其SSD前端提供全面支持。

中端

中台主要负责缓存和存储介质管理。 SSD 内部有两个关键的内存组件:DRAM 和 NAND 闪存。 DRAM作为缓存空间,可以放置临时数据,NAND闪存作为存储介质,可以长期存储数据。中端对于SSD来说非常重要,它是系统的中心。就像火车站调度员或播音员引导乘客到临时候车区或火车进行长途旅行一样,SSD IC 将数据引导到 DRAM 进行临时存储或 NAND 闪存进行长期存储。

为了完成中央调度办公室的工作,必须实施闪存转换层 (FTL) 和硬件适配层,以协作处理存储设备上的数据放置。 FTL 负责将其账本上的数据映射到闪存上的正确物理位置。同样,临时数据到DRAM也采用类似的表管理和映射机制。 FTL 和硬件适配层都是关键的固件功能,可以严重影响 SSD 的整体性能。它们由强大的中央硬件引擎驱动,必须在控制器 IC 的设计中精心规划。

为了满足中端的需求,群联拥有许多硬件IP,可以提供独特的方式来协助中央调度员。它们包括 CoX处理器™ 和 内存接口 IP 这使得群联的 NAND 闪存控制器 IC 的每一代产品都优于其他产品。

后端

NAND 闪存控制器 IC 的后端全部与 NAND 闪存有关。如前所述,NAND 闪存芯片就像我们火车站类比中的火车。就整体旅行体验而言,列车内服务与车站提供的帮助和指示同样重要。 NAND 闪存控制器 IC 设计的很大一部分集中在这些列车内服务,其中包括 NAND 接口协议符合性、耐久性维持和纠错。

NAND闪存控制器符合NAND闪存接口协议的能力就像拥有一位熟练的火车司机,可以完美且高效地操作不同的火车模型。群联拥有强大的IP组合,兼容主流协议ONFI和Toggle的最新接口规范。凭借积累的硬件和固件 IP,群联的 NAND 闪存控制器 IC 能够轻松流畅地驱动 NAND 闪存。

正如我们在旅行中所经历的那样,有时我们会在找到座位甚至登上正确的火车时犯错误,NAND 闪存中电子形式的数据也是如此。由于其固有的物理特性,电子有时会从 NAND 闪存单元中逸出,这可能会导致在操作期间和随着时间的推移出现数据位错误。因此,保持NAND闪存的高耐用性和可靠性是良好的NAND闪存控制器IC后端设计的另一个关键要求。

选择群联 IC 以获得高可靠性和品质

群联 从市场上选择最优质的 NAND 闪存解决方案,以保证其高端 SSD 产品拥有最佳的固有使用寿命,并且该公司通过强大的先进产品组合巩固了其质量传统。 纠错码 (ECC)。就像专业且乐于助人的火车服务人员协助乘客一样,群联先进的 ECC 基于几代不断改进的固件算法和专用数学计算的硬件引擎,可以轻松处理这些逃逸的电子和 NAND 闪存位错误。