스토리지 시장에서 솔리드 스테이트 드라이브(SSD)의 역할은 점점 더 중요해지고 있습니다. 그리고 SSD가 기존의 하드 디스크 드라이브(HDD)에 비해 엄청난 이점을 가지고 있기 때문에 SSD는 곧 주류 스토리지 솔루션이 될 것입니다.

SSD의 채택은 NAND 플래시의 프로세스 진화와 관련이 있습니다. 다른 반도체 제품과 마찬가지로 NAND 플래시 칩의 단가는 공정 노드를 줄임으로써 크게 줄어듭니다. 플래시 메모리는 또한 주로 트랜지스터 스케일링 및 다중 레벨 셀(MLC) 기술에 의해 구동됩니다. 단일 플래시 셀에 둘 이상의 비트를 저장할 수 있습니다. 안타깝게도 NAND 플래시의 물리적 특성으로 인해 단일 플래시 셀에서 트랜지스터의 축소 및 데이터 비트의 증가로 인해 신뢰성이 저하될 것입니다. 이러한 부작용을 커버하기 위한 기술이 개발되었습니다.

읽기 방해 오류

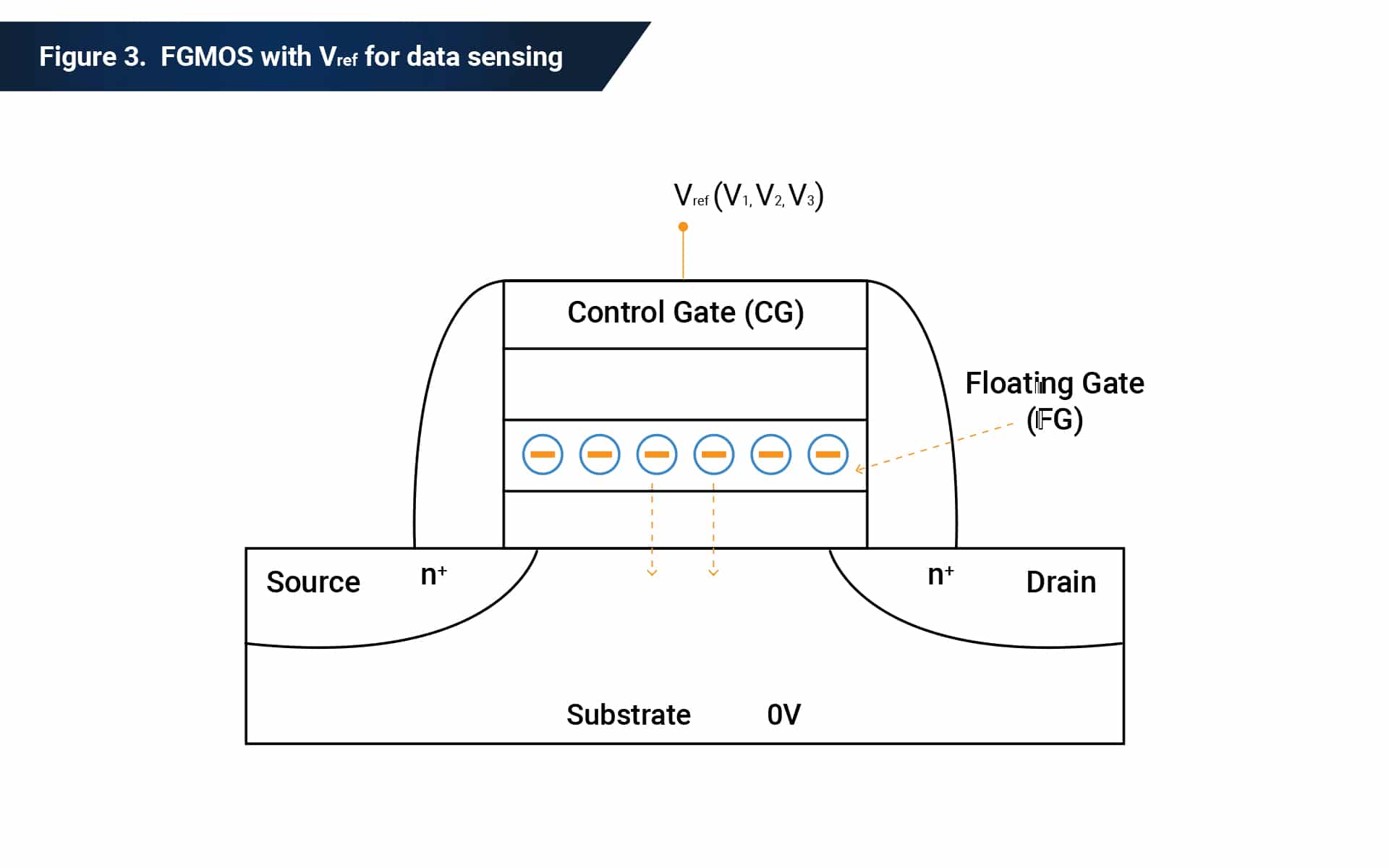

NAND 플래시 메모리는 수백만 개의 트랜지스터(MOSFET)로 구성됩니다. 각 MOSFET은 메모리 셀로 간주할 수 있습니다. 이러한 메모리 셀은 메모리 셀을 "스위치 온"할 수 있는 가장 낮은 전압인 문턱 전압(Vth)을 통해 데이터를 저장합니다.

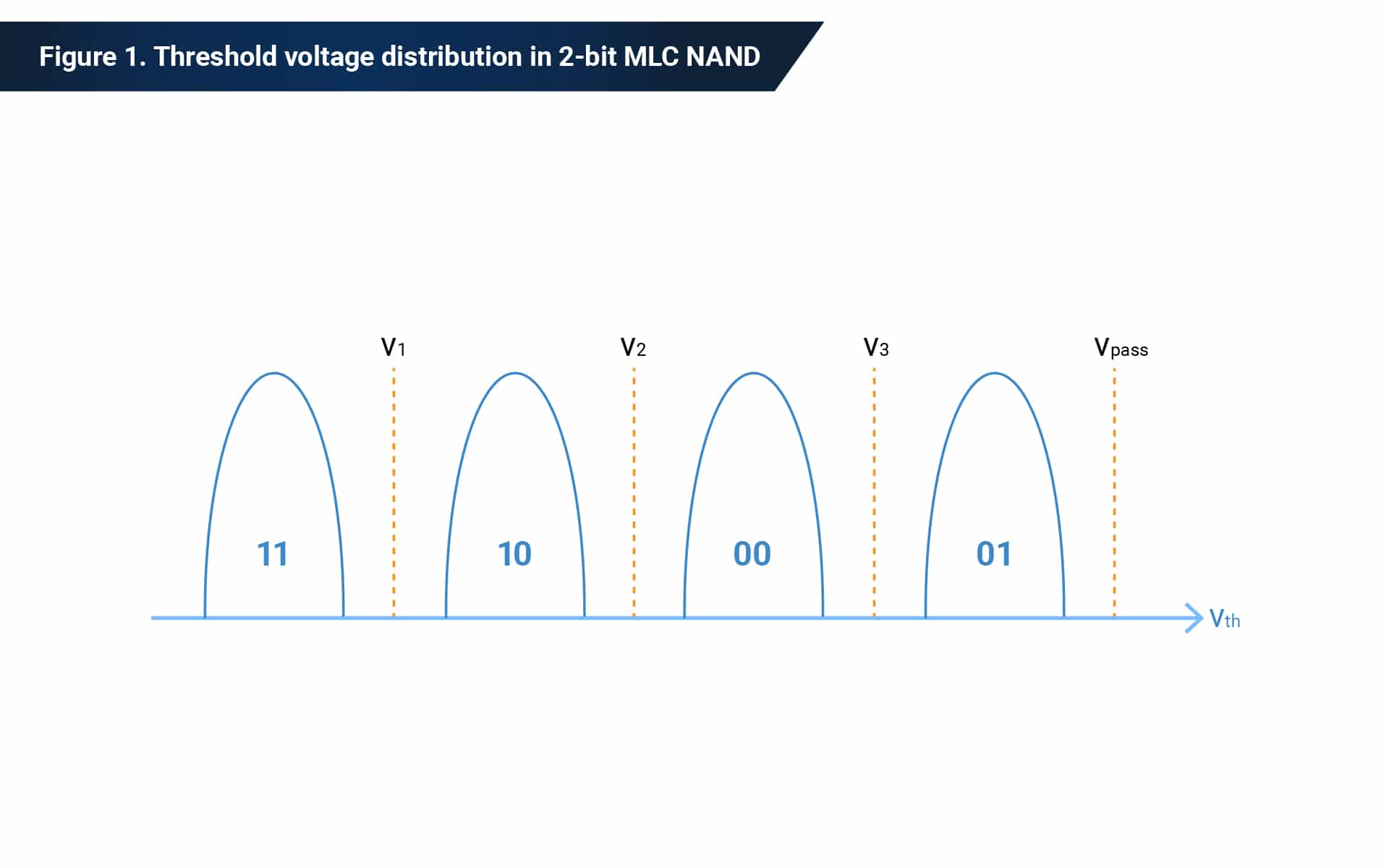

2비트 MLC NAND를 예로 들면 2비트 MLC NAND에는 4가지 데이터 상태가 있습니다. 가능한 Vth 값의 전체 범위를 이러한 4개의 세그먼트로 나누는 3개의 기준 전압(예: V1, V2 및 V3). Vth가 위치하는 영역은 메모리 셀의 현재 상태를 나타내며, 이는 메모리 셀에 어떤 데이터가 저장되었는지 식별하는 데 사용됩니다. 모든 메모리 셀의 문턱 전압의 상한선이 존재하며 이를 통과 전압(Vpass)이라고 합니다. Vpass는 메모리 셀이 "켜짐"으로 전환되도록 보장하는 데 필요한 전압입니다.

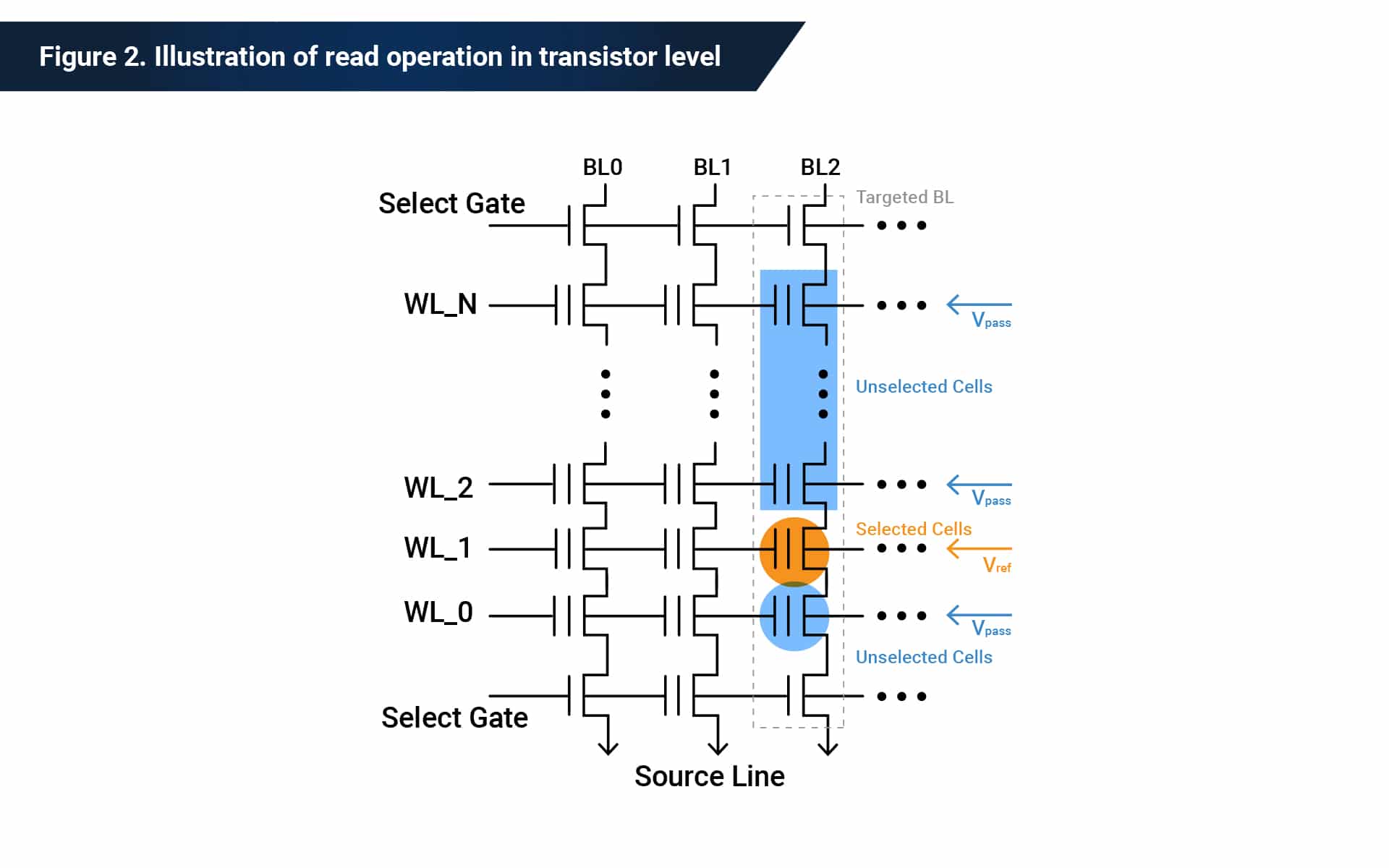

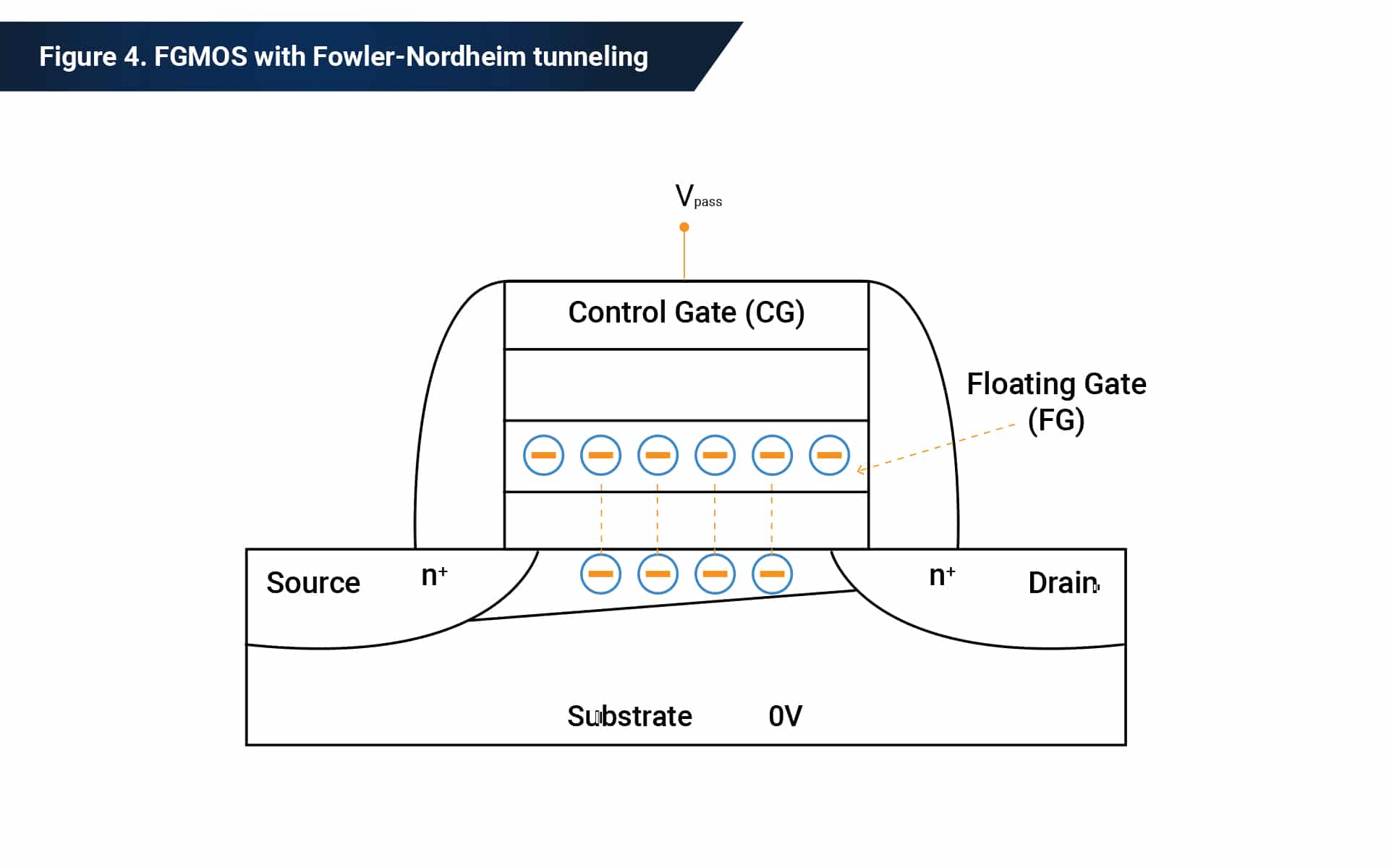

NAND 플래시 블록은 많은 트랜지스터의 배열로 간주할 수 있습니다. NAND 플래시 메모리에 대한 간단한 읽기 작업은 기준 전압(Vref)을 워드라인(WL)에 인가한 다음 이 WL에서 선택된 셀의 스위치 ON/OFF 상태를 확인함으로써 수행됩니다. 동일한 비트라인(BL)의 메모리 셀은 이웃 셀과 연결됩니다. 읽어야 할 대상 셀은 그 중 하나일 뿐이므로 선택되지 않은 다른 셀은 "ON" 상태를 유지해야 선택한 셀의 상태를 감지할 수 있습니다. 따라서 동일한 BL에서 선택되지 않은 다른 셀에 대해서는 통과(Vpass)를 적용해야 합니다.

이와 같이, 데이터 독출 동작이 수행될 때 동일 블록 내의 선택되지 않은 다른 셀들의 문턱 전압이 더 높은 값으로 이동된다.

동일한 블록에서 선택되지 않은 메모리 셀의 상태는 Vpass로 인해 영향을 받을 수 있습니다. 선택되지 않은 트랜지스터에 통과 전압이 인가되면 파울러-노드하임 터널링(Fowler-Nordheim Tunneling)이라는 터널링 효과로 인해 플로팅 게이트에 전하가 주입될 수 있습니다. 이 효과로 인해 트랜지스터의 임계 전압 이동이 발생하여 허용할 수 없는 데이터 왜곡이 발생합니다.

NAND 플래시의 보존 오류

일부 사용자는 SSD에 파일을 쓰지만 오랫동안 액세스하지 않습니다. 이러한 이전 파일에서 일부 오류를 감지할 수 있습니다. 이러한 종류의 오류는 시간 경과에 따른 전하 누출로 인해 발생합니다. 이 현상은 "읽기 장애"의 근본 원인과 유사합니다. 트랜지스터에 존재하는 전하는 메모리 셀의 임계 전압 레벨을 결정합니다. NAND 플래시의 스케일링 감소로 임계 전압 창의 크기도 점점 작아집니다. 이러한 다운스케일링 추세는 유지 노이즈로 인해 임계 전압 레벨 이동 가능성을 높입니다. 그러나 드물게 액세스되는 데이터의 무결성은 여전히 보장되어야 합니다.

Phison의 SmartRefresh™ 기술

SSD에 저장된 데이터를 보호하기 위해 Phison은 다음과 같은 독점 기술을 개발했습니다. 스마트리프레시™ 두 가지 기본 방법론을 사용합니다.

-

-

- 동적 오류 비트 모니터링(DEBM)

- 읽기 재시도

-

공정 규모 축소로 낸드플래시 고유의 신뢰성이 문제가 되고 있다. 오류 수정 코드(ECC) 기능은 NAND 플래시 업계에서 가장 중요한 주제 중 하나가 되었습니다. 불행하게도 어떤 종류의 ECC 알고리즘을 사용하든 그 수정 능력에는 이론적인 한계가 있을 수밖에 없습니다. ECC 엔진이 트리거되기 전에 오류를 줄이거나 피할 수 있으면 ECC 엔진이 사용자 데이터를 복구하지 못할 가능성이 낮아집니다. DEBM(동적 오류 비트 모니터링)은 데이터 손상이 발생하기 전에 데이터 상태를 확인하는 데 사용되는 메커니즘입니다.

Phison의 임베디드 펌웨어는 백그라운드에서 실행되어 각 블록의 오류 비트를 확인합니다. 펌웨어에서 설정한 기준 내에서 블록 실패가 발생하면(예: 오류 비트 수가 미리 결정된 임계값을 초과함) 펌웨어는 이 실패한 블록에 대해 특정 작업을 수행하여 사용자 데이터의 무결성을 보장합니다.

읽기 재시도

문제가 있는 NAND 블록에서 올바른 데이터를 얻는 또 다른 방법은 데이터 해석을 수행하기 위해 다른 전압 레벨을 선택하는 것입니다. 그림 1은 2비트 MLC NAND 플래시의 읽기 작업과 저장된 데이터를 해석하는 데 사용되는 임계 전압(Vth)을 보여줍니다. Phison의 펌웨어는 현재 대상 블록이 위험한 것으로 식별된 경우 적절한 전압 수준을 사용하여 데이터를 분석합니다. 이 방법론을 사용하여 검색된 데이터의 신뢰성은 Vth의 선택에 따라 다릅니다. Phison의 독점 알고리즘은 NAND 블록의 상태 평가를 기반으로 최상의 Vth 값을 결정합니다.

ITMS(유휴 시간 매체 스캔)

앞에서 언급한 방법론은 각각 예방 조치와 시정 조치로 간주될 수 있습니다. SmartRefresh™는 NAND 플래시의 물리적 특성으로 인해 원치 않는 오류로부터 사용자 데이터를 보호하기 위해 이 두 가지 방법론을 결합한 기술입니다. 이 메커니즘은 두 단계로 나뉩니다.

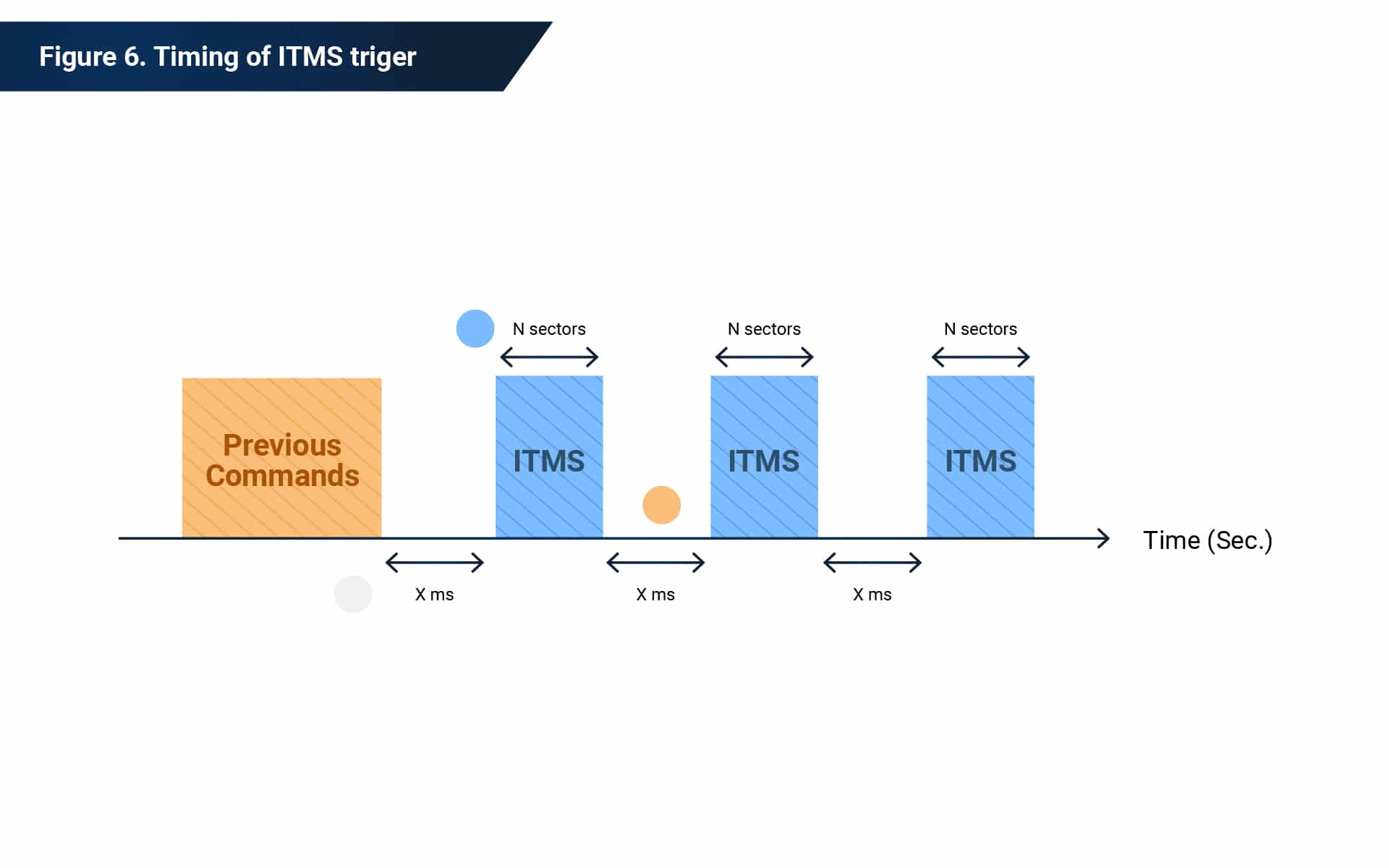

1단계는 ITMS(Idle-Time Media Scan)입니다. 호스트가 IDLE 상태에 진입하면 ITMS가 트리거됩니다. ITMS가 활성화되면 ITMS를 여러 ITMS 주기로 나누고 각 ITMS 주기 내에서 여러 섹터를 스캔합니다.

ITMS는 DEBM 및 읽기 재시도 작업이 수행된 후 스캔된 블록이 정상인지 감지하는 데 사용되는 메커니즘입니다. 비정상 블록으로 식별된 블록이 있으면 데이터 손실을 방지하기 위해 비정상 블록 내의 유효한 데이터를 적절하게 처리합니다. ITMS는 호스트가 저장된 데이터의 상태를 확인하기 위해 유휴 모드에 들어간 시간을 활용하기 때문에 호스트가 드라이브에 명령을 보낼 때마다 ITMS가 중단될 수 있습니다. 이 경우 ITMS가 중지되고 마지막 ITMS 주기에서 확인되지 않은 주소에서 다음 ITMS 주기가 시작됩니다.

RTMS(런타임 미디어 스캔)

2단계는 런타임 미디어 스캔(RTMS)입니다. ITMS와 달리 RTMS를 수행하는 타이밍은 IDLE 모드로 제한되지 않습니다. RTMS는 호스트가 드라이브에 명령을 계속 보내더라도 특정 기간(예: 매주 한 번)에 전체 드라이브 전체를 스캔하도록 보장합니다. 즉, RTMS는 장기 작업 처리에 사용되는 드라이브의 데이터 무결성을 보장하도록 설계되었습니다.

Phison은 데이터의 무결성을 보장합니다.

Phison의 독점 기술인 SmartRefresh™는 SSD에 저장된 사용자 데이터를 보호하기 위한 여러 계층의 작업을 포함하여 데이터 무결성을 보장하는 안정적인 메커니즘을 제공합니다. Phison의 SmartRefresh™ 솔루션을 채택하면 NAND 플래시 고유의 특성으로 인해 발생하는 오류를 피할 수 있습니다.