導入

何千年にもわたって、人類は技術を進歩させるための使い古された長年の公式を開発してきました。発明者や設計者は、コスト効率やパフォーマンスの向上に目を向ける前に、まず新しいテクノロジーの一般的なメカニズムを理解することに集中します。

この基本的な経験則は、他の分野や業界と同様にソリッド ステート ストレージ分野にも当てはまります。この記事では、ソリッド ステート ドライブ テクノロジのパフォーマンス向上に役立つ最近の重要な開発、ホスト メモリ バッファ (HMB) について説明します。

SSDメモリ設計のトレードオフ

ソリッド ステート ドライブ (SSD) の設計では、フラッシュ メモリを追加すると、パフォーマンスを向上させながらドライブ全体の容量を増やすことができます。ただし、他の製品設計と同様に、エンジニアはリソースとコストの間でトレードオフを行う必要があります。

SSD 設計の場合、各ユニットのパフォーマンスを既存の能力を超えて向上させるには 2 つの方法があります。1 つはフラッシュ メモリの密度を高めること、もう 1 つは追加の物理スペースを犠牲にして追加のフラッシュ メモリを搭載することです。ただし、ドライブのフォームファクターの選択に関係なく、プリント回路基板 (PCB) のスペースは限られているため、通常、基板上の他のコンポーネントを省略するという犠牲が伴います。

現在、多くのベンダーは、コスト削減を達成するために、高速だが高価な DRAM (ダイナミック ランダム アクセス メモリ) をドライブ設計から削除することを選択しています。ただし、高速揮発性メモリとして、DRAM には独自の目的があり、簡単に交換できません。 DRAM レス設計には、特に大量のランダム読み取り環境におけるデータ転送中のパフォーマンスと信号整合性の調整という点で、独自の問題に直面する必要があります。

ホストメモリバッファとは何ですか?

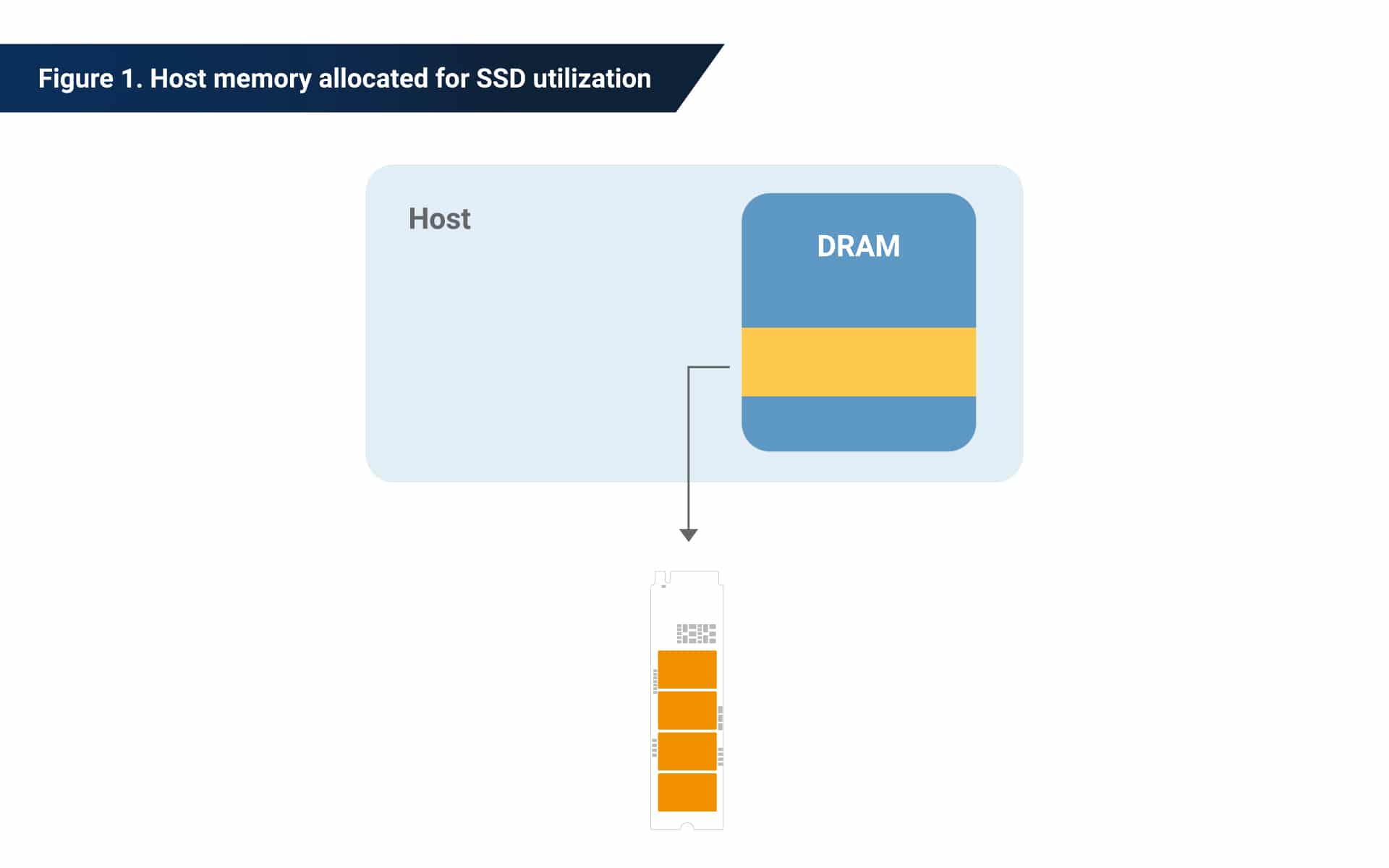

では、設計者は DRAM レス SSD の弱点にどのように対処できるのでしょうか?簡潔な答えは、ホスト メモリ バッファ (HMB) テクノロジーです。 HMB は、ホスト CPU のメモリ リソースを活用して、SSD が積極的にパフォーマンスの向上を追求できるようにする技術です。

NVMe (NVM Express または Non-Volatile Memory Express) は、NAND フラッシュ メモリや SSD などのコンピュータの不揮発性メモリにアクセスする方法を定義するオープン スタンダードです。 NVMe 1.2 仕様では、ホスト メモリ バッファ機能が初めて導入されました。

具体的には、NVMe 1.2 では、HMB を使用して SSD の使用のためにホスト メモリを割り当てる方法について概要を説明しました。適切な構成を備えた SSD はホストと通信して、必要な最小バッファ サイズを指定できます。 NVMe 1.2 仕様には、ドライブが誤って取り外された場合にデータが失われたり破損したりしないようにするなど、さまざまな目的のための条件と制限も含まれています。

HMB 機能を使用するには、ドライブとオペレーティング システムの両方が HMB 機能をサポートしている必要があります。幸いなことに、Microsoft は 2017 年にリリースされた Windows 10 Creators Update (バージョン 1703) 以降、HMB のサポートを許可しています。

なぜHMBなのか? DRAM ありから DRAM なしの SSD へ

以前の SSD 設計では、データ処理効率を高めるために、不揮発性フラッシュ デバイスと揮発性 RAM の両方を使用していました。具体的には、DRAM デバイスは次の 2 つの理由でバッファとして使用されます。

-

-

- DRAM デバイスは揮発性であり、電源が遮断されるとデータが失われます。これは、RAM が長期のデータ保存には適していないことを意味します。

- RAM デバイスはフラッシュ デバイスよりも高速に読み書きできます。この属性により、RAM がホストからのデータを一時的に停止する「中継ステーション」として機能すると同時に、タスクを継続的に処理するフラッシュ ストレージに猶予を与えることができます。

-

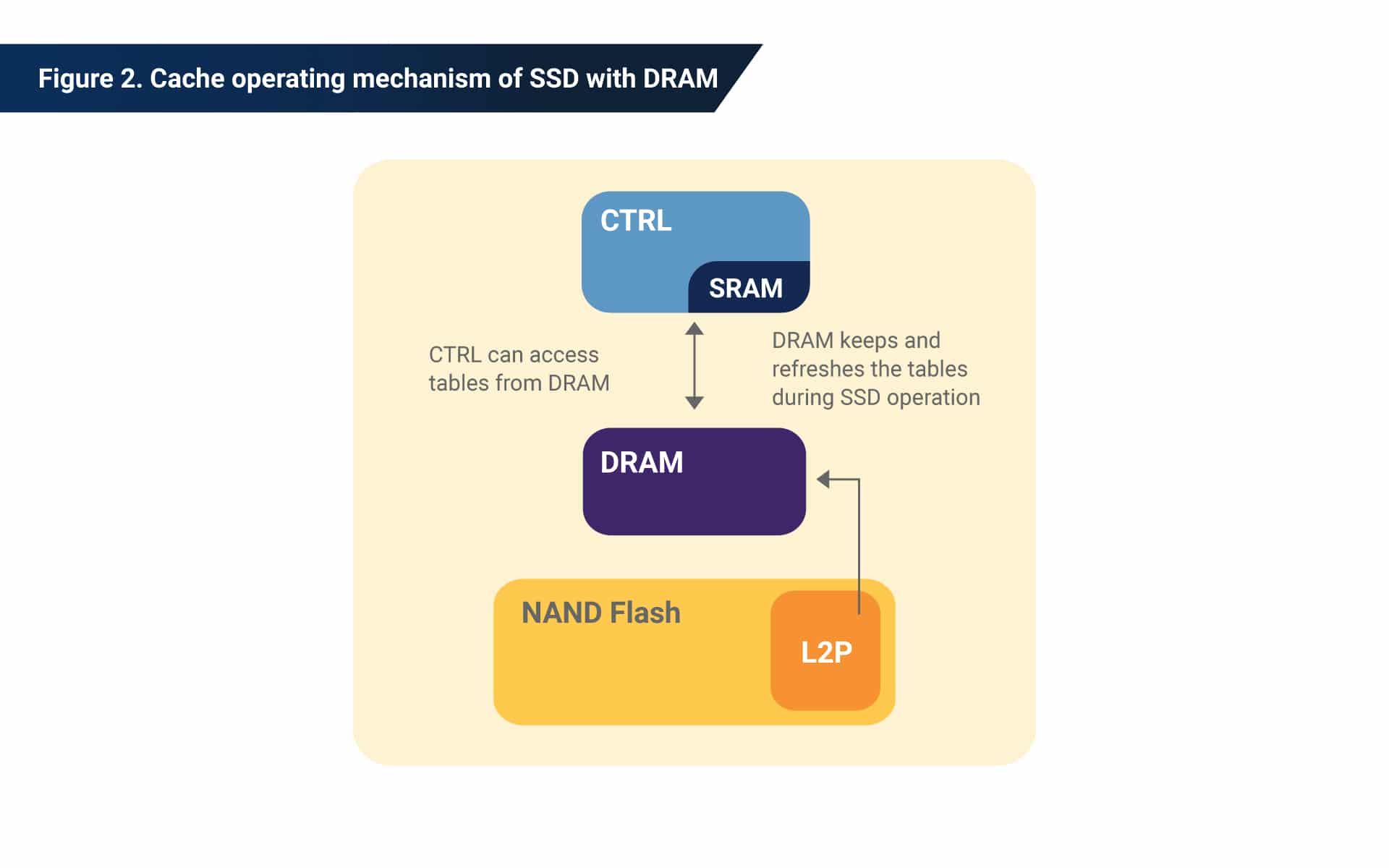

DRAM にキャッシュされる、または DRAM から取得される最も重要な情報は、論理アドレスを NAND フラッシュ アレイ内の格納データの物理的位置に変換するマッピング情報です。この情報は、L2P (論理-物理) テーブルと呼ばれるマッピング テーブルに保存され、SSD がフラッシュ ストレージにデータを出入りするときに頻繁に更新されます。 DRAM は電源が継続的に供給されないとすぐに動作しなくなるため、シャットダウン中は L2P テーブルがフラッシュ メモリに保存されます。

一方、電源がオンのシナリオでは、L2P テーブルが DRAM にアップロードされるため、コントローラーによって常に更新されます。 DRAM サイズが大きいほど、コントローラが使用できる空き領域が増えます。これは一般に、データの配置がより柔軟になり、コマンド受信時の反応時間が短縮されることを意味します。一般的なデータ ワークロードに関しては、いわゆる「ランダム読み取り」シーケンスを必要とする操作が、十分な DRAM スペースから最も恩恵を受けます。

ただし、DRAM などの貴重なリソースはフラッシュ ストレージに比べて高価です。密度を考慮すると、現在の DRAM の価格は NAND フラッシュ メモリの平均価格の 10 倍を超えており、これがすぐに変わる兆候はありません。

DRAM の利点にもかかわらず、過去 10 年間で、DRAM を搭載しない SSD が導入されました。これらの「DRAM レス」ドライブには、コストの削減や物理的寸法の小型化などの利点がありました。

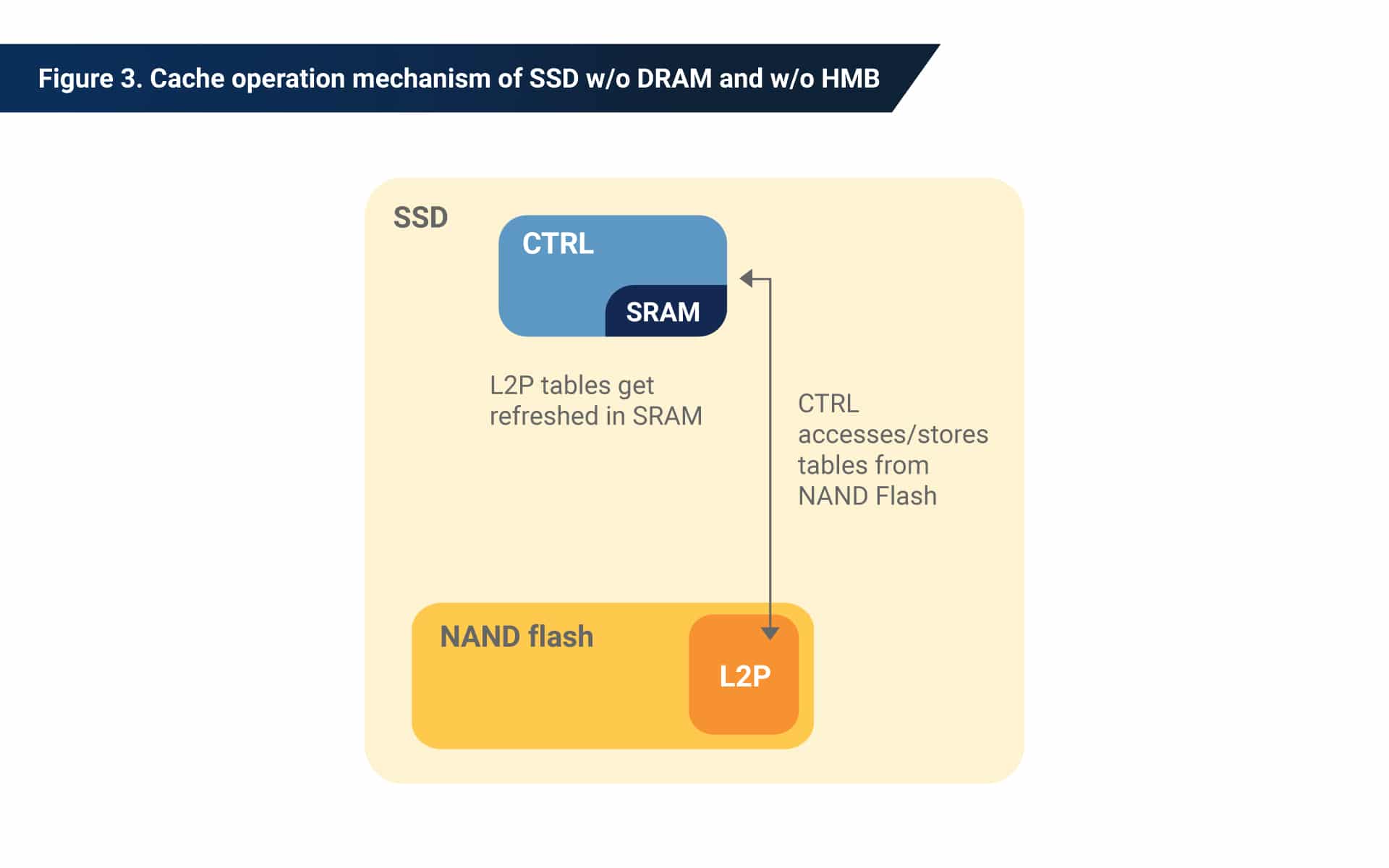

しかし、DRAM レス SSD も、厳密には「万能」なソリューションというわけではありません。 DRAM レス SSD のパフォーマンスは一般に、中間データおよびマッピング テーブル用に予約されたキャッシュ スペースの先天的な不足により低下します。

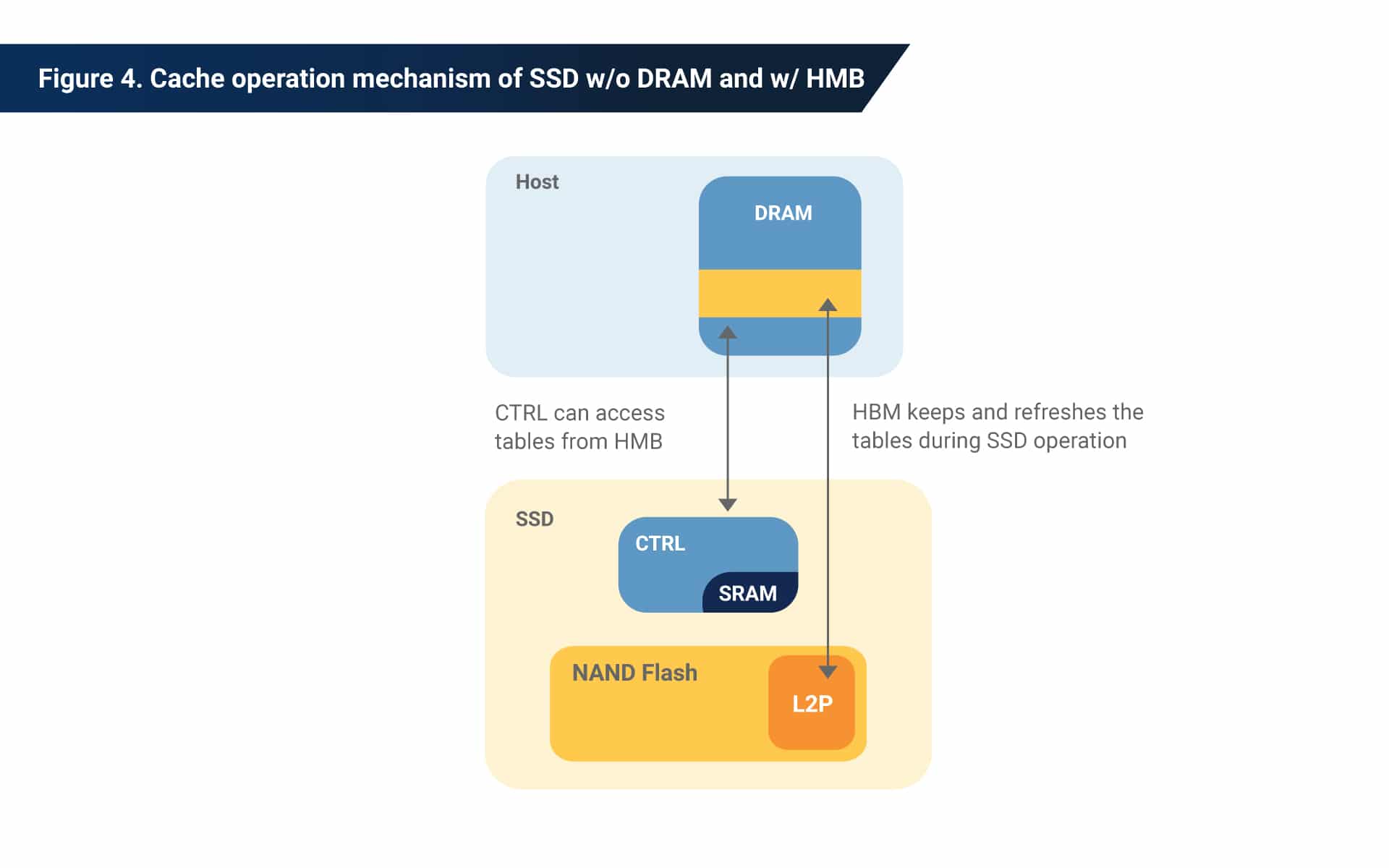

DRAM レス設計でも L2P テーブルが NAND メモリに保持されますが、DRAM が搭載された設計とは重要な違いがあります。コントローラーが NAND フラッシュ メモリからこれらのテーブルにアクセスしようとすると、情報は更新され利用される際にコントローラーの内部 SRAM (スタティック RAM) にロードされます。その後、これらのテーブルは再び NAND フラッシュ メモリに配置され、保存されます。

ここでの主な違いは、キャッシュ スペースとして SRAM を使用していることです。ただし、SRAM は貴重な高性能リソースであり、コストは DRAM よりもさらに高くなります。さらに、一般的なフラッシュ コントローラーには通常、数メガバイトの SRAM しか搭載されていません。通常、バッファ スペースが大きいほど効率が高くなるため、これらの DRAM レス設計は、パフォーマンスの観点からは最適ではないと考えられる場合があります。

この欠点こそが、HMB 機能が設計された理由です。 SSD の動作中に、L2P テーブルを NAND フラッシュから HMB に直接ロードできます。これらのテーブルは、従来の DRAM 方式とほぼ同様に、ホスト側からバッファ メモリ内で連続的にリフレッシュできます。

HMB が有効になっている SSD では、通常、ランダムなワークロードを処理する効率の低下が大幅に少ない、またはまったく低下しない可能性があります。次のセクションでは、HMB のパフォーマンスに関する具体的な実際のテスト データをいくつか見ていきます。

HMB パフォーマンスの向上: ありとなしの場合

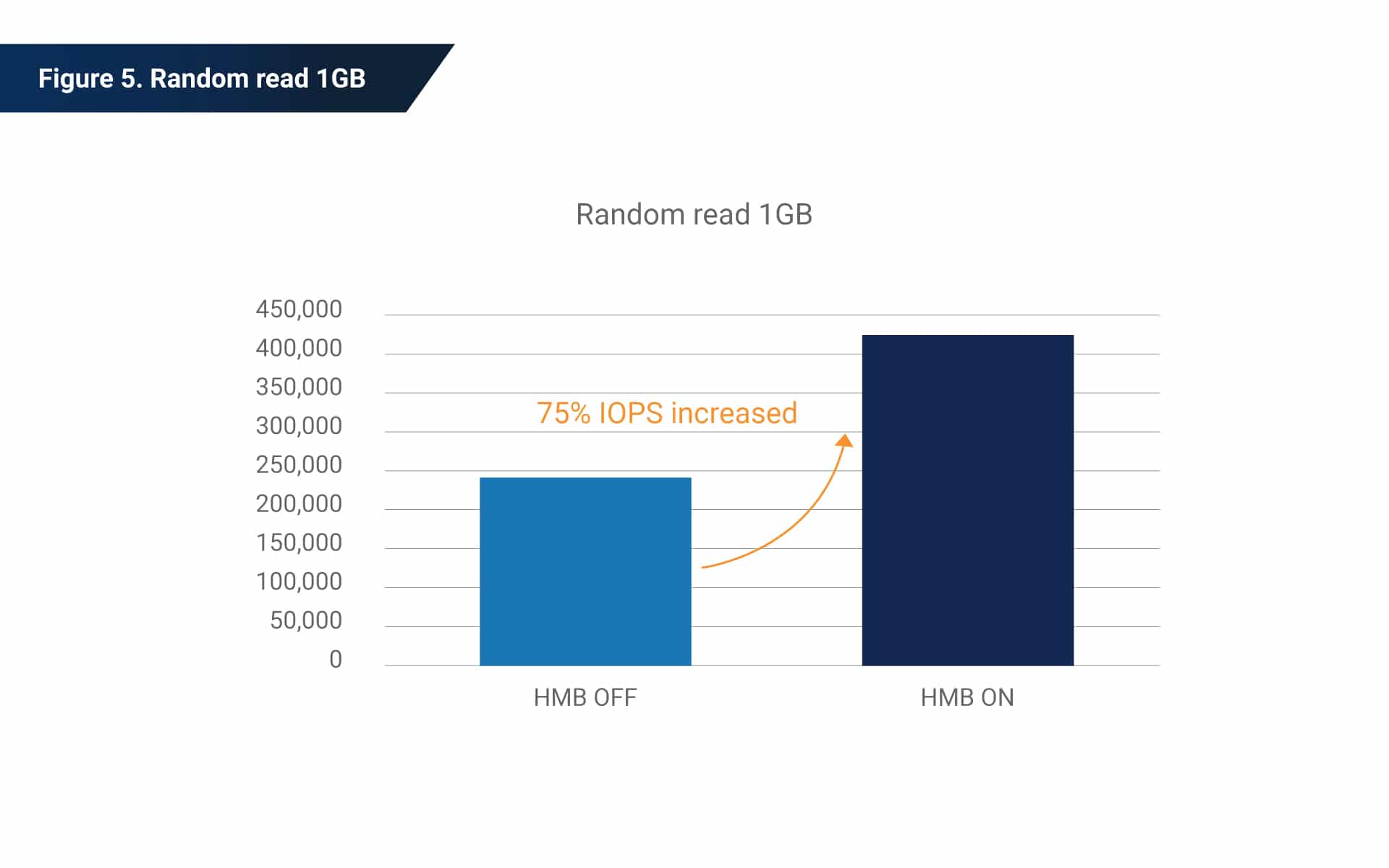

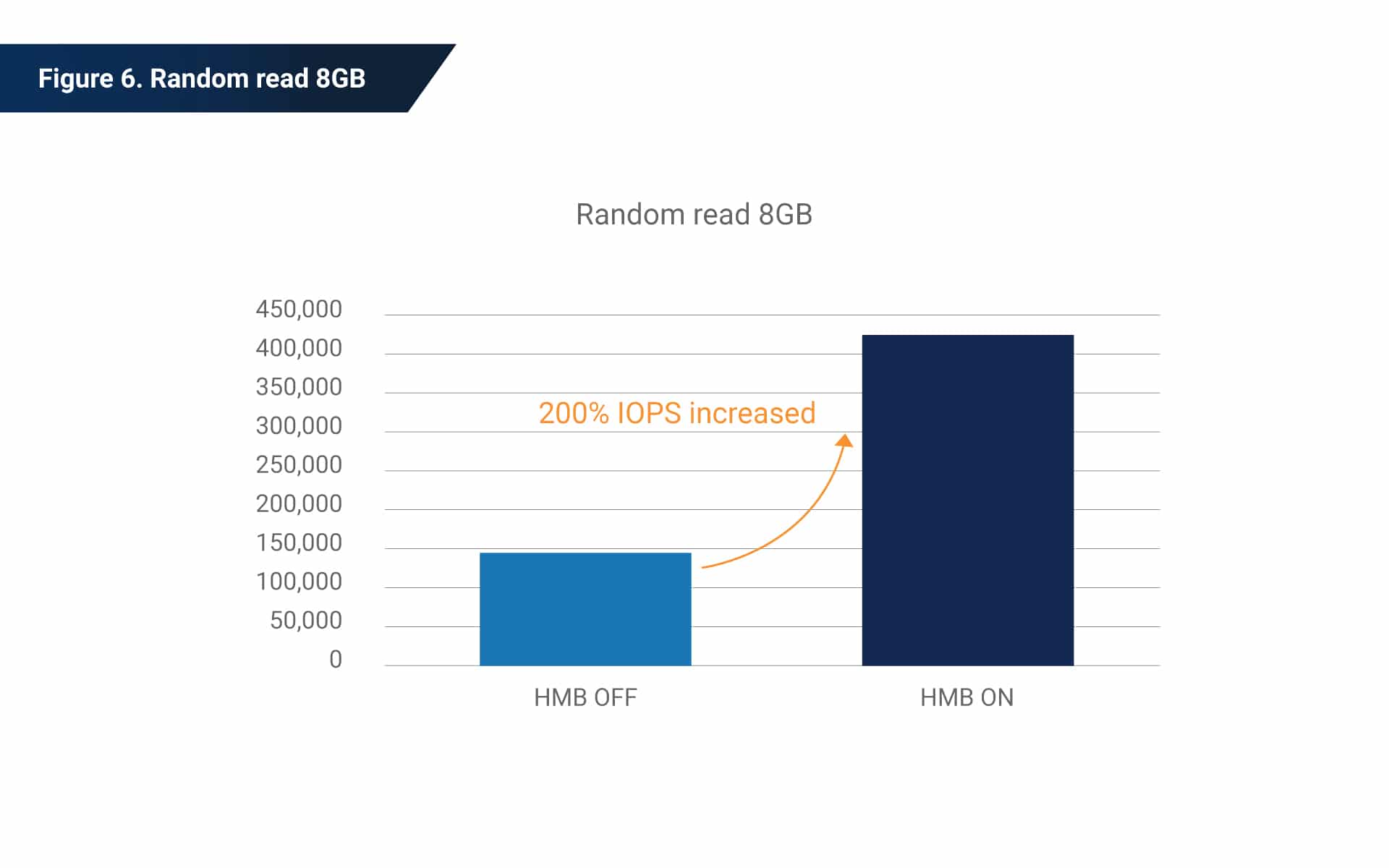

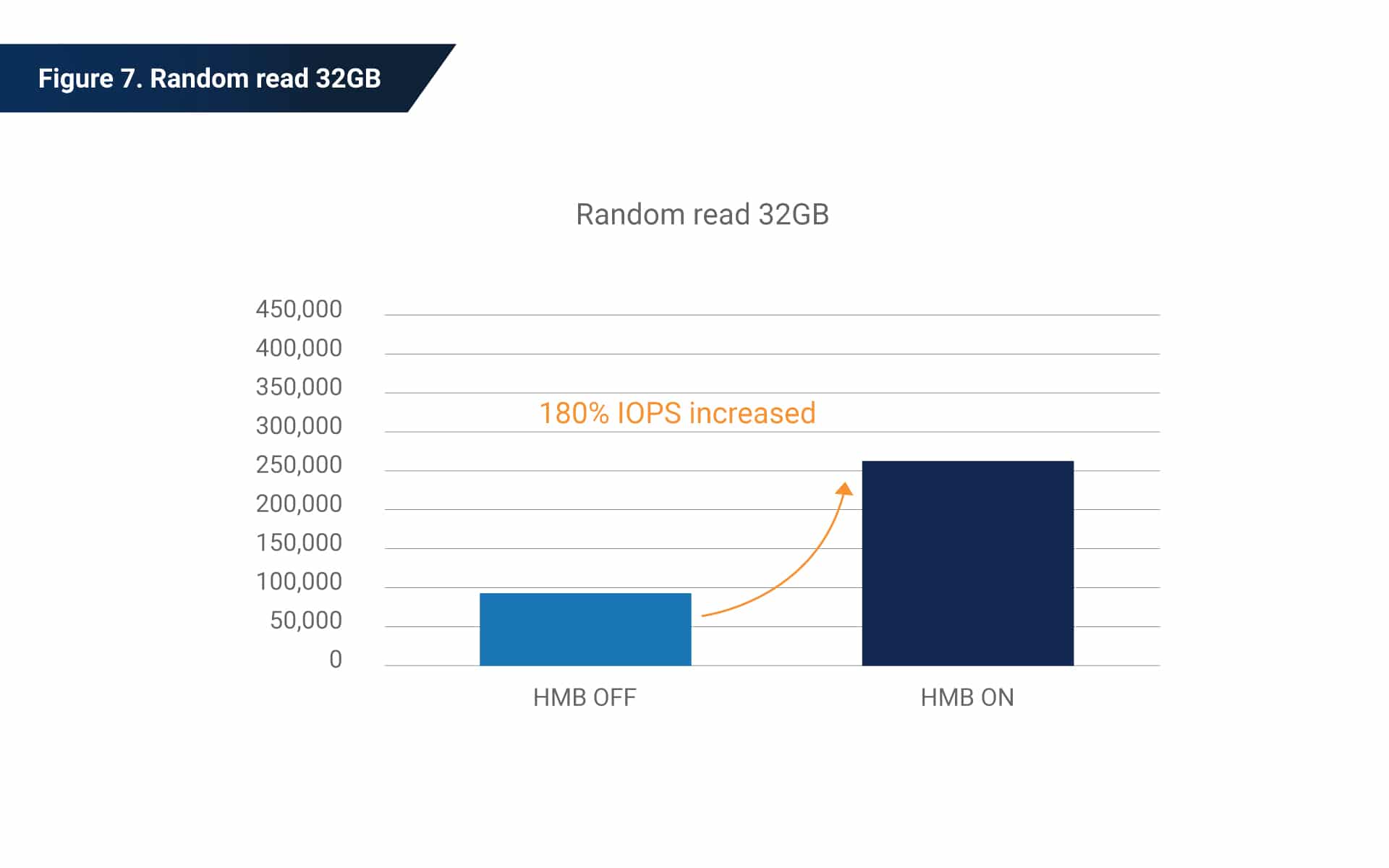

HMB を有効にすると、SSD は通常、いわゆる「ランダム読み取り」のパフォーマンスが向上します。これらの操作は、コントローラー レベルの操作を介してホスト要求ごとに、事前に決定されたサイズのデータ (ただし、フラッシュ ストレージ内の予測不可能な場所から) が取得される場合に行われます。

ただし、HMB のパフォーマンス向上はワークロードによっても異なる場合があります。これは、フラッシュ コントローラーが要求する実際の内部メモリ容量をホストが常に提供できるとは限らないためです。

これらのグラフは、HMB の使用によってパフォーマンスが非線形に向上し、ワークロードが 1 ギガバイト相当のデータの処理から 32 ギガバイトにスケールアップされたことを示しています。これは、HMB の DRAM 容量制限によるものです。

L2P テーブルを処理し、大量の中間データを処理すると、提供された HMB スペースへのロード操作が急激に増加し始めるしきい値に達します。したがって、32 ギガバイトのデータによる IOPS (1 秒あたりの入出力操作数) の増加は、わずか 8 ギガバイトのデータよりも顕著ではありません。これは、他のハードウェア テクノロジーと同様に、HMB のパフォーマンス向上には限界があることを示しています。

ただし、32 GB であっても、HMB を使用すると 100,000 以上の追加 IOPS が得られます。これは明らかに大幅な増加です。たとえ骨の折れるファームウェアの最適化を行ったとしても、得られる IOPS はわずか数千 IOPS です。

Phison が世界最高の SSD に HMB を使用する方法

DRAM レス SSD は、最初にリリースされて以来、ベンダーのいわゆる「バリュー ライン」の一部として広く導入されており、そのハードウェア構成によりコスト効率の面で利点があります。 Phison は、ハードウェアとファームウェアのノウハウを活用して、コントローラーのハードウェア リソースを乱用することなくパフォーマンスを向上させる HMB を独自の SSD に実装しました。

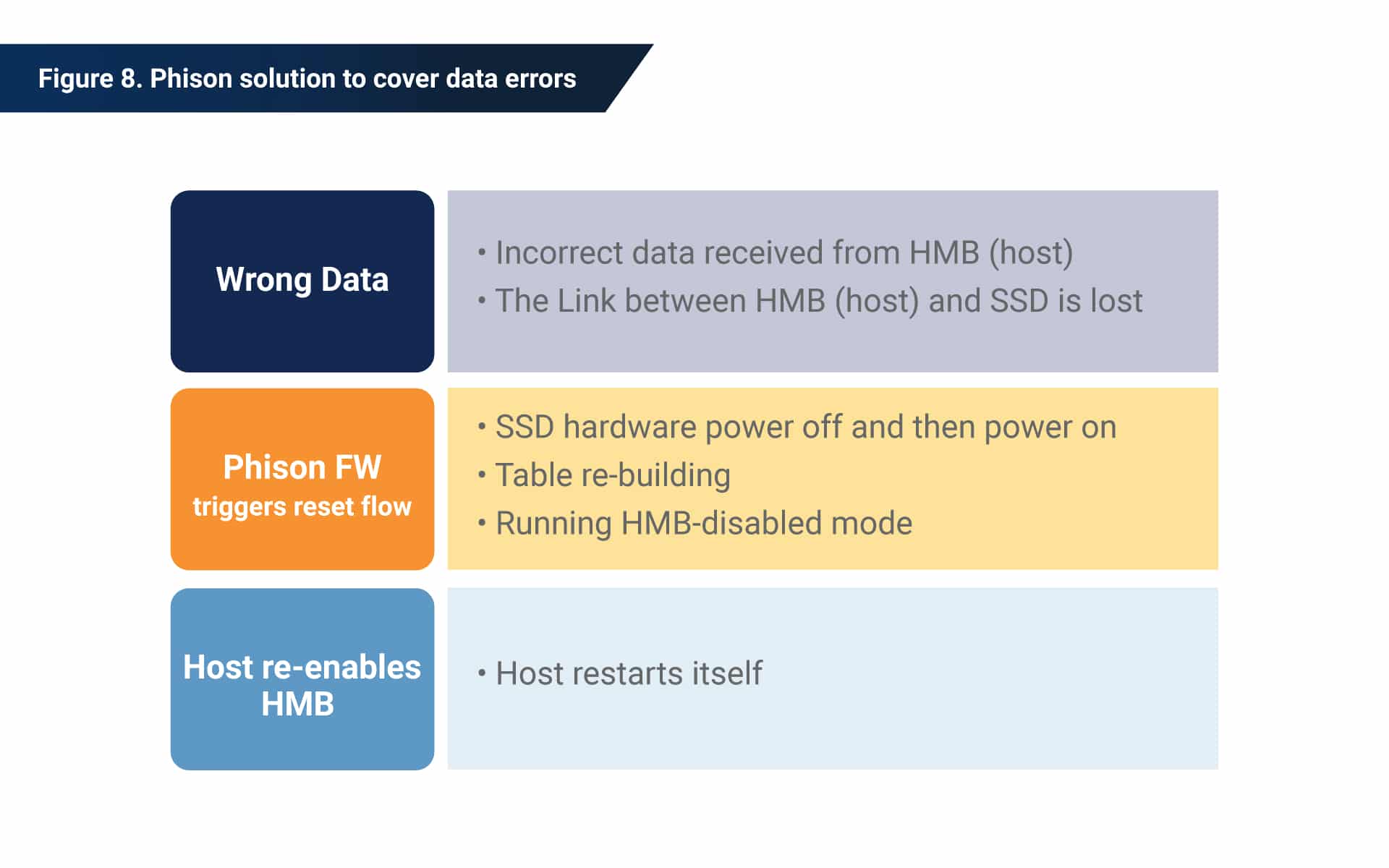

NVMe プロトコルで定義されているように、フラッシュ コントローラーは、HMB の使用中に SSD が予期せず取り外された場合でも、データ損失または破損の可能性がゼロであることを保証する必要があります。この基準を満たすために、Phison のコントローラ ソリューションは、データ送信エラーを根絶し、動作中にデータの整合性を確認するように設計された独自のファームウェアを使用しています。

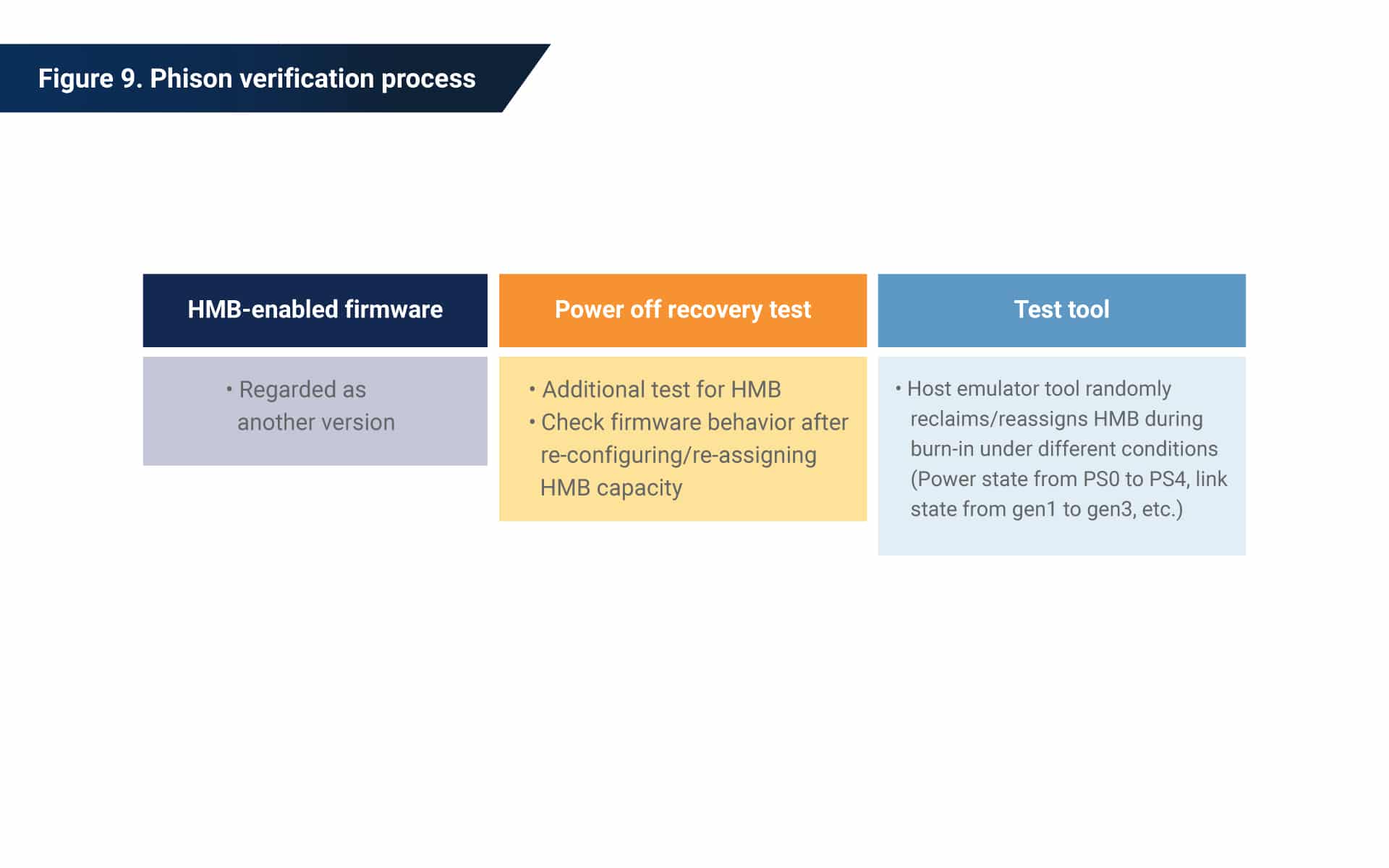

さらに、Phison はその膨大な知識と経験を活用して、SSD 設計をテストおよび検証します。 Phison は、コントローラー レベルとシステム レベルの両方のテストを実施して、徹底的な機能的および物理的な検証を行っています。

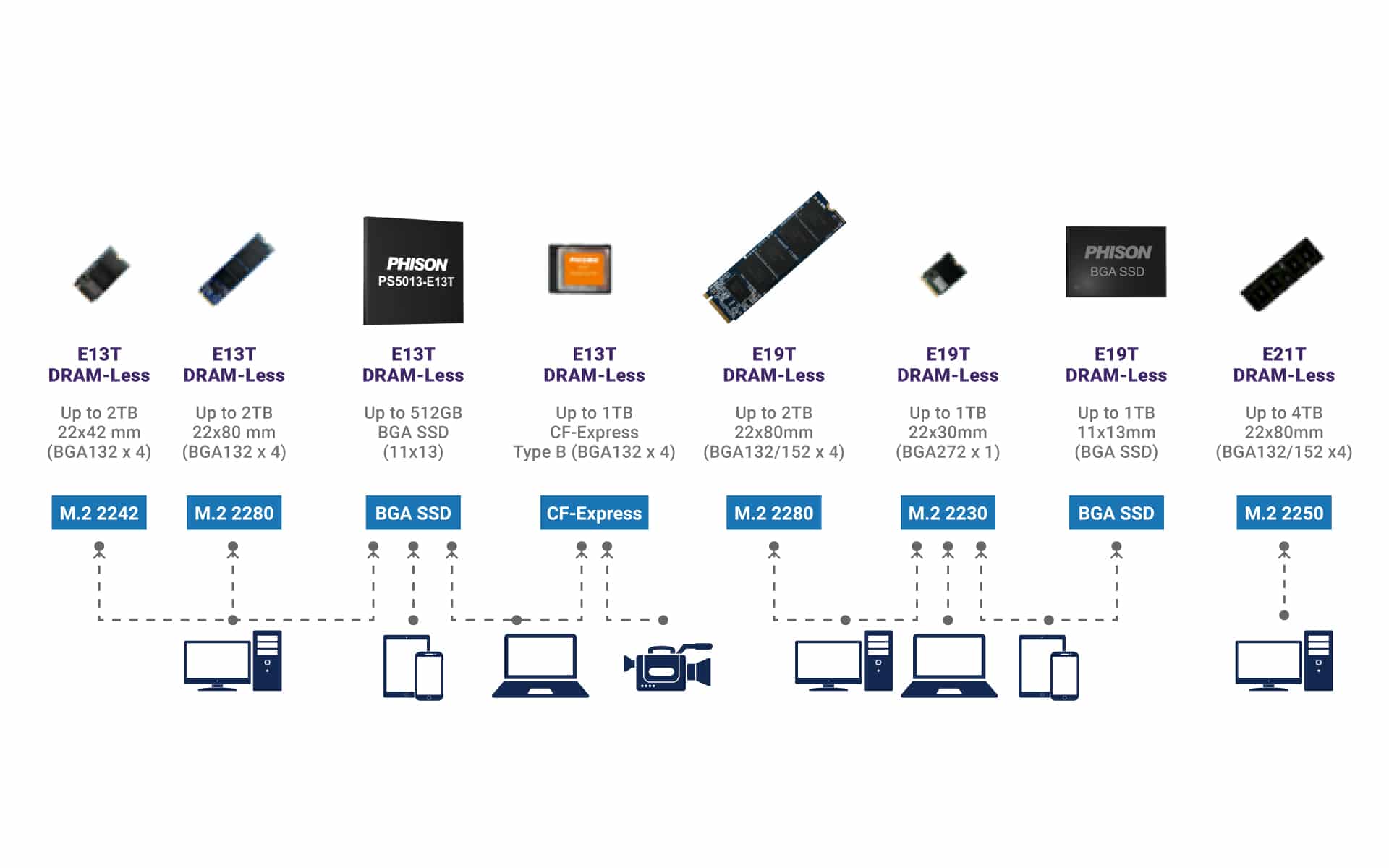

以下のグラフは、Phison がさまざまな業界アプリケーションに適合する DRAM レス製品を製造していることを示しています。詳細については、こちらをご覧ください フィソン.com.