Die Entwicklung der NAND-Flash-Technologie schreitet auf der Grundlage einer Vielzahl von Beiträgen aus der Industrie stetig voran. Die Zusammenarbeit zwischen Host-Geräte-Lösungsanbietern und Speichergeräte-Herstellern förderte die Einrichtung standardisierter Schnittstellen, die bis zum heutigen Ökosystem befolgt und gemeinsam ausgebaut wurden.

Die beiden bekanntesten öffentlich verfügbaren Schnittstellenstandards sind die Standards Open NAND Flash Interface (ONFI) und Toggle, die jeweils von ihrer jeweiligen renommierten Arbeitsgruppe entwickelt und kontinuierlich erweitert werden. Während Kontraste und Vergleiche zwischen den beiden Standards gezogen werden können, ist der JESD230-Standard, der vom Joint Electron Device Engineering Council (JEDEC) veröffentlicht wurde, eine anerkannte „gemeinsame Grundlage“, die als Referenz verwendet werden kann, die Entwickler aus dem Standard extrahieren können Sätze.

Die einzigartige Entwicklung jedes Satzes von Standards wird durch die Unterschiede in Befehls-, Adress-, Zeit-, Formatierungs- und physischen Konfigurationen deutlich, die auf ihre Gestaltung unter unterschiedlichen Geltungsbereichen und Kenntnissen führender Gruppen in der Flash- und Speicherbranche zurückzuführen sind. Dennoch vereinen beide Standards Kohärenz in ihrem Streben nach Kompatibilität und Interoperabilität zwischen verschiedenen Technologien.

Die Legacy-Schnittstelle

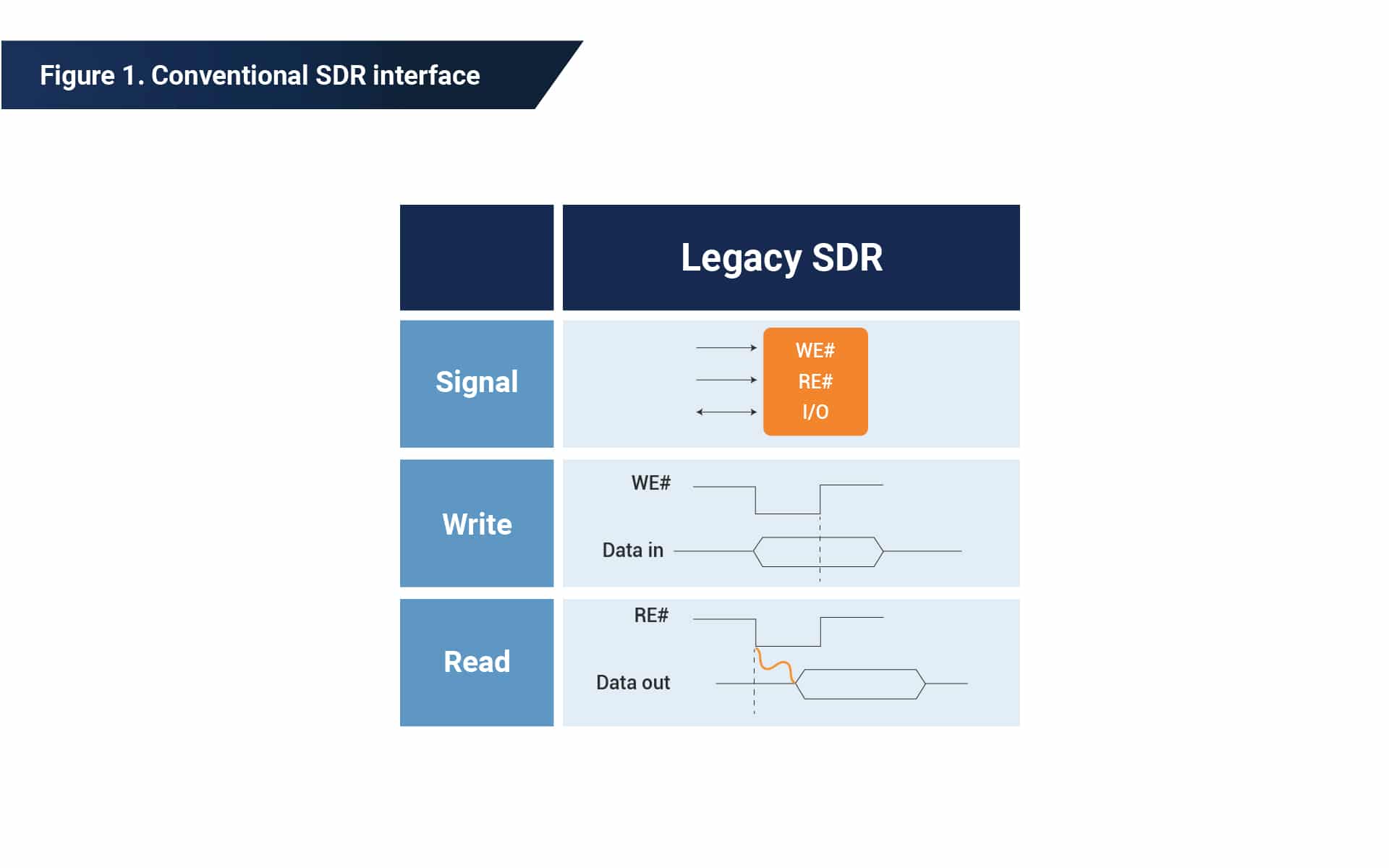

Wenn Sie in den Wissenspool über Flash-Schnittstellen eintauchen, können Sie sofort den Vergleich zwischen synchronen und asynchronen Datenübertragungsschemata erkennen. Die erste NAND-Flash-Geräteschnittstelle, bekannt als Legacy, wurde für die Verwendung des asynchronen Übertragungsschemas in Bezug auf die Zeitkriterien für Datenübertragungen konfiguriert. Für eine verbesserte Signalintegrität und -genauigkeit wird ein Synchronschema verwendet, um die Signale zu steuern, die mit einem kontinuierlichen Taktsignal synchronisiert werden müssen. Das asynchrone Schema ermöglicht, dass die Auslösung von Übertragungsaufgaben vollständig von den Steuersignalen „Write-Enable (WE)“ und „Read-Enable (RE)“ abhängt, ohne dass ein Takt erforderlich ist.

Darüber hinaus unterstützt Legacy die Datenübertragung mit Single Data Rate (SDR) und verarbeitet die Datenübertragung nur bei einer Flanke von Steuersignalen. Insbesondere erzwingt die Schnittstelle formulierte Signalausrichtungen nur an den ansteigenden Flanken von Schreibsignalen und der abfallenden Flanke von Lesesignalen, wenn Daten in Geräte hinein und aus ihnen heraus „verschoben“ werden.

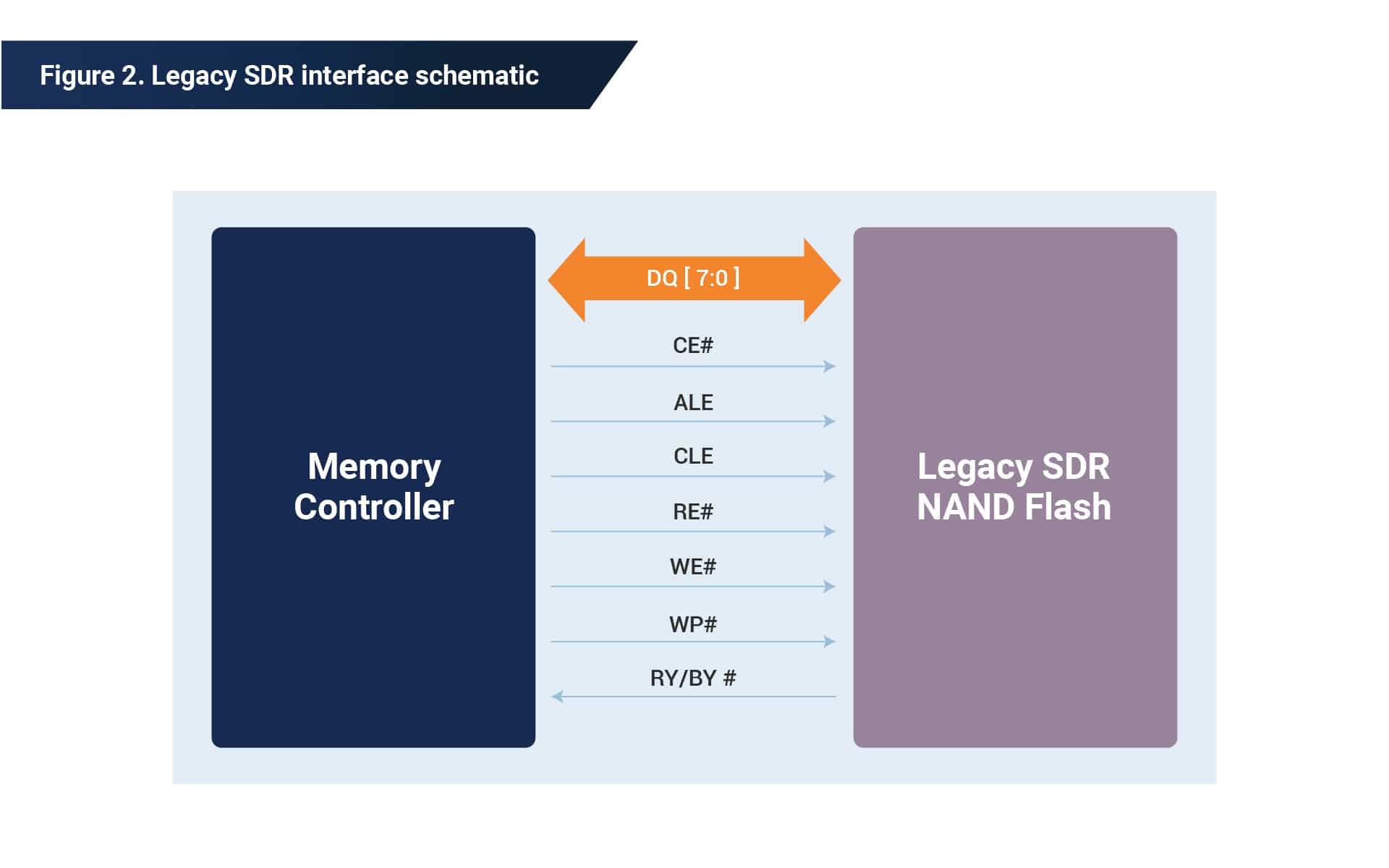

Mit sieben Steuersignal-Pins zusätzlich zu einem bidirektionalen 8-Bit(b)-Datenbus für I/O-Signalisierung (DQ) erreicht die 15-Pin-Schnittstelle die Lieferung eines Byte(B) innerhalb einer Übertragungszeit von 25 Nanosekunden(ns). ). Aufbauend auf diesem Attribut kann die maximale Bandbreite mit 40 MB/s oder 40 MB/s pro Datenpin berechnet werden. (1B/25ns = 0,04×109 B/s = 40 MB/s, 1B = 8b)

Die ONFI-Schnittstelle

Im Jahr 2006 gründete eine große Gruppe von Technologieunternehmen die Open NAND Flash Interface (ONFI) Working Group, darunter SK Hynix, Intel, Micron, SanDisk, Phison, Sony und andere. Später in diesem Jahr wurde die erste Version des ONFI-Standards entworfen und veröffentlicht, mit dem Ziel, einen einheitlichen Standard als Reaktion auf die unorganisierte Natur des Flash-Marktes bereitzustellen (die auf die inkonsistenten Kriterien für Flash-Schnittstellen zwischen Speicherprodukten, Flash-Anbietern und Downstream-Anbietern zurückzuführen ist). Produkthersteller).

Der vielschichtige ONFI-Standard veranschaulichte entscheidende Aspekte einer geeigneten Schnittstelle, die der Markt dringend benötigte, einschließlich, aber nicht beschränkt auf, Funktionscharakterisierungen, die Regulierung von Funktions-/Befehlssätzen, Signalbeschreibung/-zeitbedingungen, Verhaltensabläufe und Registerebene/physikalische Spezifikationen. Heute veröffentlicht die ONFI-Arbeitsgruppe weiterhin Updates zur Erweiterung der Standards, wobei der neueste Entwurf ONFI 5.0 ab 2021 ist.

ONFI 1.0

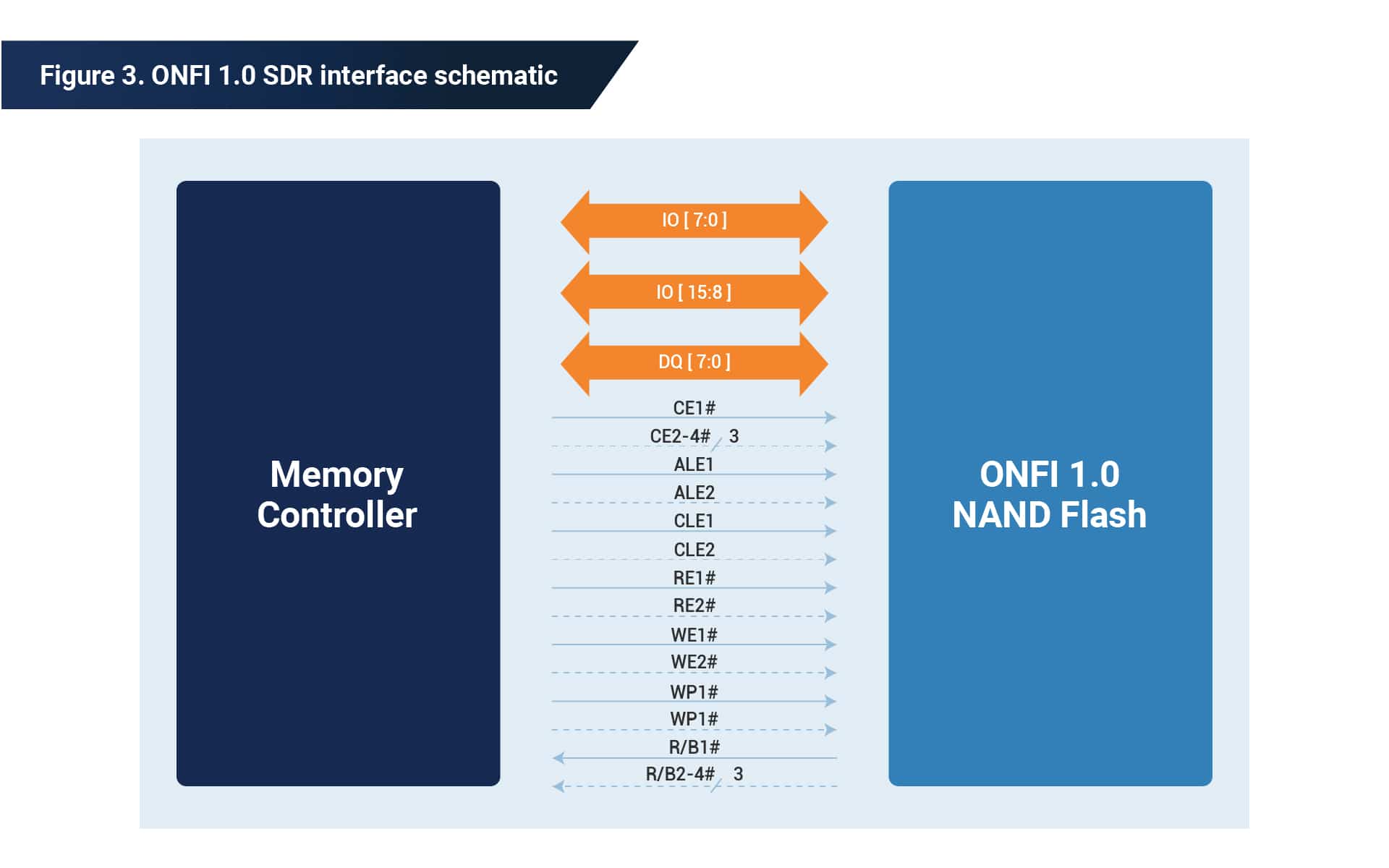

Der Hauptzweck der ersten Version bestand darin, eine beschleunigte Schnittstellenstandardisierung bereitzustellen, die über Legacy hinausgeht. Während Version 1.0 noch am asynchronen SDR-Übertragungsschema festhielt, beschrieb sie eine elektrische Schnittstelle ähnlich dem herkömmlichen Legacy, jedoch mit optionaler Unterstützung modernster Technologien wie einem 16-Bit-Datenbus mit Hochskalierung von Steuersignalen. Die Bandbreite von 50 MB/s bedeutet eine 20%-Verbesserung gegenüber der vorherigen Leistung von 40 MB/s bei Legacy.

ONFI 2.0

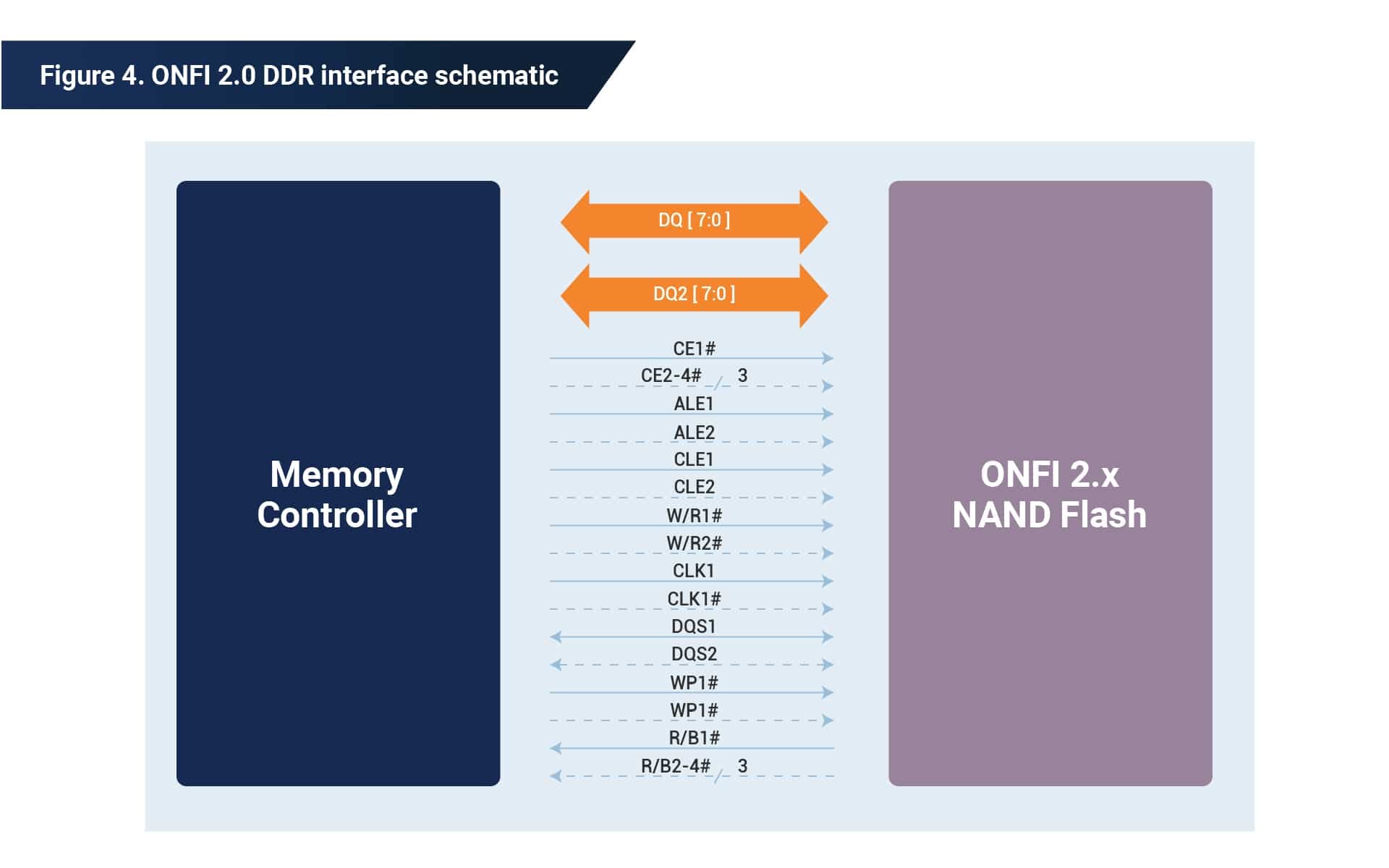

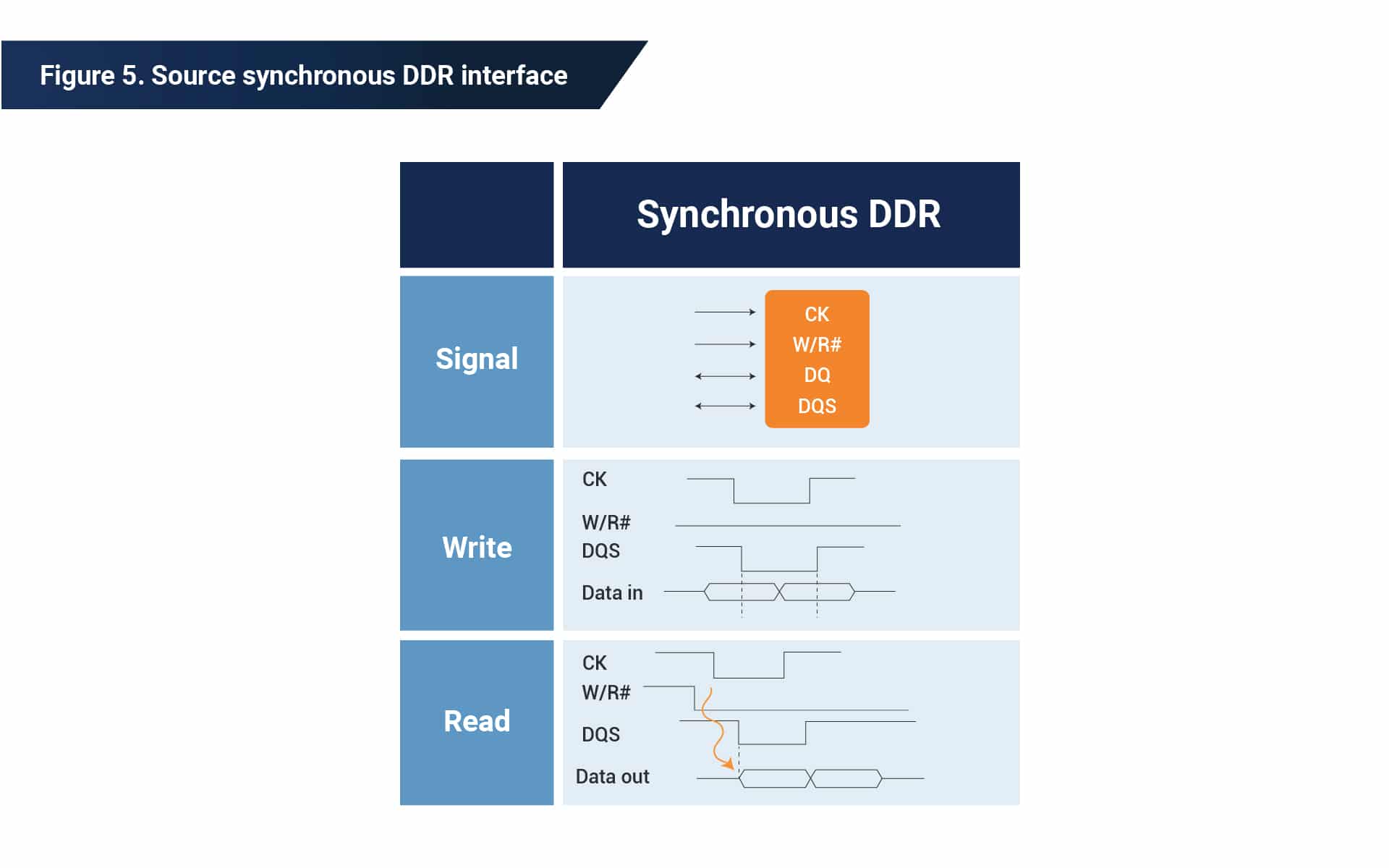

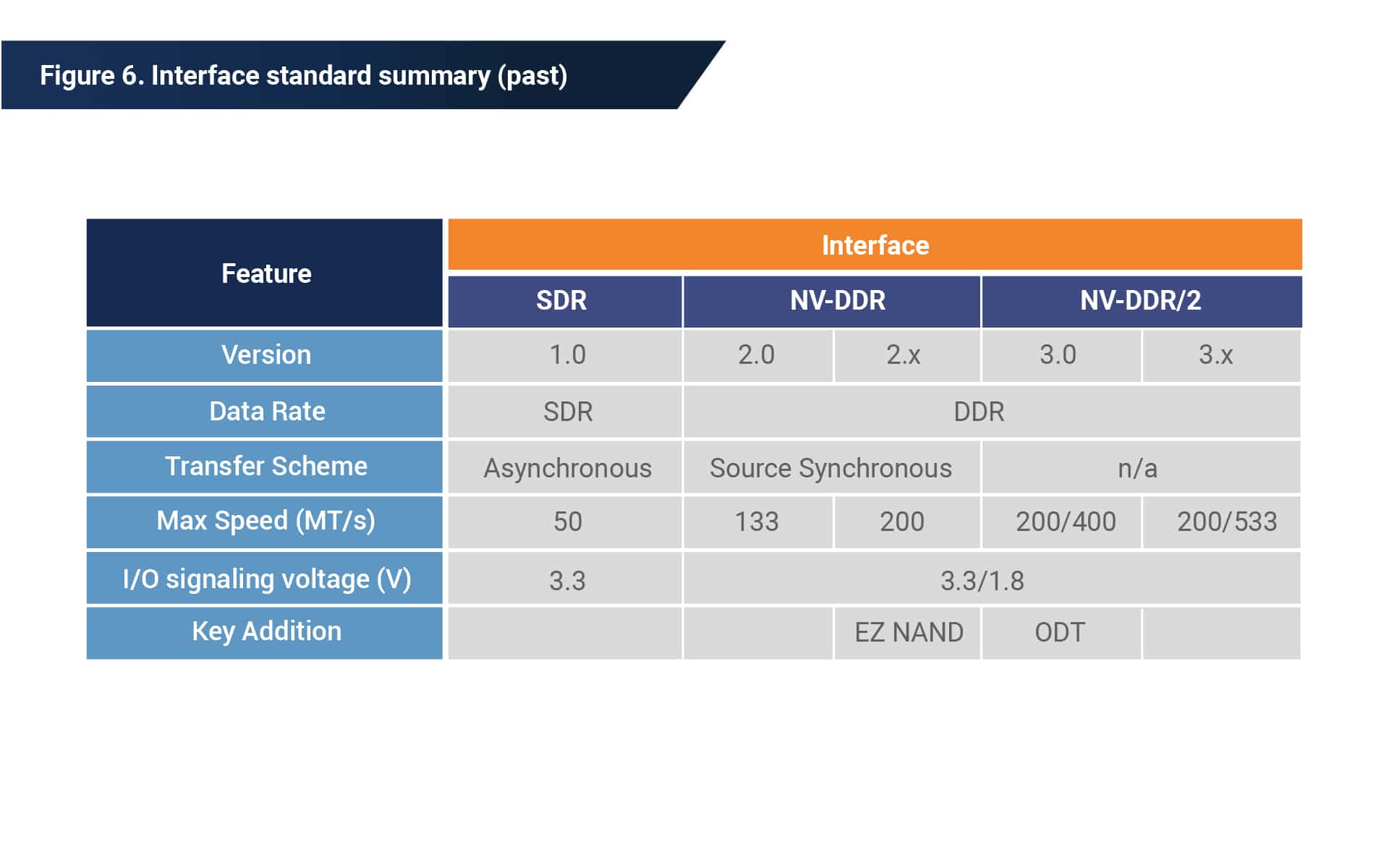

ONFI 2.0 wurde im Februar 2008 veröffentlicht. Die bedeutendste Änderung war die Einführung des Double Data Rate (DDR)-Übertragungsschemas, das eine erhebliche Steigerung des maximalen Gerätedurchsatzes ermöglichte, indem es Datenübertragungen an beiden Flanken von Steuersignalen ermöglichte. Darüber hinaus hat der ONFI-Standard die DDR-Flash-Schnittstelle innerhalb dieser Spezifikation in die NV-DDR-Schnittstelle (Non-Volatile DDR) umbenannt, wodurch sie von der flüchtigen Speicher-DDR-Schnittstelle unterschieden werden kann, die von Random Access Memory (RAM) verwendet wird.

Obwohl NV-DDR das asynchrone Arbeitsschema aus Gründen der Abwärtskompatibilität mit der vorherigen SDR-Revision beibehielt, wurden Anpassungen vorgenommen, um das quellsynchrone Schema zu unterstützen. Konkret wurde das frühere WE-Steuersignal zum Taktsignal (CLK), während das RE-Steuersignal zu einem Richtungssignal zur Auswahl zwischen Lese- und Schreibvorgängen wurde. Darüber hinaus wurden Daten nun sowohl bei steigenden als auch bei fallenden Flanken des neu hinzugefügten Daten-Strobe-Signals (DQS) übertragen, um die doppelte Übertragungsrate von bis zu 133 MT/s zu erreichen. Der erhöhte Durchsatz reagierte umgehend auf den Trend zu größeren Datenübertragungen und zufälligen Leistungsverbesserungen.

ONFI 2.1

ONFI 2.1 wurde 2009 mit Erweiterungen in mehreren Abschnitten der Revision 2.0 ratifiziert. Die 2.1-Standards ermöglichten ein Upgrade der maximalen Übertragungsrate auf 200 MT/s sowie neue Funktionen, die Raum für betriebliche Flexibilität boten.

Mehrere Abschnitte innerhalb der ONFI-Spezifikation wurden erweitert, beginnend mit erweiterten Parameterseiten, die ECC-Funktionen (Error Correction Coding) melden. Als wichtige Ergänzung in Revision 2.1 ermöglichten die erweiterten ECC-Informationen mehrere gültige Nutzungsmethoden für ein NAND-Gerät unter bestimmten Paarungen von ECC-Parametern mit anderen Geräteparametern, wie z. B. der Anzahl gültiger Blöcke und der Anzahl der unterstützten Programmier-/Löschzyklen.

Was die Speicherorganisation betrifft, so eröffnete die Einführung der verschachtelten Adressierung und der logischen Einheitennummer (LUN) neben der Reduzierung der Gehäuse-Pins, insbesondere der Chip-Enable-Pins, auch technische Möglichkeiten, wodurch die Redundanz komplexer Hardware-Designs verringert wurde.

Als Gerätesteuerungsbefehle wurden der „Small Data Move“ und der „Change Row Address“ eingeführt. Der Befehl „Small Data Move“ behebt die ECC-Einschränkungen für Low-End-Verbraucheranwendungen durch verkleinerte Datenblöcke in Gerätesteuerungsbefehlen. Der Befehl „Zeilenadresse ändern“ zielte darauf ab, den Arbeitsaufwand zu reduzieren, indem die Betriebsflexibilität des Geräts erhöht wurde.

ONFI 2.2

Aufbauend auf den Änderungen der vorherigen Revision wurde Ende 2009 ONFI 2.2 mit zusätzlichen Richtlinien zur Speicherorganisation veröffentlicht. Es wurden Einschränkungen zur bereits eingeführten Interleaved-Adressierung angegeben und Reset-Befehle für einzelne LUNs hinzugefügt. Die Überarbeitung definierte auch eine aktuelle Messmethodik im Anhang der Spezifikation.

ONFI 2.3

ONFI 2.3 wurde auf dem Flash Memory Summit (FMS) im August 2010 mit Schwerpunkt auf dem EZ-NAND-Protokoll (ECC Zero NAND) veröffentlicht. Das Protokoll empfahl, die ECC-Verwaltungseinheiten von der Seite des Speichercontrollers auf die Flash-Seite zu verlagern und so den Druck von der belasteten Steuereinheit zu verringern.

ONFI 3.x

ONFI 3.0 wurde im März 2011 mit einem ehrgeizigen Sprung bei den unterstützten Übertragungsraten von bis zu 400 MT/s angekündigt, was dem damals vorherrschenden Trend zur Vergrößerung der 8K-Seitendatenausrichtung entspricht. Die Durchsatzsteigerung ging auch mit einer Reduzierung der Signalspannung auf 1,8 Volt einher, um den Stromverbrauch zu optimieren.

Viele weitere neue Funktionen wurden eingeführt, um die Flash-Innovation voranzutreiben. On-Die-Termination (ODT) war die wirkungsvollste Ergänzung in dieser Spezifikationsrevision, ein Design, das die Signalintegrität von Speicherkanälen verbesserte, indem es dem Controller ermöglichte, den Abschlusswiderstand für unabhängige oder alle Geräte innerhalb eines Pakets ein- und auszuschalten . Multi-Chip-Paketfunktionen wie ODT wurden in dieser Überarbeitung ausführlich behandelt, um heikle Vorgänge und Verhaltensweisen auf Chip-Ebene zu steuern.

Zu den weiteren Funktionen gehörten Verbesserungen bei der Volumenadressierung und eine geringere Anzahl erforderlicher Chip-Enable-Pins, was die Effizienz der Schaltungsführung verbesserte. Doch als Revision 3.2 veröffentlicht wurde, geriet ein Upgrade der Übertragungsrate erneut ins Rampenlicht, da der Durchsatz von 533 MT/s unter der NV-DDR2-Schnittstelle verfügbar wurde, was damals Flash-Upgrades innerhalb von Geräten derselben Generation legitimierte.

ONFI 4.0

Die ONFI 4.0-Spezifikation kam 2012 mit Übertragungsraten-Upgrades auf 667 MT/s durch den früher bekannten NV-DDR2 und 800 MT/s durch den neu eingeführten NV-DDR3 auf den Markt. Als ODT-Erleichterungstool zur Kalibrierung des Abschlusswiderstands wurde eine als ZQ-Kalibrierung bezeichnete Technik eingeführt. Diese Spezifikation beschränkt die Beeinträchtigung der Signalintegrität bei Spannungs- oder Temperaturänderungen. Darüber hinaus ermöglichten diese Verbesserungen, dass der I/O-Strombedarf (VCCQ) auf 1,2 Volt gesenkt werden konnte, um den Stromverbrauch zu verbessern.

ONFI 4.x

Die gegenüber Version 4.0 erweiterten ONFI-Spezifikationen brachten mehrere Änderungen mit sich, darunter Flexibilität bei der Leistungskonfiguration, subventionierte Funktionsparameterdefinition und zusätzliche Optionen für die physische Pinbelegung.

Beginnend mit ONFI 4.1 wurden Optionen für die Kernsteuerspannung (VCC) als 2,5 Volt eröffnet und eine Reihe von Konfigurationen von 2,35 Volt bis 3,6 Volt zu den ursprünglichen 3,3/1,8/1,2-Einstellungen hinzugefügt.

Duty Cycle Correction (DCC) und DQ-Lese-/Schreibschulungen wurden zusätzlich zur ZQ-Kalibrierung als Funktionen hinzugefügt, um NAND-Geräteanpassungen während des Initialisierungsprozesses zu erleichtern. Diese Änderung zielte speziell auf Geräte ab, die über 800 MT/s bei hoher Arbeitslast arbeiten. Ziel der DCC-Schulungen war es, mögliche Abweichungen im Arbeitszyklus des „Read Enable Complement“-Signals (ein Komplementärsignal zum „Read Enable“-Signal) auszugleichen. Der

DQ-Schulungen dienten als Versuch, die DQS- und DQ-Signale an das hostseitige System anzupassen.

Mit der Revision 4.2 wurden Änderungen an den Details der DCC-Trainingsspezifikationen vorgenommen, während andere Änderungen an den Optionen für die physische Pinbelegung vorgenommen wurden. Konkret wurde zu den bisherigen BGA-272- und BGA-316-Zuordnungen eine 252-Ball-Ball-Grid-Array-Belegung (BGA) als neue Option für die physikalische Schnittstelle hinzugefügt.

ONFI 5.0

Die Veröffentlichung von ONFI 5.0 erfolgte Anfang 2021. Drei weitere Pinbelegungsoptionen wurden in der frisch veröffentlichten Standardspezifikation enthüllt, zusammen mit Anweisungen zu Änderungen, die für eine ordnungsgemäße Einführung erforderlich sind. Wichtiger war jedoch die NV-LPDDR4-Schnittstelle, die den Schwerpunkt auf die Senkung des Gesamtstromverbrauchs legt und gleichzeitig die Übertragungsrate jeder Schnittstelle erhöht, nämlich 800 MT/s bei NV-DDR2 und bis zu 2400 MT/s bei NV-DDR3 und NV-LPDDR4. Unter Berücksichtigung der erhöhten Übertragungsrate können Geräte, die NV-LPDDR4 unterstützen, die Data Bus Inversion (DBI)-Funktion nutzen, um den Stromverbrauch zu begrenzen, indem sie die Signalrichtungen und damit die Menge des Stromflusses steuern.

Andererseits löste die Einführung von NV-LPDDR4 einen weiteren Vorstoß zur Funktionsänderung für ODT aus. Zusätzliche Funktionen wie ODT-Deaktivierung/-Aktivierung und Kanal-ODT befassten sich mit möglichen Auswirkungen, die ODT durch die neue NV-LPDDR4-Schnittstelle erlitten hat.

Bei der Aktivierung von NV-LPDDR4 könnte die interne Referenzspannung zwischen NAND-Geräten und Controllern in einem untrainierten Zustand belassen werden, aber die durch ODT verursachten kleinen Signalschwankungen könnten zu Fehlern in Befehlssequenzen führen. Daher kann die rechtzeitige Deaktivierung/Aktivierung von ODT den Betrieb unter der neuen Schnittstelle erheblich beeinflussen.

Abgesehen von dieser schalterähnlichen Funktion ermöglicht die Kanal-ODT-Einstellung die Steuerung der Pull-up-Widerstandsstärke des On-NAND-Ausgangs und damit des Signalabschlusswiderstands. Mit anderen Worten: Die Einstellung ermöglicht es der Hostseite im Wesentlichen, die optimale ODT-Stärke innerhalb jedes Kanals während Datenausgabevorgängen zu bestimmen. Gleichzeitig passen sich die NAND-Geräte entsprechend den herstellerspezifischen Einstellungswerten an.

Die Umschaltoberfläche

Im Jahr unmittelbar nach der Veröffentlichung von ONFI 1.0 führten Samsung Semiconductors und Toshiba Memory Corporation (TMC), zwei der weltweit führenden NAND-Flash-Hersteller, den Toggle-Schnittstellenstandard als Alternative ein, um den Betrieb von Flash-Geräten über die Legacy-Funktionen hinaus zu steuern. Geräte, die die Toggle-Schnittstelle nutzen, arbeiten außerdem nach einer Reihe erweiterbarer, sorgfältig ausgearbeiteter Richtlinien in verschiedenen Hardwarekonfigurationen, Signalmustern und elektrischen Eigenschaften. Die Entwicklung des Toggle-Standards erfolgte im Rahmen kundenspezifischer Veröffentlichungen von NAND-Gerätespezifikationen von Samsung und TMC und nicht für die Öffentlichkeit. Dies stand im Gegensatz zum ONFI-Standard, der auf der Grundlage einheitlicher öffentlicher Veröffentlichungen seiner Arbeitsgruppe aktualisiert wurde.

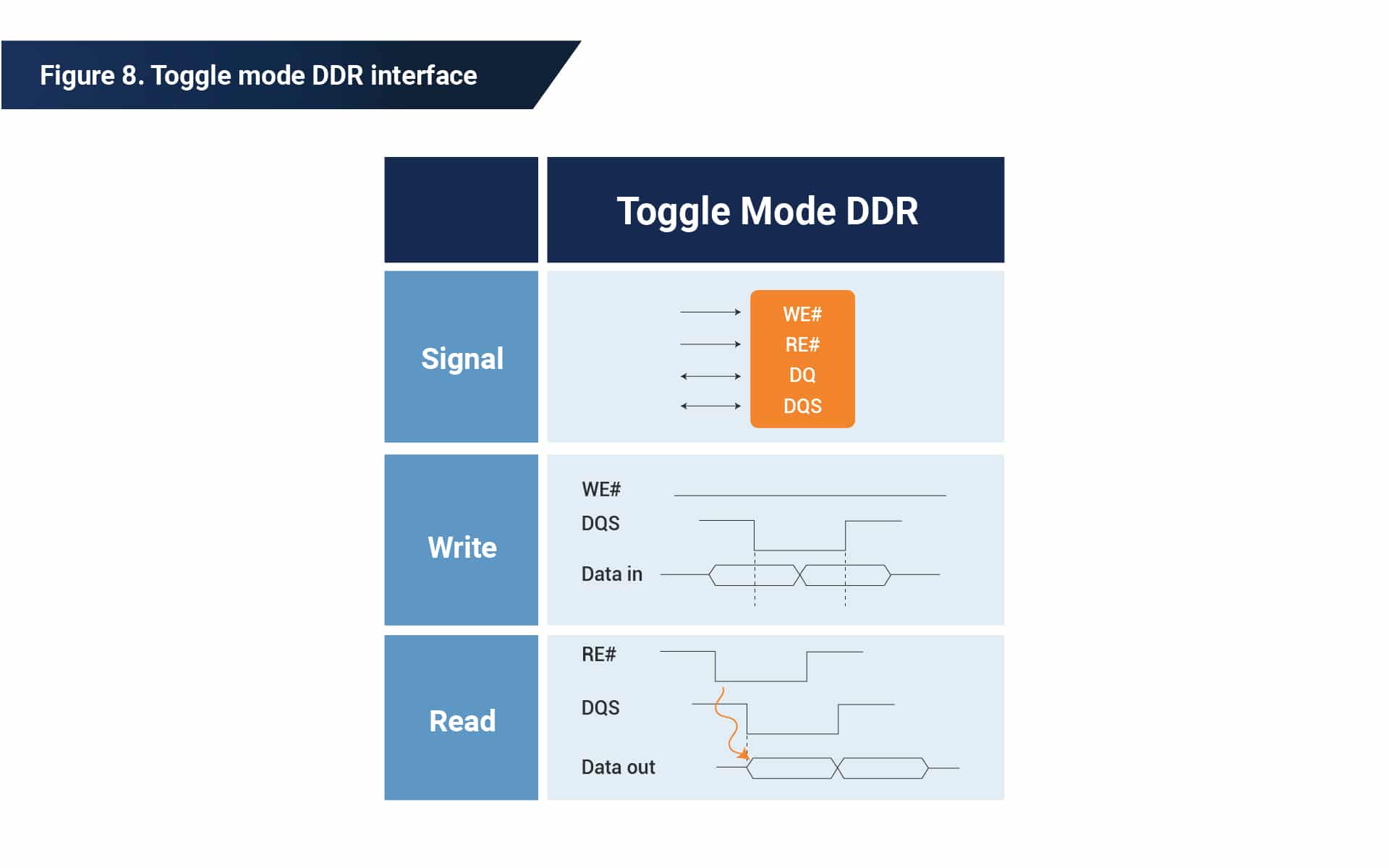

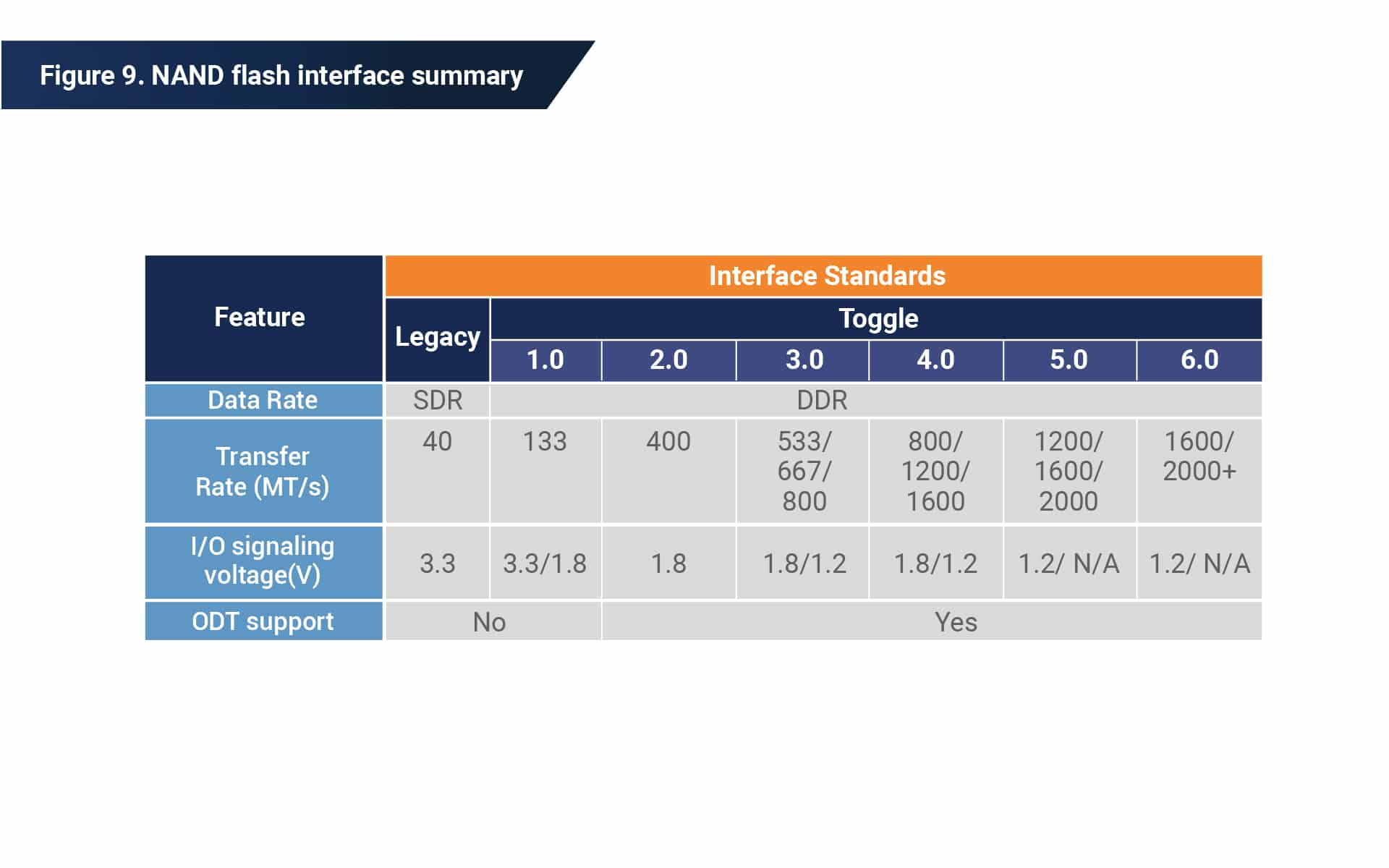

Umschalten 1.0

Auf den ersten Blick hatte die Toggle-DDR-Schnittstelle der ersten Generation einige allgemeine Merkmale mit der ONFI 2.0-Revision gemeinsam. Toggle 1.0 ermöglichte Datenübertragungsraten von bis zu 133 MT/s mithilfe bidirektionaler DQS-Strobe-Signale, wobei jede steigende und fallende Flanke einer Datenübertragung zugeordnet war. Der Unterschied zwischen ONFI und Toggle besteht jedoch darin, dass die Toggle-Datenübertragung ohne Taktsignal erfolgt, sodass sie nur beim Auftreten von Lese- und Schreibvorgängen asynchron zum Stromverbrauch erfolgt. Auch ONFI hat diese Implementierung mit ihrem Vorsprung in puncto Energieeffizienz und Designeinfachheit in Revision 3.0 übernommen.

Umschalten zwischen 2,0 / 3,0 / 4,0

Von Toggle 2.0 unterstützte Geräte ermöglichten einen Durchsatz von bis zu 400 MT/s und waren damit vergleichbar mit Geräten, die unter ONFI 3.0 betrieben wurden. Allerdings unterstützten je nach Veröffentlichungszeitpunkt nur ein Teil der Toggle 2.0-Geräte die ODT-Funktion.

Während Toggle 3.0-Geräte im Jahr 2015 mit unterstützten Übertragungsratenoptionen von 533 MT/s und 667 MT/s und vollständiger Unterstützung der ODT- und ZQ-Kalibrierungsfunktionen auf den Markt kamen, ist die Mainstream-Toggle-Standardrevision der Toggle 4.0-Standard. In ihrer frühesten Version ermöglichte die Toggle 4.0-Schnittstelle Übertragungsraten von bis zu 800 MT/s und 1200 MT/s und unterstützte gleichzeitig die notwendigen Funktionen, die ONFI entsprechen, allerdings mit unterschiedlichen Abbildungen je nach Produkt.

Natürlich waren die Schnittstellenstandards auf die neueste NAND-Flash-Technologie ausgerichtet, nämlich die BiCS-Serie für Kioxia (ehemals TMC) und Western Digital sowie die V-NAND-Serie für koreanische Anbieter wie Samsung und SK Hynix. Tatsächlich konnten die Flash-Anbieter mit der Einführung neuer Flash-Designs und -Technologien die Übertragungsraten optimieren, indem sie das Flash-Verhalten durch wiederholtes Ausprobieren innerhalb der Schnittstelle derselben Generation kalibrierten. Phison hat mit seinen Flash-Anbieterpartnern zusammengearbeitet, um den Durchbruch bei Übertragungsraten von über 2000 MT/s zu erreichen, zusammen mit verschiedenen Designverbesserungen, die zum perfekten Zeitpunkt kamen, da die Front-End-Leistung des Systems den Herausforderungen von Verbindungen der nächsten Generation gegenübersteht.

Wechseln Sie zwischen 5.0 und 6.0

Die Zukunft ist rosig, denn Entwickler stapeln eifrig die Bausteine im Buch der Standards für Flash-Schnittstellen. Da die 3D-Flash-Technologie offiziell in die Ära des 100-plus-Layer-Stacking eingetreten ist, erwartet die Branche einen bevorstehenden Übergang zu noch schnelleren und moderneren Schnittstellenaustauschgeschwindigkeiten. In Kürze werden die Schnittstellen Toggle 5.0 und 6.0 voraussichtlich mit Übertragungsraten von über 2400 MT/s laufen, was über 250 MB/s pro Chip entspricht. Angesichts der laufenden Diskussionen über Flash-Topologie und Designänderungen erwartet die Branche weitere Funktionserweiterungen und Verbesserungen, um die Mainstream-Standards voranzutreiben.

Die Zukunft von NAND-Flash

In den letzten 20 Jahren haben sich ONFI- und Toggle-NAND-Flash-Schnittstellen floriert und als Industriestandard für die Entwicklung von NAND-Flash-Anwendungen anerkannt. Ab 2021 haben die neuesten Versionen beider Standards die NAND-Flash-Leistung auf mehr als das Zehnfache der herkömmlichen Legacy-Fähigkeiten gesteigert und gleichzeitig eine höhere Modulkapazität und einen geringeren Stromverbrauch ermöglicht. Phison verfügt über mehr als 1900 weltweite Patente und 20 Jahre Erfahrung in der Flash-Branche und ist bereit, Unterstützung für Speichercontroller bereitzustellen, um den Anforderungen jeder Anwendung unter einer der beiden primären Schnittstellen gerecht zu werden.