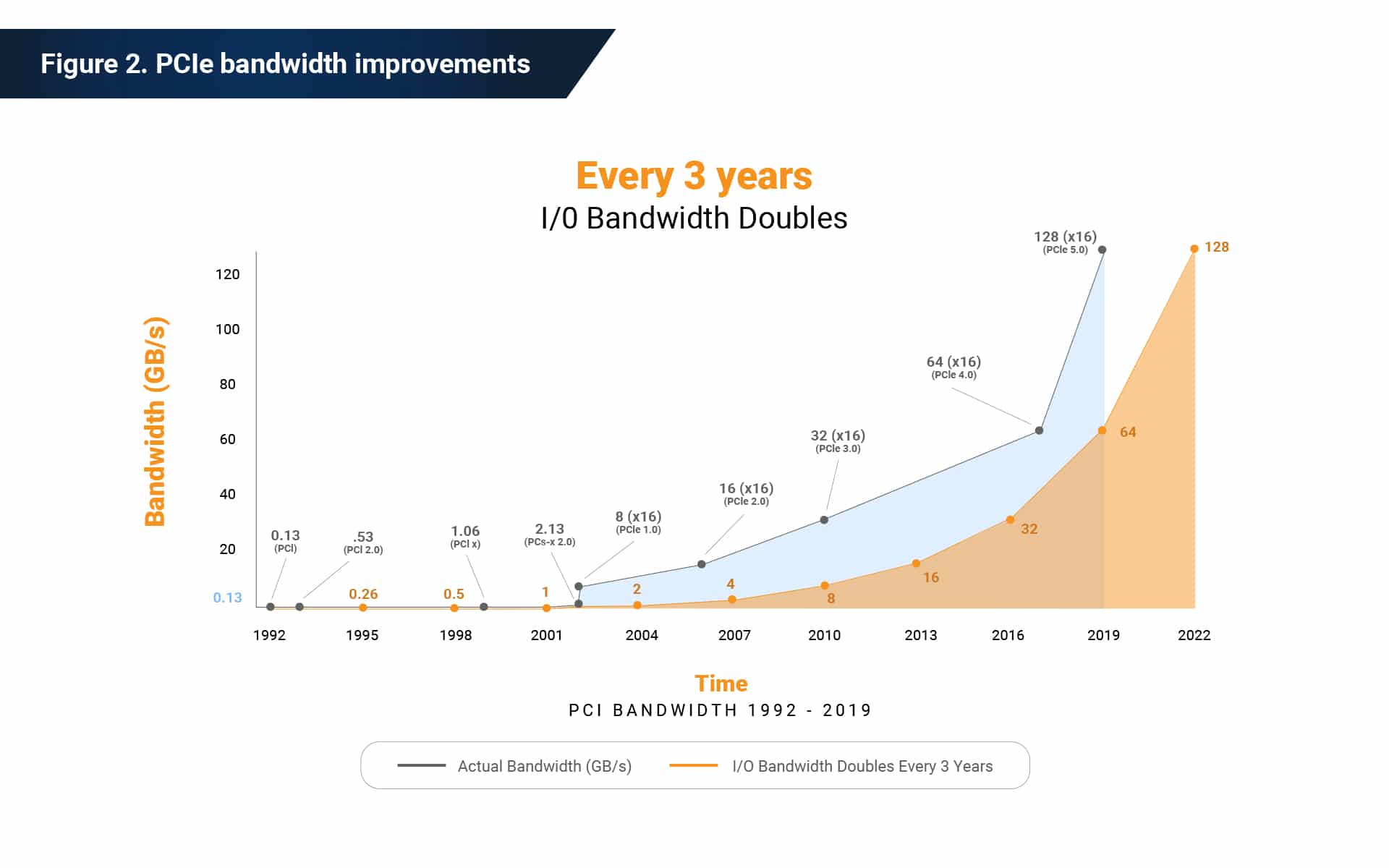

過去十年來,PCIe 一直是連接計算機主板上高速外圍硬件組件的標準接口,這已不是什麼新聞了。自最早發布以來,該標準每3到4年就會經歷一次穩定的傳輸速率升級和換代,但PCIe 4.0於2017年到來,引發了人們對技術創新的關注和熱情。從數據存儲的角度來看,“Gen 4”接口釋放了基於 PCIe 3.0 標準構建的 NVMe 固態硬盤 (SSD) 約 3 GB/s 的長期帶寬上限。接口升級鼓勵許多供應商推動更好的設計,以適應第四代接口並解決處理器層和存儲層硬件解決方案之間的瓶頸。

PCIe 接口和 Gen 4 基礎知識

從外圍組件的角度來看,PCIe接口就是我們所看到的組件模塊開發過程中的“前端”。良好的“前端”設計的最終目標是通過目標接口確保硬件模塊和計算機系統之間的穩健連接。

您可以將設計和開發過程分為兩個階段:硬件和固件。雖然人們很容易質疑自 2000 年代初以來 PCIe“前端”設計工作中的創新,但硬件和固件改進工作中的細節使得成熟的設計隨著每個接口規範的發布而脫穎而出。

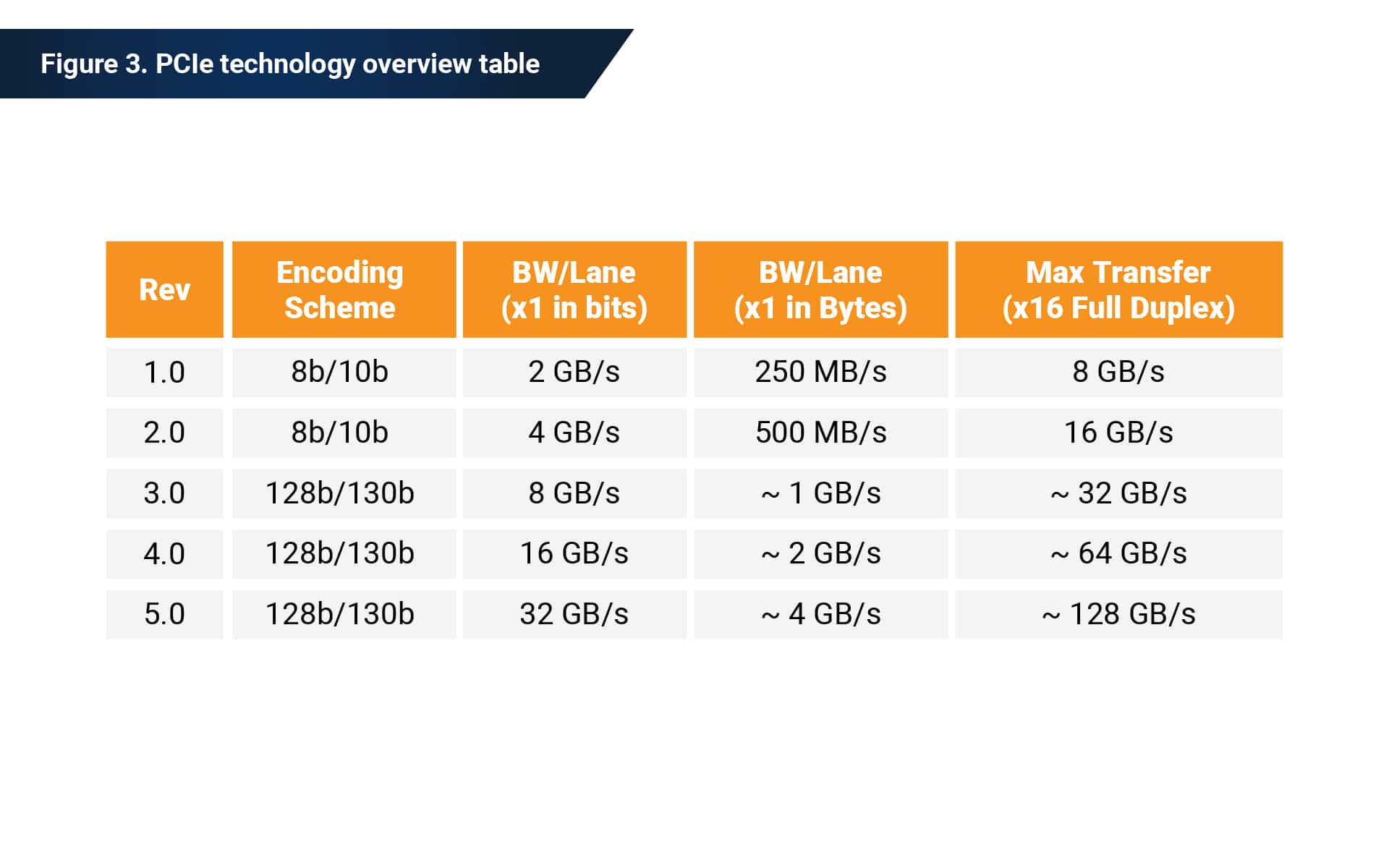

要了解“前端”設計主機,必須首先回顧一下PCIe接口硬件配置基礎知識。對於通過 PCIe 連接到主板的存儲組件,它採用通常稱為 x1、x4、x8 和 x16 插槽配置的硬件連接器之一。例如,Gen 4×4 配置表明連接器遵循 PCIe 基本規範修訂版 4.0 的必要設計和特性要求,同時通過 4 個 PCIe“通道”發送數據信號。每條通道都是雙向路徑,在一秒鐘內“閃爍”數十億個電信號。第 4 代 PCIe 通道以每秒 16 千兆傳輸 (GT/s) 的速度執行信號傳輸。雖然通過釋放高/低電壓的電信號來表示邏輯1和0,傳輸節點和接收節點之間可以交換一個“比特”的數據,但16GT/s表示在一秒內執行160億次。

此外,PCIe通道在“全雙工”機制下運行。即,兩個方向上的數據傳輸可以同時發生。因此,16 GT/s 的傳輸速率理論上表明,在第四代連接器上運行的功能強大的 PCIe 組件可以在其 32 個可用通道之一內在一秒內交換 320 億個數據位。

然而,計算中的問題是 PCIe 與許多其他數據傳輸硬件接口一樣,通過將時鐘信息編碼到數據流中來保護其數據。從 PCIe Gen 3 開始,採用 128 位至 130 位編碼方案進行數據保護。該方案需要在每 130 位傳輸中使用 2 位來存儲時鐘信息,以幫助識別和驗證鏈路接收側的數據。通過簡單的除法和乘法,16GT/s 變成每秒 157.54 億位的傳輸速率,通常稱為 15.754 Gb/s 的有意義數據位傳輸(忽略時鐘信息位)。

計算時鐘信息位可得出 16 Gb/s 的物理帶寬。然後,它可以以 8 位到 1“字節”的速率轉換為 4 GB/秒 (GB/s),這是模塊級帶寬和吞吐量領域中更常用的標準數據大小單位。此外,PCIe Gen 4 指令下的總帶寬可擴展至 64 GB/s,是上一代 PCIe 3.0 最大吞吐量的兩倍。

從這一進步的意義來看,計算機上輸入的字符的數據大小為 1 字節(或 8 位),而 PCIe Gen 4×16 接口可以在一個字節內交換一對 320 億字符的文件。第二。一部1080p 高清電影通常會堆積一個大約10 GB 的文件,而64 GB/s 的帶寬允許您將其中的三個文件從存儲複製到計算機,同時在理想的數據處理環境下在一秒鐘內將三個文件全部移出。儘管如此,PCIe閃存存儲瓶頸仍然遠低於16通道的滿容量。 2021年主流NVMe SSD主要採用x4配置,物理性能上限為8GB/s。

PCIe 規範概述

當前最廣泛採用的存儲接口不僅僅是性能指標。 PCIe協議監管的電信號監管了深入的功能和能力,包括但不限於:

-

-

- 接口初始化,

- 維護狀態跟踪,

- 互連電源管理,

- 車道測繪談判,

- 接口級數據編碼/解碼,

- 以及嵌入式時鐘調諧

-

除了物理層之外,還有另外兩個 PCIe 規範,它們對於正確的 SSD 前端操作同樣重要,甚至更重要。 “數據鏈路層”(或簡稱“鏈路層”)和“事務層”。正如“物理”一詞所表明的那樣,該層內的許多功能在很大程度上取決於存儲模塊的硬件設計。另一方面,理解上面兩層有助於了解前端相關的固件模塊。

緊接物理層之上的是數據鏈路層,負責與物理層配合,確保系統間信息交換的可靠。請注意“信息”而不是“數據”的措辭,因為該層內的工程重點已從數據信令中的物理視圖轉移到邏輯以及物理連接和鏈接的固件視圖。它與物理層的協作包括往返於物理層的電源狀態傳輸、鏈路級數據保護以及錯誤重試/記錄服務。

最後但並非最不重要的 PCIe 設計層是事務層,它對稱為事務層包 (TLP) 的數據包的移動進行操作。隨著 TLP 的生成和接收,事務層與 PCIe 鏈路的另一側交換流控制信息。更具體地說,它存儲由系統/存儲處理器生成的鏈路配置信息以及由物理層硬件生成的鏈路能力。此外,TLP的處理也是軟件和硬件啟動的電源管理機制的主要基礎。了解上面兩層有助於了解前端相關的固件模塊。

總而言之,事務層承擔著鏈路處理和電源管理的重任,需要同步的硬件和固件工作。

PCIe Gen 4 市場概覽

隨著PCIe架構分層設計模型的不斷完善,該規範制定了可擴展、可擴展的數據傳輸接口,並將繼續發展超越當前的措施。儘管隨著第5 代存儲控制器解決方案已於2021 年進入市場(以及新興的第6 代討論),下一代PCIe 的技術進步即將到來,但市場採用率仍會日復一日地立即為行業級存儲收入做出貢獻。

儘管 PCI-SIG 工作組已經將目光投向了第 4 代以外的領域,這已不是什麼秘密,但主流固態存儲市場仍處於第 4 代採用的鼎盛時期。從消費市場入手,AMD 在2019 年Computex 上率先推出搭載X570 芯片組的PCIe Gen 4 平台,奠定了第一家系統廠商的地位。同年,群聯率先推出全球首款PCIe Gen 4 閃存控制器,並搭載X570 芯片組。我們的 E16 解決方案將第三代性能拋諸腦後,以 5 GB/s 的吞吐量傳輸數據。

另一方面,英特爾宣布推出代號為 Rocket Lake 的新平台,該平台的發佈時間可能較晚,但在支持 PCIe 外設的性能方面卻有所落後。從Intel官方公佈的基準測試結果來看,PCIe Gen 4 SSD結合Rocket Lake平台,在2020年將Gen 4性能提升到了一個新的水平。

響應這一突破,群聯於同年晚些時候推出了更新的 E18 PCIe Gen 4 控制器解決方案,將 Gen 4 記錄推向了巔峰。它成為世界上第一個吞吐量超過 7 GB/s 的控制器解決方案。憑藉與兩家世界級CPU/平台供應商的持續牢固合作關係,群聯將隨時準備引領PCIe消費市場,並通過跨越台式機、筆記本電腦、遊戲和工作站市場的尖端存儲解決方案為其合作夥伴和客戶提供支持。

另一方面,機器學習、人工智能(AI)和深度學習等企業級和數據中心級高性能計算應用的持續增長,刺激服務器市場追求更強大的計算能力。需要具有可靠的一致性和可靠性的高性能存儲來確保穩定的服務質量,這是過渡到 PCIe Gen 4 存儲解決方案以滿足帶寬要求的絕佳機會。除了吞吐量需求之外,大多數企業和數據中心級用例都遵循嚴格的標準,這些標準可以調節穩定的性能,並且對壓力下超出規格的延遲的容忍度較低。

為了滿足這一需求,需要強大的硬件和固件設計能力來針對客戶應用進行微調,以實現 PCIe Gen 4 的無縫過渡。作為Gen 4解決方案市場的開拓者,群聯的工程團隊一直在苦心準備深入雲和高性能計算市場轉型,並通過釋放前端瓶頸來追求更高水平的存儲服務。

群聯在第四代應用領域取得了公認的成就,並為消費市場快速、及時地提供了第四代SSD解決方案。我們將投入同樣的注意力和工程資源來支持企業市場應用的第 4 代和第 5 代過渡。