2013년 Apple은 PCIe SSD가 장착된 최초의 MacBook Pro를 출시하여 PCIe 기반 SSD의 영역을 소비자 애플리케이션으로 공식적으로 확장했습니다. 그러나 PCIe 기반 SSD는 높은 대역폭과 확장성 때문에 그 이전부터 서버와 데이터 센터에서 이미 발견되었습니다.

최신 3D NAND 플래시 기술을 통해 PCIe SSD는 더 저렴해졌으며 소매 및 소비자 애플리케이션에서 더 많이 채택되었습니다. 그러나 가격과 성능만이 소비자와 기업이 SSD로 전환하는 유일한 이유는 아닙니다. 데이터 보호도 필수 요소입니다.

SSD 엔드투엔드 데이터 보호

3D TLC 또는 QLC와 같은 고급 플래시 프로세스 기술을 통해 드라이브는 매우 매력적인 소매 가격으로 테라바이트의 데이터를 쉽게 저장할 수 있습니다. 그러나 PCIe SSD 컨트롤러가 데이터를 보호하는 방법은 저장된 데이터의 양이 두 배 또는 세 배가 되기 때문에 드라이브 성능과 마찬가지로 중요합니다.

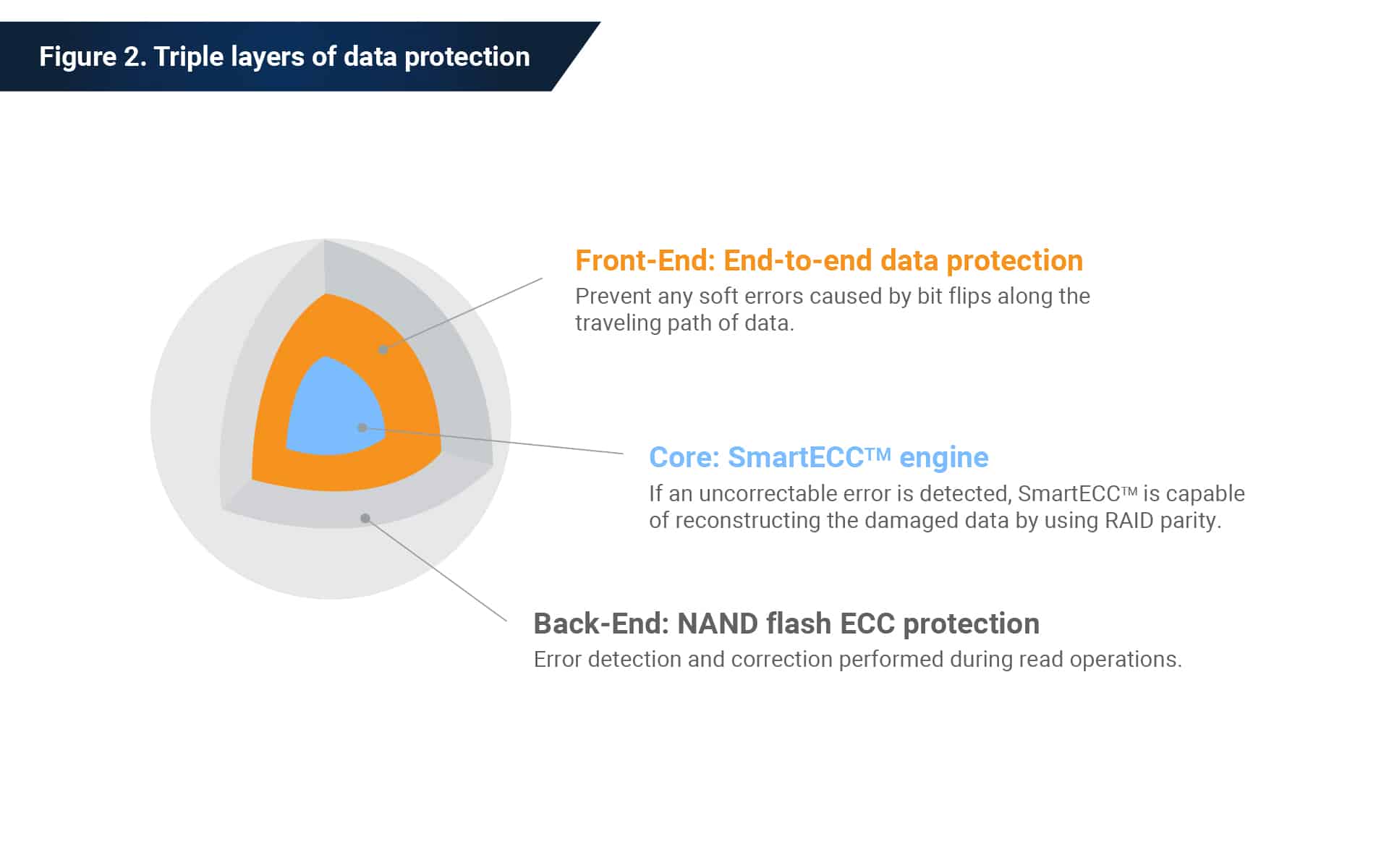

을 위한 Phison PCIe SSD, 데이터 보호는 세 가지 수준으로 구성됩니다.

-

-

- 프런트엔드: ETEDP(End-to-End Data Protection)는 읽기 및 쓰기 작업 모두에서 데이터를 보호합니다.

- 핵심: SmartECCTM 엔진은 RAID 메커니즘을 사용하여 잘못된 데이터를 복구합니다.

- 백엔드: NAND 플래시 ECC 보호는 읽기 작업 중에 오류 감지 및 수정을 수행합니다.

-

ETEDP라고도 하는 종단 간 데이터 보호는 데이터 전송 시 소프트 오류를 감지하도록 설계되었습니다. 데이터를 NAND 플래시에서 읽거나 쓸 때 데이터 전송 중에 데이터가 임시로 저장되는 여러 단계가 있습니다. 따라서 플래시 스토리지에는 단일 이벤트 오류를 유발할 수 있는 비트 플립 또는 노이즈가 있을 수 있습니다. 컨트롤러는 이러한 오류가 언제 발생하는지 알고 가능한 경우 조치를 취해야 합니다.

쓰기 작업 보호

데이터가 NAND에 기록되면 호스트 IP(PCIe 및 NVMe IP)에서 데이터 버퍼(DRAM 및 SRAM), 플래시 IP, 마지막으로 NAND 플래시로 이동합니다.

호스트가 쓰기 명령을 내리면 먼저 데이터가 호스트 IP로 이동됩니다. 데이터는 CRC에 대해 확인되며 일치하는 경우 데이터 자체에 E2E 패리티(데이터의 논리 블록 주소(LBA)를 기반으로 생성됨)가 추가됩니다. 데이터가 Data Buffer로 이동하면 해당 데이터는 SECDED(Single Error Correction, Double Error Detection)로 보호되며 내부 ECC 엔진이 잘못된 데이터를 복구할 수 있습니다. Flash IP의 경우 데이터를 확인하고 CRC 및 LDPC 코드를 추가합니다. 마지막으로 패리티가 있는 모든 데이터는 NAND 플래시에 한 번에 기록됩니다.

읽기 작업 보호

호스트에서 데이터를 읽을 때 데이터는 NAND에서 플래시 IP, 데이터 버퍼, 마지막으로 호스트 IP로 이동합니다.

수정 엔진의 설계에 따라 얼마나 많은 오류를 복구할 수 있는지가 결정됩니다. 읽기 작업 중에 데이터는 먼저 Flash IP에서 LDPC 및 CRC를 확인합니다. 데이터가 올바르면 ECC 패리티가 분리되고 그에 따라 데이터가 다른 IP로 이동합니다. 쓰기 작업과 마찬가지로 데이터 버퍼 및 호스트 IP에서 데이터의 정확성을 확인합니다. 데이터가 올바르면 E2E 패리티가 분리되고 데이터가 호스트로 전송됩니다.

Phison은 데이터를 안전하게 유지합니다.

3D NAND 공정 기술을 통해 고객은 SSD의 고성능 및 용량과 더 나은 내구성 및 데이터 안정성을 원합니다. 데이터 보호 측면에서 목적을 달성하는 방법에는 여러 가지가 있지만 종단 간 데이터 보호는 일반적으로 PCIe 컨트롤러 내에서 실행됩니다. 종단 간 데이터 보호의 목적은 읽기 및 쓰기 작업의 데이터 전송 중에 소프트 오류 감지를 위해 패리티를 생성하고 데이터에 추가하는 것입니다.