この記事は、Phison の最も重要な製品の 1 つである集積回路 (IC) を詳しく調査するシリーズの 3 回目で最終回です。 第二弾 NAND フラッシュ コントローラー IC の機能ブロック図を示しながら、基本的な IC 設計プロセスを紹介しました。この最後の記事では、Phison の IC 設計の世界にさらに一歩踏み込みます。

私たちが議論したように、 前の記事 IC 設計に関しては、IC がターゲット アプリケーションを「中心に」設計されることが重要です。そのためには、設計者は回路が達成する必要がある機能を理解する必要があります。そうして初めて、電力パラメータ、メモリ容量、しきい値、環境適応性などの量的および質的変数に厳密に対処するための詳細な仕様のリストをまとめることができます。

特定の機能ブロックと要件は、意図された使用例とアプリケーションに応じて大きく異なる場合があります。ただし、一部の一般的な機能ブロックは、特定のアプリケーションの設計で共通になる場合があります。これを説明するために、フラッシュ メモリ コントローラーに進む前に、AI および 5G アプリケーション用の IC 設計の例をいくつか見てみましょう。

AIおよび5Gアプリケーション向けのIC設計

多くの AI アプリケーション中心の IC にとって、重要な機能ブロックはデジタル信号処理 (DSP) エンジンです。これは、行列の乗算や畳み込みなどのアルゴリズムに必要な複雑な数学演算の実行を担当するハードウェア エンジンです。これらの演算は、コンピューターの機械学習や深層学習中に常に大量に発生する計算の重要なステップです。

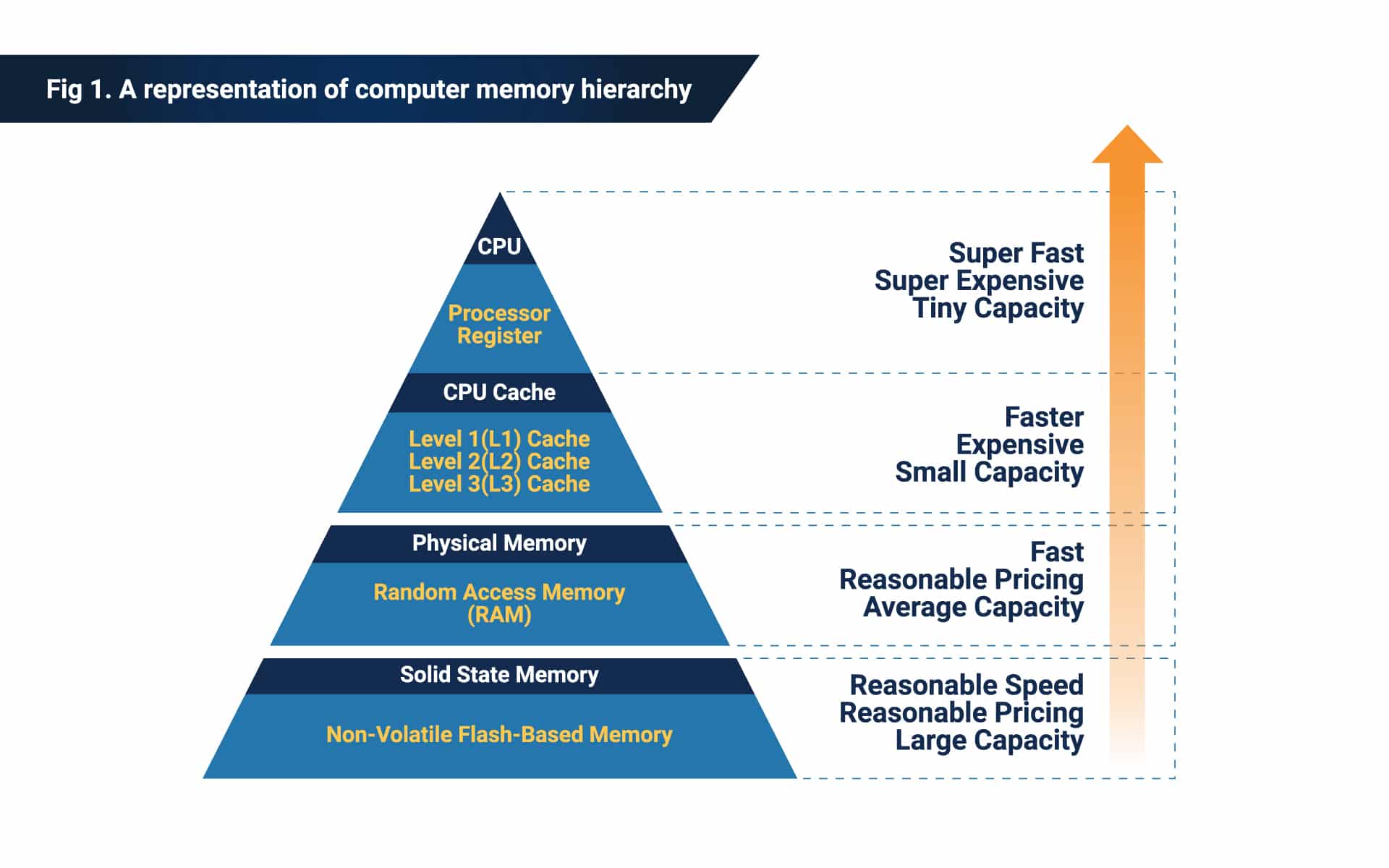

コンピューティング システムのコンピューティング エンドの裏側にはメモリ エンドがあります。すべてのコンピューティング システムには、中間パラメータや計算結果を一時的に保存するための何らかのハードウェア スペースが必要です。 AI アプリケーションの場合、計算とトレーニングの間に生成された一時データをすぐに取得したり、後で使用するために保管したりできることが重要です。したがって、AI アプリケーション向けに設計されたほとんどの IC チップには、最高速のメモリ ハードウェアと、単一ビットのデータを超高速で保存できる多数のレジスタを備えた、高速な意思決定を行う優れたメモリ インターフェイスが必要です。

AI アプリケーション中心の IC には、ニューラル ネットワーク推論などの要求の高いワークロードをサポートするためのいわゆる「ハードウェア アクセラレータ」が搭載されていることが多いため、処理とデータ ストレージに必要な速度に加えて、ある程度の速度が追加されることも貴重です。これらのアクセラレータは通常、メイン プロセッサに追加された特殊な回路であり、特定の計算ミッションを並行して実行するために、多くの場合ビジーで大きなタスクで負荷がかかります。アクセラレータによるこのオフロード効果は、メイン プロセッサ内でのタスク間の切り替えによって生じるエネルギー消費と遅延を削減しながら、チップの効率を向上させ、AI アプリケーションの全体的なパフォーマンスを向上させるのに役立ちます。

別の例として、5G アプリケーション中心の IC を考えてみましょう。このタイプの IC の主な焦点は、高速ワイヤレス接続とデータ転送を可能にすることです。設計の主要な機能ブロックには、無線信号のエンコードとデコードを担当するデジタル ベースバンド処理ユニットと、無線通信中に必要なアンテナとアナログ信号の送受信を担当する無線周波数 (RF) フロントエンドが含まれます。

さらに、5G 用に設計された IC は、複数のアンテナの制御を介してワイヤレス信号を特定のデバイスに送信するビームフォーミングなどの高度な機能をサポートしていることがよくあります。このような制御メカニズムを実装するには、回路内に MIMO (複数入力、複数出力) 機能ブロックを実装し、複数のアンテナからの信号シーケンスを適切に指示する必要があります。

対象となるアプリケーションの違いにもかかわらず、IC の設計に使用される特定の側面やプロセスによって、一見異なる IC タイプ間に相関関係が生じます。たとえば、AI IC とフラッシュ メモリ コントローラ IC は両方とも、最適なパフォーマンスを達成するために効率的なメモリ インターフェイスを必要とします。この区別は、関連するメモリ デバイスがメモリ階層のどこに分類されるかだけです。 5G IC に関して言えば、堅牢な MIMO 信号システムの設計は、NAND フラッシュ ストレージ フロントエンドのデータ フローを制御する先入れ先出し (FIFO) バッファーの実装と微妙な類似点を持っています。 2 つの設計間に直接の関係はありませんが、操作された入力で目的の出力を生成する別個のバッファ回路が両方とも含まれています。

SSDのフラッシュメモリコントローラ用IC設計

汎用 SSD NAND フラッシュ メモリ コントローラ IC には、次のような特定の機能ブロックが含まれています。

-

-

- フロントエンド相互接続

- 中央エンジン

- バッファおよびストレージメディア管理ユニット

- 周辺機器の相互接続

- 信頼性保証とセキュリティ機能のための複数の暗号化エンジン

-

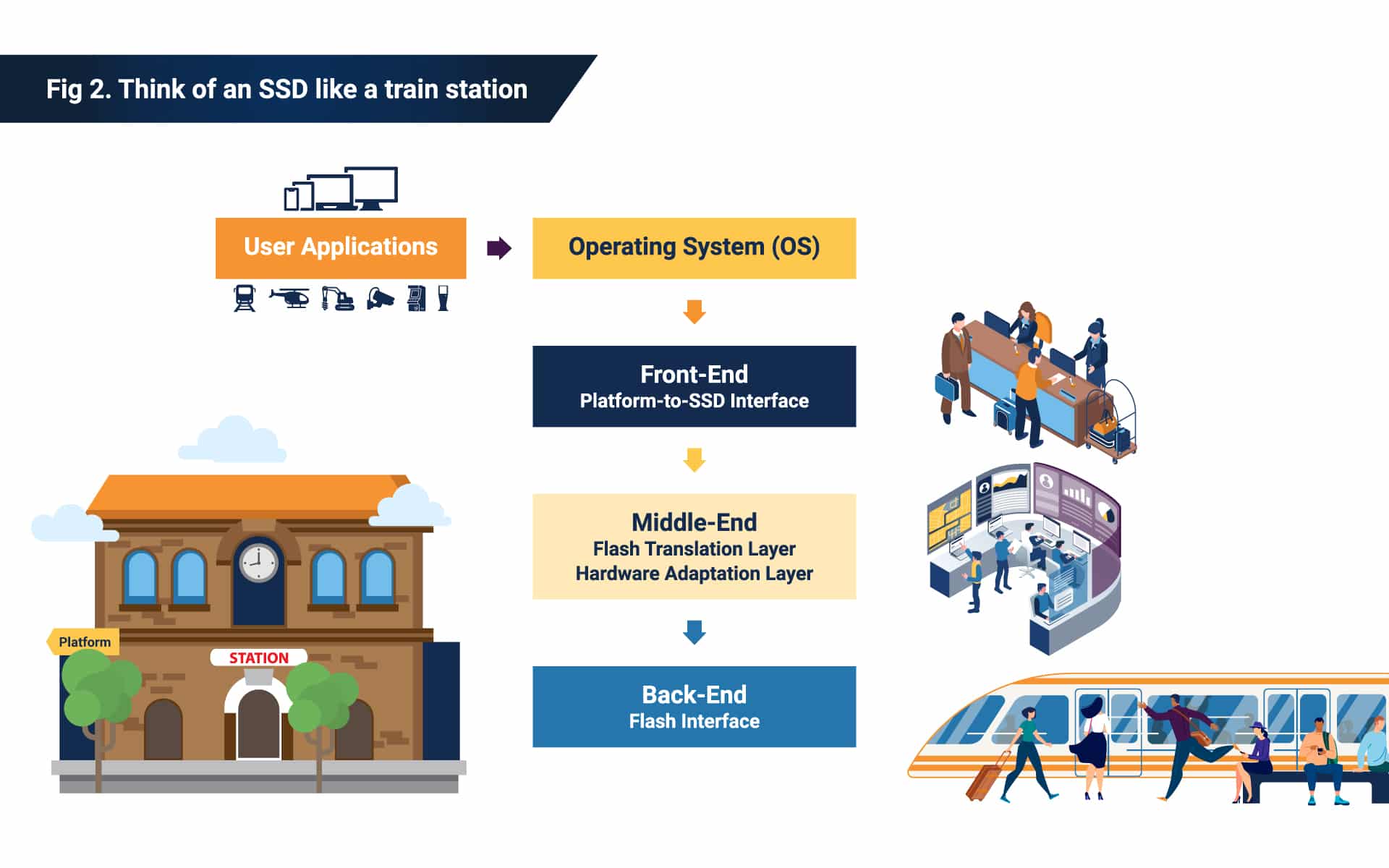

これらのブロックは連携して、信頼性の高いデータ ストレージ デバイスとして SSD が効率的に動作するようにします。それがどのように起こるかをよりわかりやすく説明するために、鉄道の駅に例えてみましょう。鉄道の駅に旅行者向けにさまざまなエリアやセクションがあるのと同じように、データを処理するための SSD の操作も、フロントエンド、ミドルエンド、バックエンドのいくつかの部分に分けることができます。

フロントエンド

SSD のフロントエンドは、駅のフロント ロビーのようなものだと考えてください。サービスに発券、手荷物預かり、さらには清掃サービスが含まれる駅のロビーと同様に、SSD のフロントエンドは、受信信号に対する多くの事前処理サービスを備えたデータのエントリ ポイントとして機能します。これらのサービスには、ターゲットの送信インターフェイス (SATA、SAS、または PCIe など) を介した信号リンクの確立、プロトコル準拠のデジタル信号変換、および接続検証の各種ルーチンが含まれます。

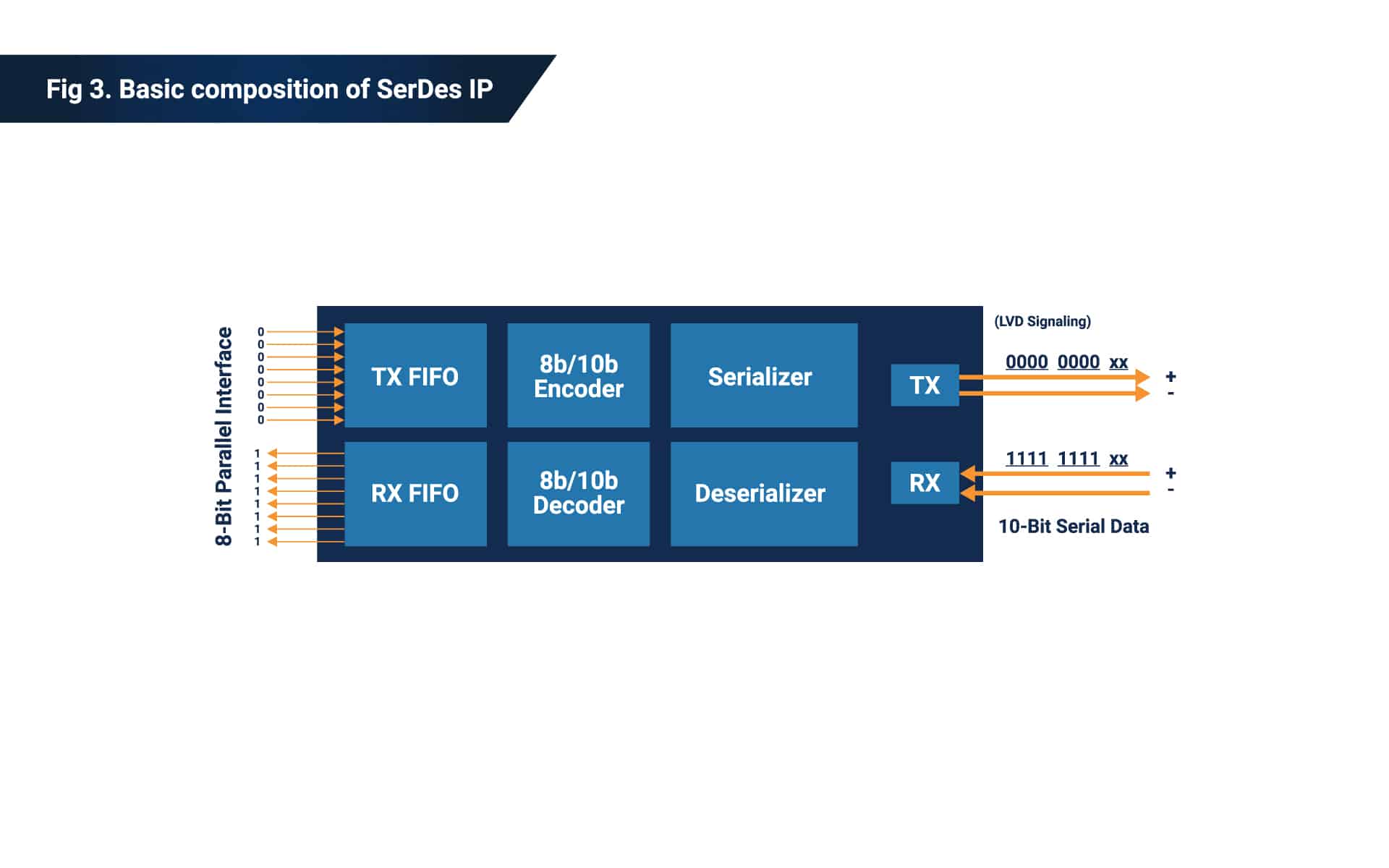

これらのサービスを提供するには、多くの汎用および特許取得済みの小型回路 (IP と略されることが多い) を NAND フラッシュ メモリ コントローラ IC チップ上に実装する必要があります。 Phison 独自の SSD コントローラ ソリューションのフロントエンド IP の一例は、 セルデス (Serial-and-Deserializer の略) は、受信パラレル データ ビット (異なる物理ピンを同時に経由して送信されることを意味します) をシリアル ビットストリームに変換する、またはその逆の変換を行います。 SerDes の構成には、データ フロー管理のための FIFO キャッシュと、プロトコル準拠のための 1 組のコーダーが含まれています。 Phison は、業界最高のナノメートルスケールの製造プロセスに基づいて構築された、主流の SSD 伝送インターフェイス向けの独自の包括的な SerDes IP ポートフォリオを持ち、SSD フロントエンドをフルパワー化します。

ミドルエンド

ミドルエンドは主にキャッシュとストレージ メディアの管理を担当します。 SSD の内部には、DRAM と NAND フラッシュという 2 つの主要なメモリ コンポーネントが組み込まれています。 DRAM は一時データを配置できるキャッシュ スペースとして機能し、NAND フラッシュはデータを長期間保存するストレージ メディアです。ミドルエンドは、システムの中心として機能する SSD にとって非常に重要です。駅の指令員やアナウンサーが乗客を一時的な待合室や長距離の列車に誘導するのと同じように、SSD IC はデータを一時記憶域の場合は DRAM に、長期記憶域の場合は NAND フラッシュに送信します。

中央ディスパッチ オフィスとしての役割を果たすには、フラッシュ変換層 (FTL) とハードウェア アダプテーション層を実装して、メモリ デバイス上のデータ配置を連携させる必要があります。 FTL は、帳簿上のデータをフラッシュ メモリ上の正しい物理的な場所にマッピングする責任があります。同様に、テーブル管理とマッピングの同様のメカニズムが、DRAM への一時データにも採用されています。 FTL レイヤーとハードウェア アダプテーション レイヤーはどちらも、SSD の全体的なパフォーマンスに重大な影響を与える可能性がある重要なファームウェア機能です。これらは、コントローラー IC の設計内で慎重に計画する必要がある強力な中央ハードウェア エンジンによって駆動されます。

ミドルエンドのニーズに対応するために、Phison には、中央のディスパッチャを支援する独自の方法を提供するハードウェア IP が多数あります。それらには、 CoXプロセッサ™ そして メモリインターフェイスIP これにより、Phison の NAND フラッシュ コントローラー IC は各世代の製品で他の製品よりも優れたパフォーマンスを発揮できるようになります。

バックエンド

NAND フラッシュ メモリ コントローラ IC のバックエンドは、NAND フラッシュ メモリに関するものです。前述したように、NAND フラッシュ メモリ チップは、駅に例えると電車に相当します。車内サービスは、旅行体験全体の観点から、駅での案内や案内と同じくらい重要です。 NAND フラッシュ コントローラー IC 設計の大部分は、NAND インターフェイス プロトコルへの準拠、耐久性の維持、エラー訂正などの車内サービスに焦点を当てています。

NAND フラッシュ コントローラーが NAND フラッシュ インターフェイス プロトコルに準拠できるということは、さまざまな列車モデルを完璧かつ効率的に運転できる熟練した電車の運転士がいることに似ています。 Phison は、主流プロトコル ONFI および Toggle の最新インターフェイス仕様と互換性のある強力な IP ポートフォリオを備えています。 Phison の NAND フラッシュ メモリ コントローラ IC は、蓄積されたハードウェアおよびファームウェア IP を使用して、楽にスムーズなペースと制御で NAND フラッシュを駆動します。

私たち全員が旅行中に経験したことがあるように、座席を見つけたり、正しい電車に乗ったりすることさえ間違えることがあります。NAND フラッシュ メモリ内の電子の形でのデータも同様です。 NAND フラッシュ セルの固有の物理的特性により、電子が NAND フラッシュ セルから漏れることがあり、動作中や時間の経過とともにデータ ビット エラーが発生する可能性があります。したがって、NAND フラッシュの高い耐久性と信頼性を維持することは、優れた NAND フラッシュ メモリ コントローラー IC バックエンド設計のもう 1 つの重要な要件です。

高い信頼性と品質を実現するには Phison IC を選択してください

ファイソン 同社は、ハイエンド SSD 製品本来の最高の寿命を保証するために、市場から最もプレミアムな NAND フラッシュ ソリューションを選択し、高度な製品の強力なポートフォリオで品質の伝統を強化しました。 エラー訂正コード (ECC)。専門的で親切な車内サービス員が乗客を支援するのと同じように、Phison の高度な ECC は、何世代にもわたって絶えず改良されているファームウェア アルゴリズムと専用の数学的計算用のハードウェア エンジンに基づいて、漏れ出た電子や NAND フラッシュ ビット エラーを簡単に処理します。