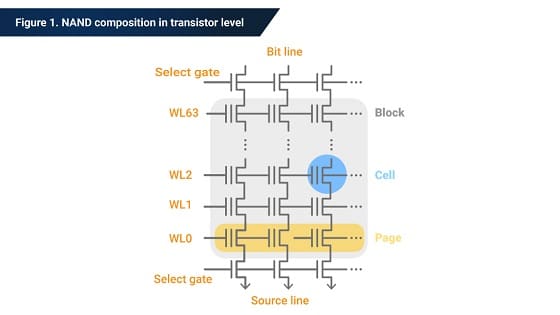

NAND フラッシュは、ゲート内に電子を捕捉する数百万個のフローティング ゲート トランジスタで構成される不揮発性メモリです。これらのフローティング ゲート トランジスタはメモリ セルと考えることができます。数百万のメモリセルが接続されると、アレイが形成されます。各配列はブロックで構成され、各ブロックには多数のページが含まれます。

図 1 は、NAND アレイの概略図を示しています。

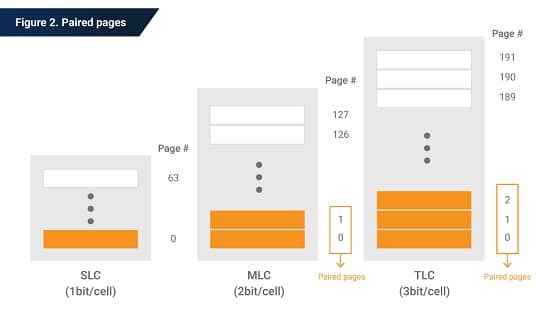

各ワードライン (WL) は、NAND の読み取り/プログラム操作の基本単位であるページを構成します。ただし、各 WL のページ数は、シングルレベル セル (SLC)、マルチレベル セル (MLC)、およびトリプルレベル セル (TLC) タイプの NAND では異なります。

図2は、MLC NANDでは同じWLを共有する2つのページ(下位ページと上位ページ)と、TLC NANDでは同じWLを共有する3つのページ(下位、中位、上位ページ)を示しています。同じ WL を共有するページはペアページと呼ばれます。

NAND フラッシュの物理的特性のため、NAND プログラミング操作では次の 2 つの黄金律に従う必要があります。

- プログラミング操作は、NAND フラッシュの特性に基づいて指定された順序に従う必要があります。

- ワード線 (WL) でのプログラミング操作が完了していない場合、この WL のデータの整合性は保証できません。

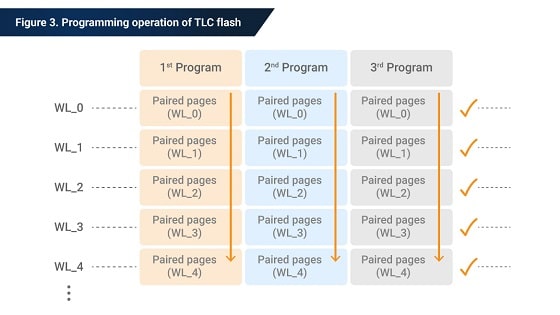

MLC または TLC NAND フラッシュの場合、単一ページのデータ プログラミングは 1 ステップの操作ではありません。データ プログラミング要件を達成するには、MLC/TLC ページを 2 ~ 3 回プログラムする必要があります。この現象はフラッシュメモリの物理的特性です。

ペアページのユーザーデータの整合性に関する懸念

現在の消費者向けソリッド ステート ドライブ (SSD) 市場では、MLC および TLC フラッシュが最も人気のあるメモリ タイプです。 MLC および TLC フラッシュは、特に TLC において、より大きなストレージ容量を低コストで提供できます。ただし、MLC および TLC フラッシュでのプログラミング操作は SLC よりも複雑です。 TLC フラッシュを例にとると、操作全体を完了するには、同じ WL 上のペア ページを 3 回プログラムする必要があります。

図 3 は、TLC フラッシュの完全なプログラム動作を示しています。 WL_x での 3 回目のプログラミング操作が終了した場合にのみ、WL_x に格納されたデータは信頼できるデータになります。

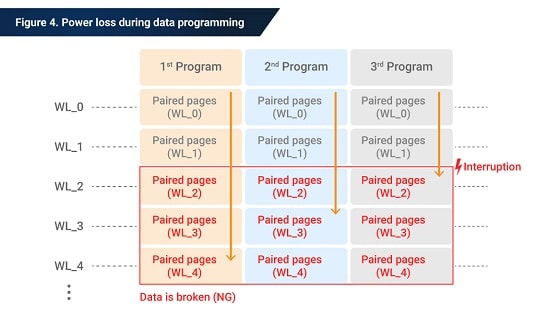

残念ながら、このプログラミング操作の複雑さにより、データ破損のリスクが増大します。データの整合性はプログラミング シーケンス全体 (つまり、最初のプログラム + 2 番目のプログラム + 3 番目のプログラム) が完了した後にのみ発生するため、プログラミング操作の完了前に予期せぬイベントが発生すると、データの破損または損失が発生します。

図 4 は、予期しないイベントによってデータ プログラミング操作が中断された場合に何が起こるかを示しています。この場合、WL_2 のプログラミング動作が完了する前に電力損失が発生するため、WL_0/WL_1 に格納されているデータのみが保証されます。つまり、電力損失により他のデータが破損する可能性があります。

Phison 独自のテクノロジーである Academic Flush™ は、プログラミング操作中の予期せぬ中断によるストレージ デバイスのデータ破損を防ぐために設計されています。

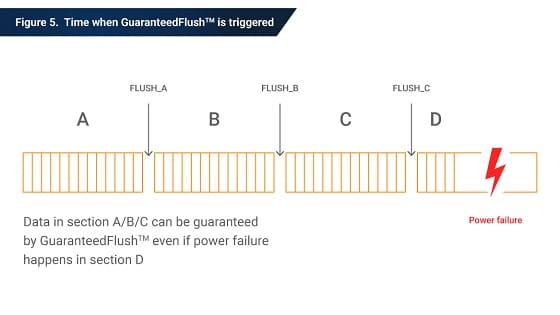

Academic Flush™ は、単一のデータ プログラミング コマンドごとに実行されるわけではありません。代わりに、ストレージ デバイスが FLUSH_CACHE コマンドを受信すると、AcademicedFlush™ がバックグラウンドでトリガーされます。したがって、FLUSH_CACH コマンドの前にデバイスにプログラムされたすべてのデータの整合性が、このテクノロジーによって保証されます。

図 5 は、GuarrantedFlush™ がカバーできるユーザー データ範囲を示しています。

Academic Flush™ は、多層アルゴリズムの実装です。突然の停電からユーザーのデータを保護するために使用される基本的な方法が 2 つあります。

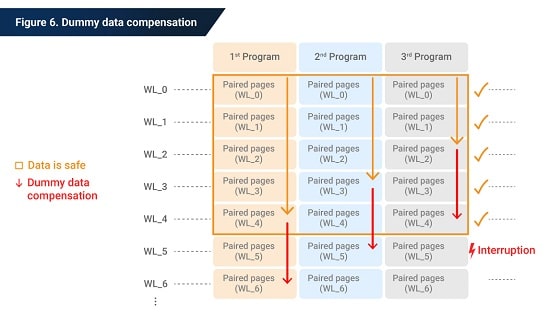

コンセプト1:ダミーデータ補正

1 つ目の方法は、プログラミング操作を高速化することです。 NAND フラッシュ タイプが異なれば、プログラミング シーケンスも異なる場合があります。プログラミング シーケンスがどのように変化しても、単一の WL でのデータ プログラミングの継続時間によって、予期せぬ中断によるデータ損失のリスクが決まります。この時間が長くなると、中断が発生する可能性が高くなります。この問題に対処するために、図 6 に示すように、特定の WL にダミー データを挿入して、ユーザー データを保存する WL がプログラミング動作全体 (つまり、1 番目のプログラム + 2 番目のプログラム + 3 番目のプログラム) を完了できるようにします。

以下の WL にダミー データを挿入することで、ユーザー データのプログラミング操作を完了できます。このようにして、予期しないイベントによって今後のプログラミング シーケンスが中断された場合でも、ユーザー データの整合性が保証されます。

コンセプト 2: リアルタイム データ バックアップ

ペア ページ効果によるデータ破損から SSD を保護する 2 番目の方法は、そもそもペア ページの問題が発生することなく、データをページに直接バックアップすることです。 SLC モードとして設定されたページは、この要件を満たすことができます。これは、ユーザー データを安全に保つための根本的な方法のように思えるかもしれません。ただし、SLC モードの容量は TLC メモリの 3 分の 1 です。リアルタイム データ バックアップの実装は別の問題になります。

安全なデータのために Phison を選択してください

AcademicFlush™ は、予期せぬ電力損失時にデータの正確性を確保するために設計されたもう 1 つの Phison 独自のテクノロジーです。 AcademicFlush™ は Phison SSD 製品の信頼性を強化します。

よくある質問(FAQ):

TLC NAND は SLC よりもデータ破損が発生しやすいのはなぜですか?

TLCはセルあたり3ビットを保存し、ページ間でワードラインを共有します。これにより3回のプログラミング操作が必要となり、不完全な書き込みのリスクが高まります。 書くSLC では 1 回のプログラミング サイクルのみが必要なため、このリスクは大幅に軽減されます。

GuaranteedFlush™ におけるダミーデータ補正とは何ですか?

ダミーデータは事前に書き込まれます その後 ワードラインは、実際のユーザーデータのプログラミングを高速化します。これにより、プログラムシーケンス全体が迅速に完了し、電源喪失のリスクを軽減します。

リアルタイムデータバックアップとダミーデータ補償の違いは何ですか?

リアルタイムバックアップは、ユーザーデータをSLCモードページに直接保存します。 しない ペアページ効果の影響を受けます。TLCプログラミングの複雑さは回避できますが、 容量SLC ではセルあたりに保存されるデータが少なくなるためです。

なぜリアルタイムデータバックアップが排他的に使用されないのですか?

SLCモードではストレージ密度が大幅に低下します, これを独占的に使用すると、TLC NAND の使用可能容量が 3 分の 2 減少します。 ファイソン バックアップの使用と他の技術とのバランスをとる 保持 容量 そしてパフォーマンス。

GuaranteedFlush™ は Phison のエンジニアリング哲学をどのように反映していますか?

それ ショーケース フィソンの コントローラレベルのイノベーションとデータ整合性に重点を置いています。NANDの動作に合わせてファームウェアレベルの保護を設計することで、 ファイソン OEM およびエンタープライズ ユーザーに、優れた電源喪失耐性を備えた信頼性の高い低レイテンシのストレージを提供します。