Dieser Artikel ist der dritte und letzte einer Reihe, die sich eingehend mit einem der wichtigsten Angebote von Phison befasst: dem integrierten Schaltkreis (IC). Unser zweiter Teil stellte grundlegende IC-Designprozesse mit einer Illustration eines Funktionsblockdiagramms eines NAND-Flash-Controller-ICs vor. In diesem letzten Artikel führen wir Sie einen Schritt weiter in die Phison-Welt des IC-Designs.

Wie wir in unserem besprochen haben Vorheriger Artikel Beim IC-Design ist es wichtig, dass ICs „um“ Zielanwendungen herum entworfen werden. Dazu müssen Designer die Funktionen verstehen, die die Schaltkreise erfüllen müssen. Nur dann können sie eine Liste detaillierter Spezifikationen zusammenstellen, um quantitative und qualitative Variablen wie Leistungsparameter, Speicherkapazität, Schwellenwerte, Anpassungsfähigkeit an die Umgebung usw. genau zu berücksichtigen.

Spezifische Funktionsblöcke und Anforderungen können je nach beabsichtigtem Anwendungsfall und Anwendung stark variieren. Einige allgemeine Funktionsblöcke können jedoch im Design für bestimmte Anwendungen gemeinsam sein. Um dies zu veranschaulichen, werfen wir einen Blick auf einige Beispiele des IC-Designs für KI- und 5G-Anwendungen, bevor wir uns den Flash-Speicher-Controllern zuwenden.

IC-Design für KI- und 5G-Anwendungen

Für viele anwendungsorientierte KI-ICs ist die digitale Signalverarbeitungs-Engine (DSP) ein kritischer Funktionsblock. Hierbei handelt es sich um eine Hardware-Engine, die für die Durchführung komplexer mathematischer Operationen verantwortlich ist, die für Algorithmen wie Matrixmultiplikation und Faltung erforderlich sind. Dabei handelt es sich um wesentliche Berechnungsschritte, die beim maschinellen Lernen am Computer und beim Deep Learning ständig und in großen Mengen stattfinden.

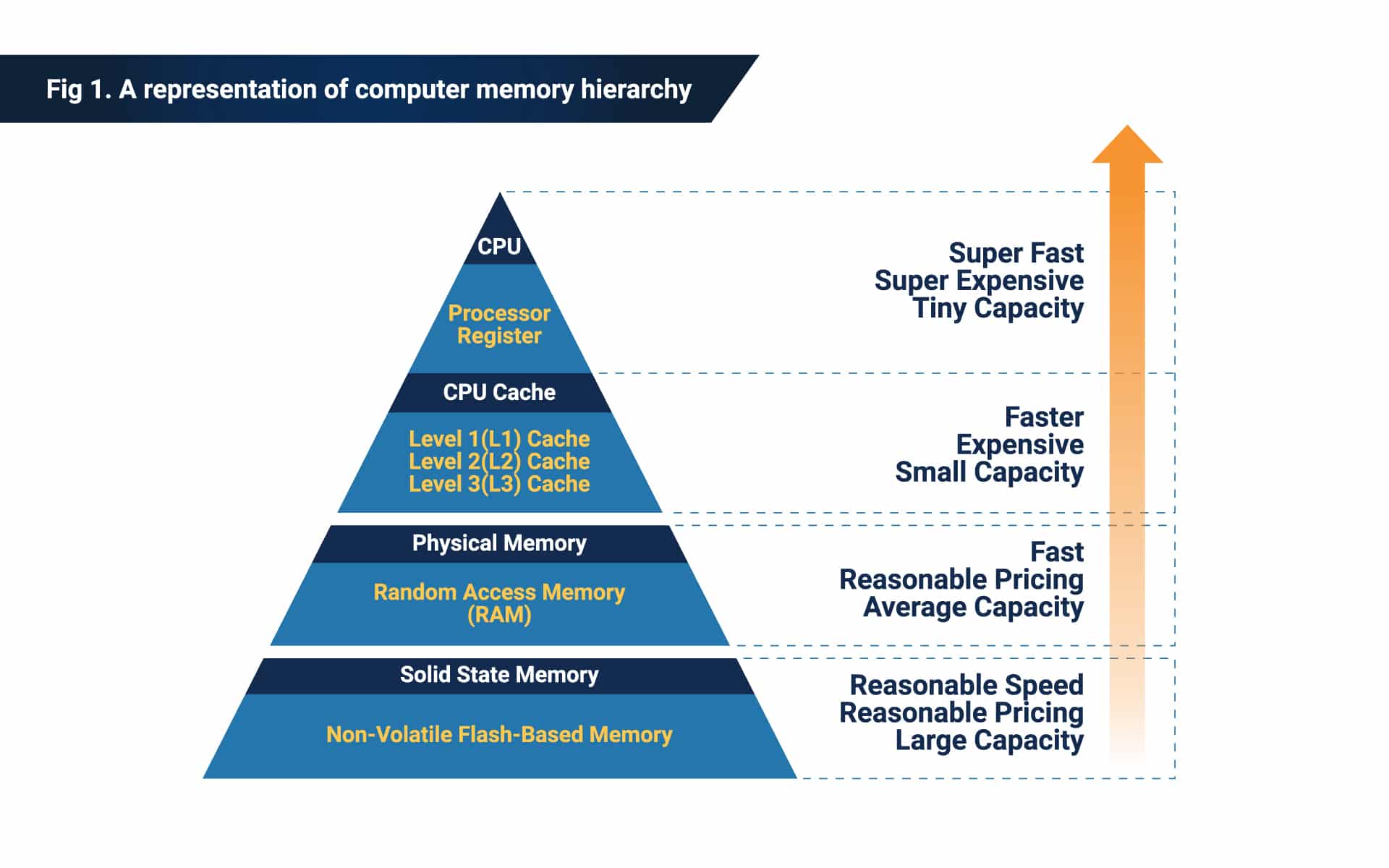

Auf der anderen Seite der Computerseite in einem Computersystem befindet sich die Speicherseite. Jedes Computersystem benötigt eine Art Hardwarespeicher, um die Zwischenparameter oder Berechnungsergebnisse vorübergehend zu speichern. Für KI-Anwendungen ist es entscheidend, dass die zwischen Berechnung und Training generierten temporären Daten schnell abgerufen oder für eine spätere Verwendung beiseite gelegt werden können. Daher erfordern die meisten für KI-Anwendungen entwickelten IC-Chips erstklassige Speicherhardware und eine gute Speicherschnittstelle, die schnelle Entscheidungen trifft und gleichzeitig mit vielen Registern ausgestattet ist, die einzelne Datenbits mit extremer Geschwindigkeit speichern können.

Zusätzlich zur Geschwindigkeit, die für die Verarbeitung und Datenspeicherung erforderlich ist, kann eine gewisse zusätzliche Geschwindigkeit wertvoll sein, da auf KI-Anwendungen ausgerichtete ICs häufig mit sogenannten „Hardwarebeschleunigern“ ausgestattet sind, um sehr anspruchsvolle Arbeitslasten wie Rückschlüsse auf neuronale Netzwerke zu unterstützen. Bei diesen Beschleunigern handelt es sich in der Regel um spezielle Schaltkreise, die an die Hauptprozessoren angeschlossen sind, die häufig mit größeren Aufgaben ausgelastet sind, um parallel bestimmte Berechnungsaufgaben auszuführen. Dieser Entlastungseffekt der Beschleuniger trägt dazu bei, die Gesamtleistung von KI-Anwendungen zu verbessern, indem er die Effizienz des Chips erhöht und gleichzeitig den Energieverbrauch und die Latenz verringert, die durch den Wechsel zwischen Aufgaben innerhalb des Hauptprozessors verursacht werden.

Als weiteres Beispiel betrachten wir anwendungsorientierte 5G-ICs. Der Schwerpunkt dieses IC-Typs liegt hauptsächlich auf der Ermöglichung drahtloser Hochgeschwindigkeitsverbindungen und Datenübertragung. Zu den wichtigsten Funktionsblöcken im Design können eine digitale Basisbandverarbeitungseinheit gehören, die für die Codierung und Decodierung der drahtlosen Signale verantwortlich ist, und ein Hochfrequenz-Frontend (RF), das sich um die Antenne und den analogen Signaltransceiving kümmert, die während der drahtlosen Kommunikation erforderlich sind.

Darüber hinaus unterstützen ICs, die für 5G entwickelt wurden, häufig erweiterte Funktionen wie Beamforming, das drahtlose Signale über die Steuerung mehrerer Antennen an bestimmte Geräte weiterleitet. Um solche Steuermechanismen zu implementieren, muss ein MIMO-Funktionsblock (Multiple-Input, Multiple-Output) in die Schaltung implementiert werden, um die Signalsequenz von mehreren Antennen richtig zu steuern.

Trotz der unterschiedlichen Zielanwendungen erzeugen bestimmte Aspekte und Prozesse, die beim Entwurf eines IC verwendet werden, Korrelationen zwischen scheinbar unterschiedlichen IC-Typen. Beispielsweise benötigen sowohl KI-ICs als auch Flash-Speicher-Controller-ICs effiziente Speicherschnittstellen, um optimale Leistungen zu erzielen. Der Unterschied besteht lediglich darin, wo die zugehörigen Speichergeräte in der Speicherhierarchie eingeordnet sind. In Bezug auf 5G-ICs weist das Design eines robusten MIMO-Signalsystems subtile Ähnlichkeiten mit der Implementierung eines First-In-First-Out-Puffers (FIFO) zur Steuerung des Datenflusses in einem NAND-Flash-Speicher-Frontend auf. Obwohl es keine direkte Verbindung zwischen den beiden Designs gibt, beinhalten beide unterschiedliche Pufferschaltungen, die mit manipulierten Eingängen die gewünschte Ausgabe erzeugen.

IC-Design für Flash-Speicher-Controller in SSDs

Ein generischer SSD-NAND-Flash-Speicher-Controller-IC umfasst spezifische Funktionsblöcke wie:

-

-

- Front-End-Verbindungen

- Ein zentraler Motor

- Eine Puffer- und Speichermedien-Verwaltungseinheit

- Peripherieverbindungen

- Mehrere Verschlüsselungs-Engines für Zuverlässigkeitsgarantie und Sicherheitsfunktionen

-

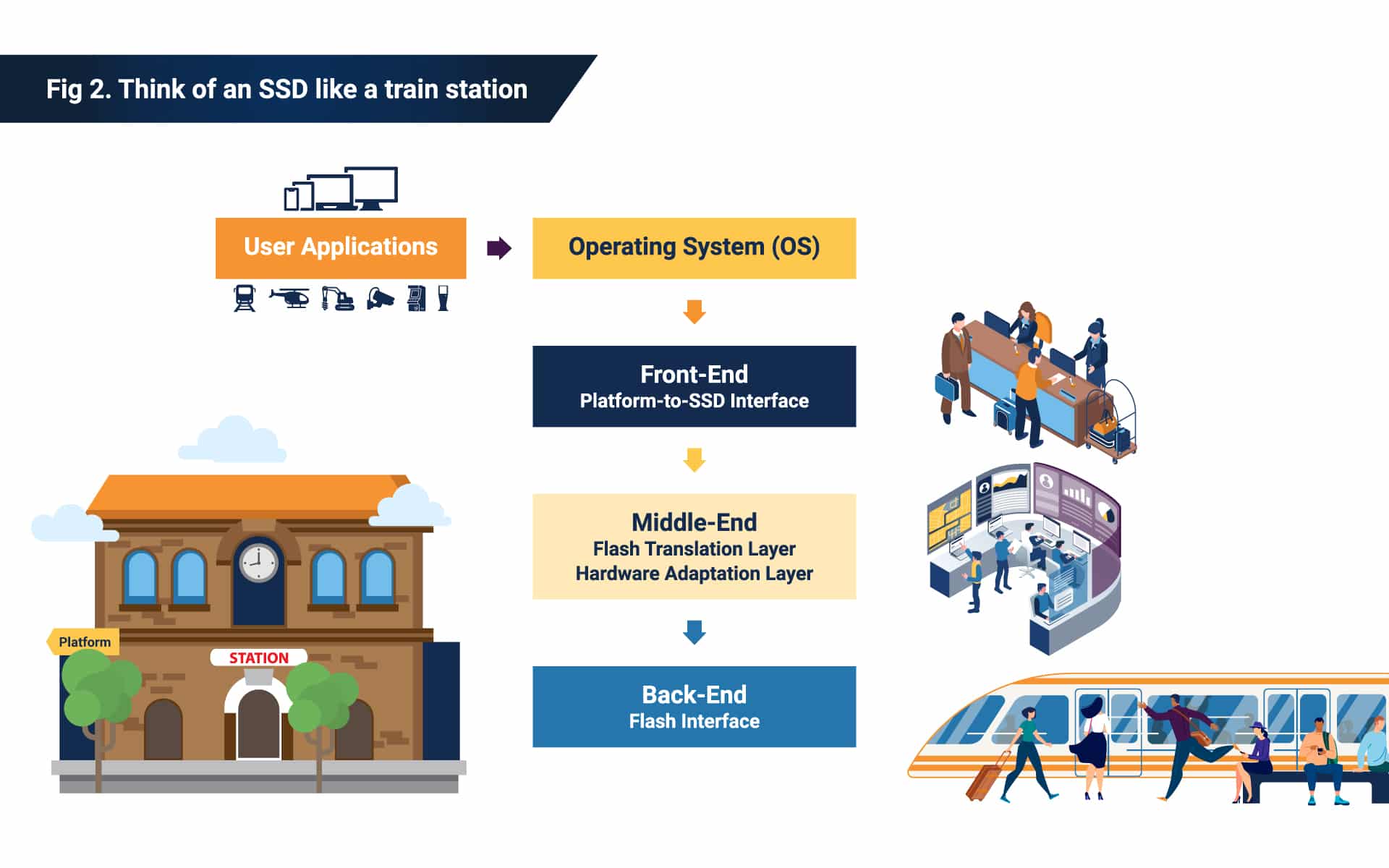

Diese Blöcke arbeiten zusammen, um den effizienten Betrieb der SSD als zuverlässiges Datenspeichergerät sicherzustellen. Um besser zu veranschaulichen, wie das geschieht, verwenden wir die Analogie eines Bahnhofs. So wie ein Bahnhof über verschiedene Bereiche oder Abschnitte für Reisende verfügt, kann auch der Betrieb einer SSD zur Bereitstellung von Daten in mehrere Teile unterteilt werden: das Front-End, das Middle-End und das Back-End.

Das Frontend

Stellen Sie sich das Front-End einer SSD wie die Eingangshalle eines Bahnhofs vor. Ähnlich wie in einer Bahnhofslobby, wo die Dienste Ticketverkauf, Gepäckaufbewahrung oder sogar Hausmeisterdienste umfassen, dient das Front-End einer SSD als Dateneingangspunkt mit vielen Vorverarbeitungsdiensten für eingehende Signale. Zu diesen Diensten gehören der Aufbau einer Signalverbindung über eine gezielte Übertragungsschnittstelle (bei der es sich um SATA, SAS oder PCIe handeln kann), eine protokolltreue digitale Signalübersetzung und verschiedene Routinen zur Verbindungsüberprüfung.

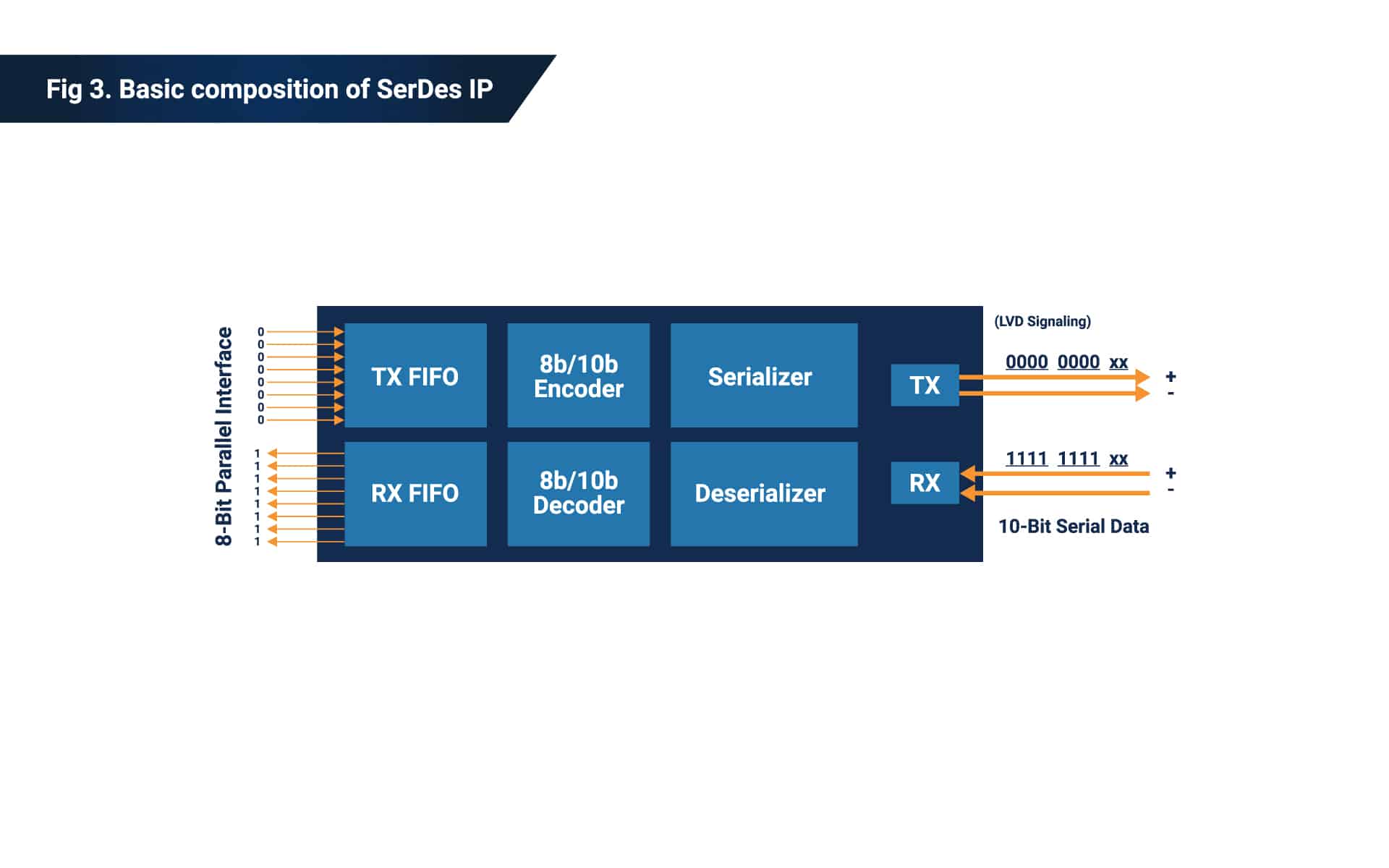

Um diese Dienste bereitzustellen, müssen viele generische und patentierte Miniaturschaltkreise, oft als IPs abgekürzt, auf einen NAND-Flash-Speicher-Controller-IC-Chip gepackt werden. Ein Beispiel für eine Front-End-IP auf Phisons eigenen SSD-Controller-Lösungen ist die SerDes (kurz für Serial-and-Deserializer), der für die Umwandlung eingehender paralleler Datenbits – d. h. sie kommen gleichzeitig über verschiedene physische Pins – in einen seriellen Bitstrom und umgekehrt verantwortlich. Die Zusammensetzung eines SerDes umfasst einen FIFO-Cache für die Datenflussverwaltung sowie ein Paar Codierer für die Protokollkonformität. Phison verfügt über ein eigenes umfassendes SerDes-IP-Portfolio für Mainstream-SSD-Übertragungsschnittstellen, das auf den branchenweit besten Produktionsverfahren im Nanometerbereich basiert, um seine SSD-Frontends vollständig mit Strom zu versorgen.

Das mittlere Ende

Das mittlere Ende ist hauptsächlich für die Cache- und Speichermedienverwaltung verantwortlich. Im Inneren von SSDs befinden sich zwei wichtige Speicherkomponenten: DRAM und NAND-Flash. DRAM dient als Cache-Speicherplatz, in dem temporäre Daten abgelegt werden können, und NAND-Flash ist das Speichermedium, in dem Daten für längere Zeiträume gespeichert werden. Das mittlere Ende ist für eine SSD aufgrund ihrer Funktion als Zentrum des Systems äußerst wichtig. So wie Fahrdienstleiter oder Ansager an Bahnhöfen Passagiere zu temporären Wartebereichen oder Zügen für längere Fahrten leiten, leiten SSD-ICs Daten zur temporären Speicherung an DRAM oder zur längeren Speicherung an NAND-Flash weiter.

Um seine Aufgabe als zentrale Versandstelle erfüllen zu können, müssen ein Flash Translation Layer (FTL) und eine Hardware-Anpassungsschicht implementiert werden, um bei der Datenplatzierung auf den Speichergeräten zusammenzuarbeiten. Der FTL ist dafür verantwortlich, die Daten in seinem Kontobuch dem richtigen physischen Speicherort im Flash-Speicher zuzuordnen. Ebenso wird ein ähnlicher Mechanismus der Tabellenverwaltung und -zuordnung auch für temporäre Daten im DRAM übernommen. Sowohl FTL als auch Hardware-Anpassungsschichten sind wichtige Firmware-Funktionen, die die Gesamtleistung einer SSD erheblich beeinträchtigen können. Sie werden von einer leistungsstarken zentralen Hardware-Engine angetrieben, die im Rahmen des Designs eines Controller-IC sorgfältig geplant werden muss.

Um den Bedarf im Middle-End zu decken, verfügt Phison über viele Hardware-IPs, die einzigartige Möglichkeiten zur Unterstützung des zentralen Dispatchers bieten. Dazu gehören die CoXProcessor™ Und Speicherschnittstellen-IPs Dadurch können die NAND-Flash-Controller-ICs von Phison mit Produkten jeder Generation andere übertreffen.

Das Backend

Im Backend eines NAND-Flash-Speicher-Controller-ICs dreht sich alles um den NAND-Flash-Speicher. Wie bereits erwähnt, sind die NAND-Flash-Speicherchips die Züge in unserer Bahnhofs-Analogie. Der Service im Zug ist für das gesamte Reiseerlebnis ebenso wichtig wie die Hilfe und Wegbeschreibung in den Bahnhöfen. Ein großer Teil des NAND-Flash-Controller-IC-Designs konzentriert sich auf diese In-Train-Dienste, zu denen die Anpassung des NAND-Schnittstellenprotokolls, die Aufrechterhaltung der Lebensdauer und die Fehlerkorrektur gehören.

Die Fähigkeit eines NAND-Flash-Controllers, sich an NAND-Flash-Schnittstellenprotokolle anzupassen, ist wie ein erfahrener Lokführer, der verschiedene Zugmodelle fehlerfrei und effizient bedienen kann. Phison verfügt über ein starkes IP-Portfolio, das mit den neuesten Schnittstellenspezifikationen der gängigen Protokolle ONFI und Toggle kompatibel ist. Mit den gesammelten Hardware- und Firmware-IPs steuern die NAND-Flash-Speicher-Controller-ICs von Phison NAND-Flash mit mühelos gleichmäßiger Geschwindigkeit und Kontrolle.

Wie wir alle auf unseren Reisen erlebt haben, machen wir manchmal Fehler bei der Suche nach unseren Sitzplätzen oder sogar beim Einsteigen in den richtigen Zug – und das gilt auch für Daten in Form von Elektronen im NAND-Flash-Speicher. Aufgrund ihrer inhärenten physikalischen Eigenschaften können gelegentlich Elektronen aus NAND-Flash-Zellen austreten, was während des Betriebs und im Laufe der Zeit zu Datenbitfehlern führen kann. Daher ist die Aufrechterhaltung einer hohen Lebensdauer und Zuverlässigkeit des NAND-Flash eine weitere entscheidende Voraussetzung für ein gutes Back-End-Design des NAND-Flash-Speicher-Controller-ICs.

Wählen Sie Phison-ICs für hohe Zuverlässigkeit und Qualität

Phison wählt die hochwertigsten NAND-Flash-Lösungen auf dem Markt aus, um die beste inhärente Lebensdauer seiner High-End-SSD-Produkte zu garantieren – und das Unternehmen hat sein Qualitätsvermächtnis mit einem starken Portfolio an fortschrittlichen Produkten gestärkt Fehlerkorrekturcode (ECC). Ähnlich wie ein professioneller und hilfsbereiter Servicemitarbeiter im Zug Fahrgäste unterstützt, bewältigt Phisons fortschrittliches ECC diese entkommenen Elektronen und NAND-Flash-Bitfehler mit Leichtigkeit, basierend auf Generationen ständig verbesserter Firmware-Algorithmen und Hardware-Engines für spezielle mathematische Berechnungen.