过去十年来,PCIe 一直是连接计算机主板上高速外围硬件组件的标准接口,这已不是什么新闻了。自最早发布以来,该标准每3到4年就会经历一次稳定的传输速率升级和换代,但PCIe 4.0于2017年到来,引发了人们对技术创新的关注和热情。从数据存储的角度来看,“Gen 4”接口释放了基于 PCIe 3.0 标准构建的 NVMe 固态硬盘 (SSD) 约 3 GB/s 的长期带宽上限。接口升级鼓励许多供应商推动更好的设计,以适应第四代接口并解决处理器层和存储层硬件解决方案之间的瓶颈。

PCIe 接口和 Gen 4 基础知识

从外围组件的角度来看,PCIe接口就是我们所看到的组件模块开发过程中的“前端”。良好的“前端”设计的最终目标是通过目标接口确保硬件模块和计算机系统之间的稳健连接。

您可以将设计和开发过程分为两个阶段:硬件和固件。虽然人们很容易质疑自 2000 年代初以来 PCIe“前端”设计工作中的创新,但硬件和固件改进工作中的细节使得成熟的设计随着每个接口规范的发布而脱颖而出。

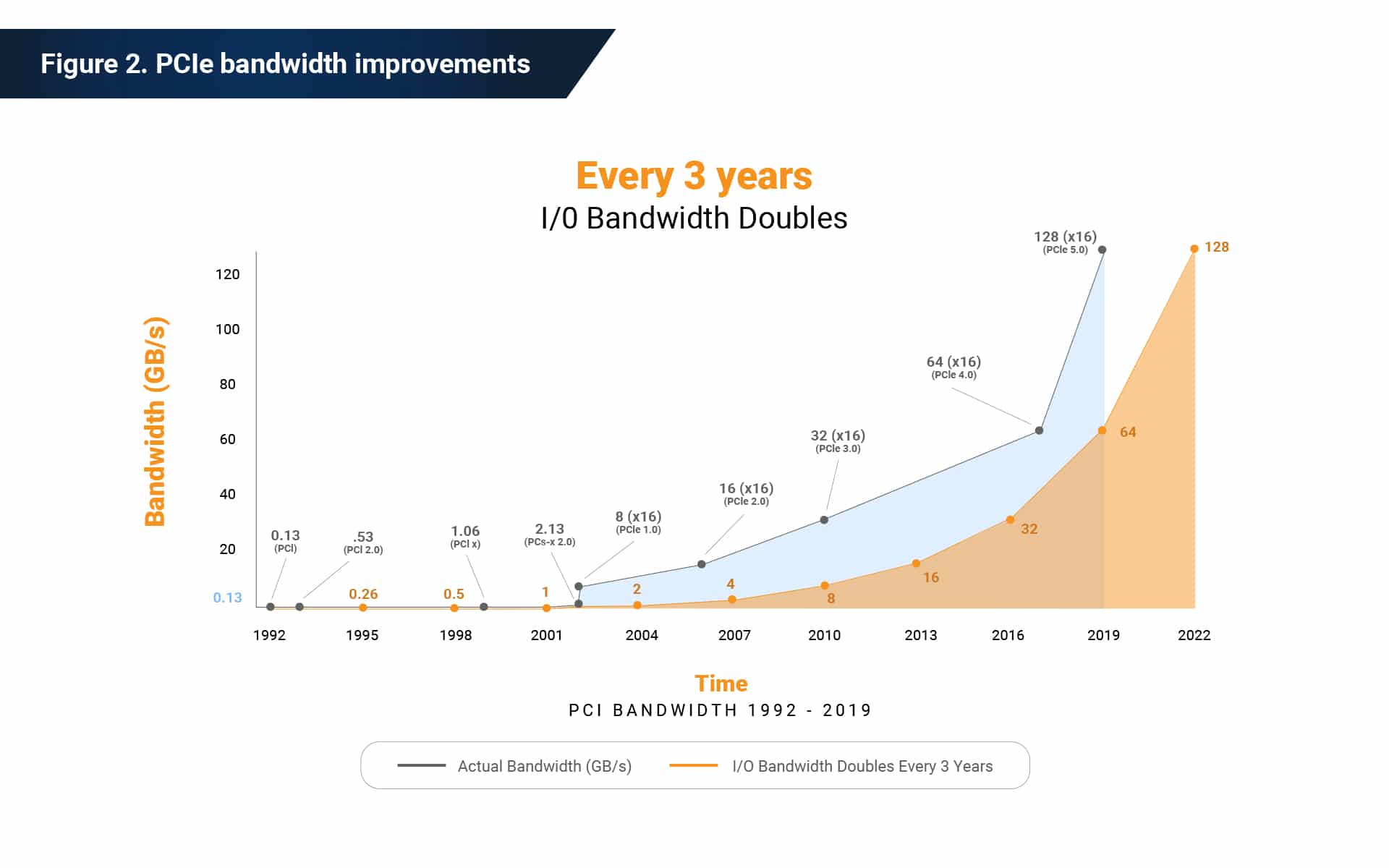

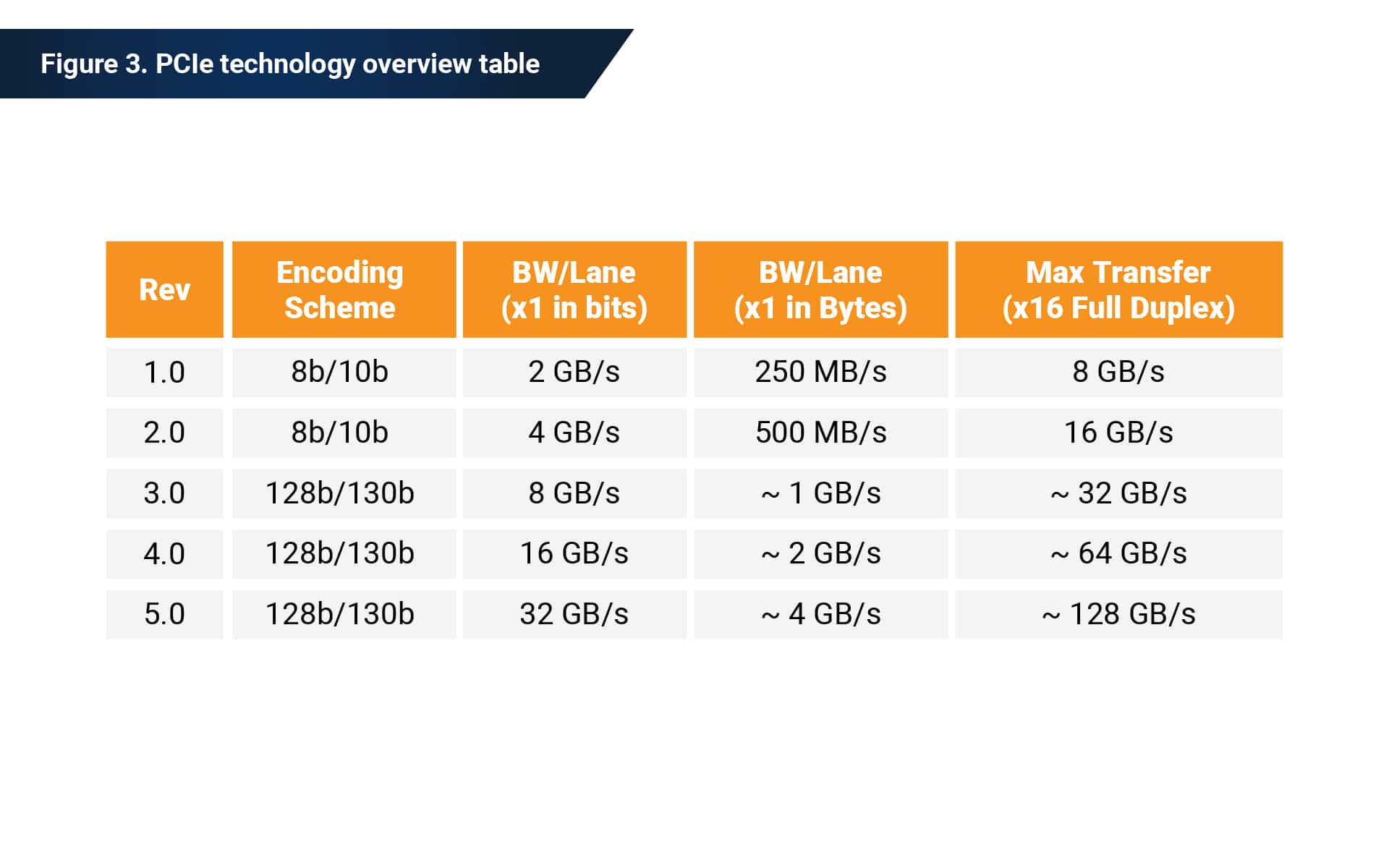

要了解“前端”设计主机,必须首先回顾一下PCIe接口硬件配置基础知识。对于通过 PCIe 连接到主板的存储组件,它采用通常称为 x1、x4、x8 和 x16 插槽配置的硬件连接器之一。例如,Gen 4×4 配置表明连接器遵循 PCIe 基本规范修订版 4.0 的必要设计和特性要求,同时通过 4 个 PCIe“通道”发送数据信号。每条通道都是双向路径,在一秒钟内“闪烁”数十亿个电信号。第 4 代 PCIe 通道以每秒 16 千兆传输 (GT/s) 的速度执行信号传输。虽然通过释放高/低电压的电信号来表示逻辑1和0,传输节点和接收节点之间可以交换一个“比特”的数据,但16GT/s表示在一秒内执行160亿次。

此外,PCIe通道在“全双工”机制下运行。即,两个方向上的数据传输可以同时发生。因此,16 GT/s 的传输速率理论上表明,在第四代连接器上运行的功能强大的 PCIe 组件可以在其 32 个可用通道之一内在一秒内交换 320 亿个数据位。

然而,计算中的问题是 PCIe 与许多其他数据传输硬件接口一样,通过将时钟信息编码到数据流中来保护其数据。从 PCIe Gen 3 开始,采用 128 位至 130 位编码方案进行数据保护。该方案需要在每 130 位传输中使用 2 位来存储时钟信息,以帮助识别和验证链路接收侧的数据。通过简单的除法和乘法,16GT/s 变成每秒 157.54 亿位的传输速率,通常称为 15.754 Gb/s 的有意义数据位传输(忽略时钟信息位)。

计算时钟信息位可得出 16 Gb/s 的物理带宽。然后,它可以以 8 位到 1“字节”的速率转换为 4 GB/秒 (GB/s),这是模块级带宽和吞吐量领域中更常用的标准数据大小单位。此外,PCIe Gen 4 指令下的总带宽可扩展至 64 GB/s,是上一代 PCIe 3.0 最大吞吐量的两倍。

从这一进步的意义来看,计算机上输入的字符的数据大小为 1 字节(或 8 位),而 PCIe Gen 4×16 接口可以在一个字节内交换一对 320 亿字符的文件。第二。一部 1080p 高清电影通常会堆积一个大约 10 GB 的文件,而 64 GB/s 的带宽允许您将其中的三个文件从存储复制到计算机,同时在理想的数据处理环境下在一秒钟内将三个文件全部移出。尽管如此,PCIe闪存存储瓶颈仍然远低于16通道的满容量。 2021年主流NVMe SSD主要采用x4配置,物理性能上限为8GB/s。

PCIe 规范概述

当前最广泛采用的存储接口不仅仅是性能指标。 PCIe协议监管的电信号监管了深入的功能和能力,包括但不限于:

-

-

- 接口初始化,

- 维护状态跟踪,

- 互连电源管理,

- 车道测绘谈判,

- 接口级数据编码/解码,

- 以及嵌入式时钟调谐

-

除了物理层之外,还有另外两个 PCIe 规范,它们对于正确的 SSD 前端操作同样重要,甚至更重要。 “数据链路层”(或简称“链路层”)和“事务层”。正如“物理”一词所表明的那样,该层内的许多功能在很大程度上取决于存储模块的硬件设计。另一方面,理解上面两层有助于了解前端相关的固件模块。

紧接物理层之上的是数据链路层,负责与物理层配合,确保系统间信息交换的可靠。请注意“信息”而不是“数据”的措辞,因为该层内的工程重点已从数据信令中的物理视图转移到逻辑以及物理连接和链接的固件视图。它与物理层的协作包括往返于物理层的电源状态传输、链路级数据保护以及错误重试/记录服务。

最后但并非最不重要的 PCIe 设计层是事务层,它对称为事务层包 (TLP) 的数据包的移动进行操作。随着 TLP 的生成和接收,事务层与 PCIe 链路的另一侧交换流控制信息。更具体地说,它存储由系统/存储处理器生成的链路配置信息以及由物理层硬件生成的链路能力。此外,TLP的处理也是软件和硬件启动的电源管理机制的主要基础。了解上面两层有助于了解前端相关的固件模块。

总而言之,事务层承担着链路处理和电源管理的重任,需要同步的硬件和固件工作。

PCIe Gen 4 市场概览

随着PCIe架构分层设计模型的不断完善,该规范制定了可扩展、可扩展的数据传输接口,并将继续发展超越当前的措施。尽管随着第 5 代存储控制器解决方案已于 2021 年进入市场(以及新兴的第 6 代讨论),下一代 PCIe 的技术进步即将到来,但市场采用率仍会日复一日地立即为行业级存储收入做出贡献。

尽管 PCI-SIG 工作组已经将目光投向了第 4 代以外的领域,这已不是什么秘密,但主流固态存储市场仍处于第 4 代采用的鼎盛时期。从消费市场入手,AMD 在 2019 年 Computex 上率先推出搭载 X570 芯片组的 PCIe Gen 4 平台,奠定了第一家系统厂商的地位。同年,群联率先推出全球首款 PCIe Gen 4 闪存控制器,并搭载 X570 芯片组。我们的 E16 解决方案将第三代性能抛诸脑后,以 5 GB/s 的吞吐量传输数据。

另一方面,英特尔宣布推出代号为 Rocket Lake 的新平台,该平台的发布时间可能较晚,但在支持 PCIe 外设的性能方面却有所落后。从Intel官方公布的基准测试结果来看,PCIe Gen 4 SSD结合Rocket Lake平台,在2020年将Gen 4性能提升到了一个新的水平。

响应这一突破,群联于同年晚些时候推出了更新的 E18 PCIe Gen 4 控制器解决方案,将 Gen 4 记录推向了巅峰。它成为世界上第一个吞吐量超过 7 GB/s 的控制器解决方案。凭借与两家世界级CPU/平台供应商的持续牢固合作关系,群联将随时准备引领PCIe消费市场,并通过跨越台式机、笔记本电脑、游戏和工作站市场的尖端存储解决方案为其合作伙伴和客户提供支持。

另一方面,机器学习、人工智能(AI)和深度学习等企业级和数据中心级高性能计算应用的持续增长,刺激服务器市场追求更强大的计算能力。需要具有可靠的一致性和可靠性的高性能存储来确保稳定的服务质量,这是过渡到 PCIe Gen 4 存储解决方案以满足带宽要求的绝佳机会。除了吞吐量需求之外,大多数企业和数据中心级用例都遵循严格的标准,这些标准可以调节稳定的性能,并且对压力下超出规格的延迟的容忍度较低。

为了满足这一需求,需要强大的硬件和固件设计能力来针对客户应用进行微调,以实现 PCIe Gen 4 的无缝过渡。作为Gen 4解决方案市场的开拓者,群联的工程团队一直在苦心准备深入云和高性能计算市场转型,并通过释放前端瓶颈来追求更高水平的存储服务。

群联在第四代应用领域取得了公认的成就,并为消费市场快速、及时地提供了第四代SSD解决方案。我们将投入同样的注意力和工程资源来支持企业市场应用的第 4 代和第 5 代过渡。