2013年,苹果推出了第一款配备PCIe SSD的MacBook Pro,正式将基于PCIe的SSD领域扩展到消费类应用。然而,基于 PCIe 的 SSD 因其高带宽和可扩展性而在此之前就已广泛应用于服务器和数据中心。

凭借最新的 3D NAND 闪存技术,PCIe SSD 变得更加便宜,从而在零售和消费应用中得到更多采用。但价格和性能并不是消费者和企业转向 SSD 的唯一原因。数据保护也是一个重要因素。

SSD端到端数据保护

借助 3D TLC 或 QLC 等先进闪存工艺技术,驱动器可以以极具吸引力的零售价格轻松存储 TB 级数据。但 PCIe SSD 控制器如何保护数据对于驱动性能同样重要,因为存储的数据量增加了一倍甚至三倍。

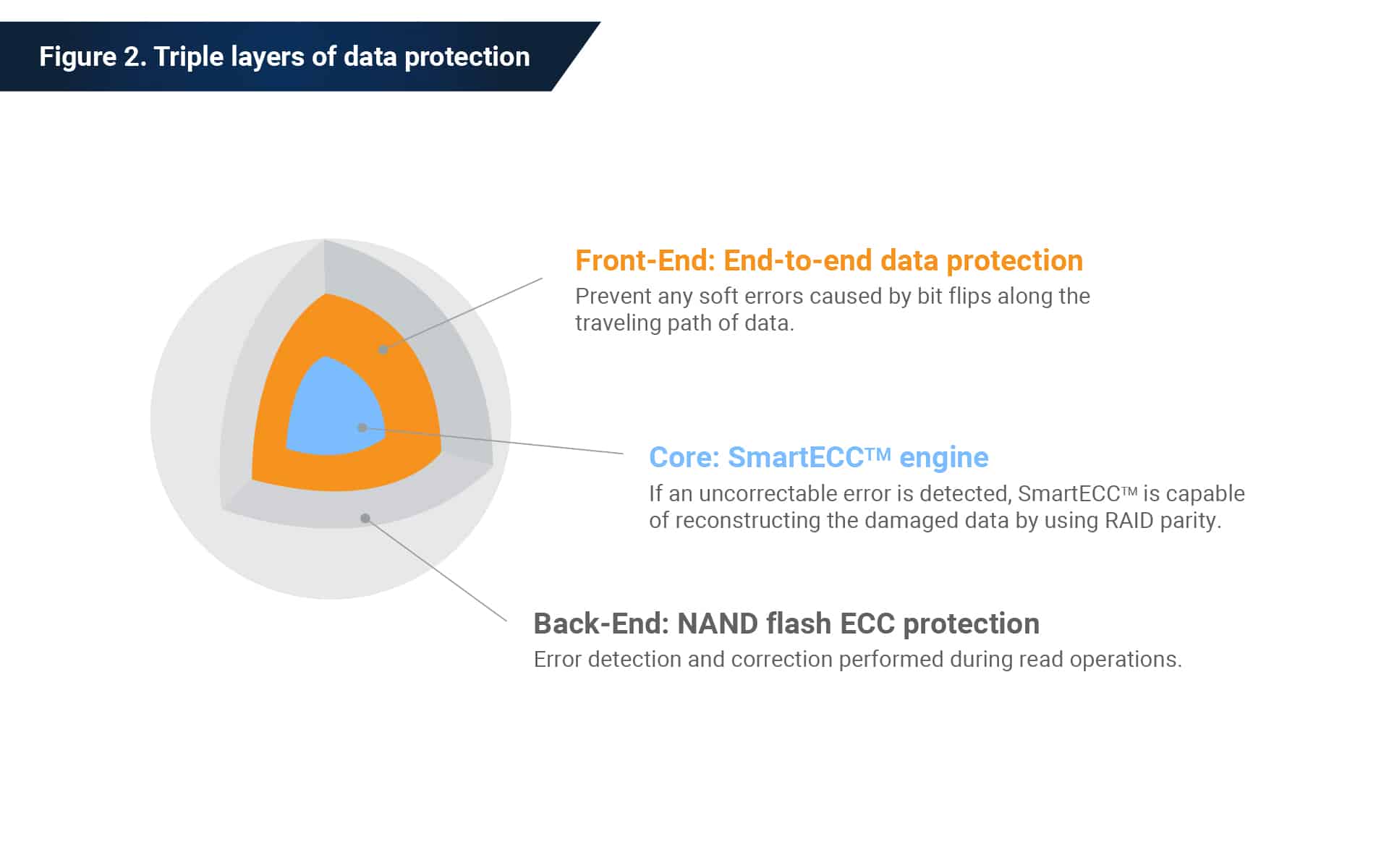

为了 群联 PCIe SSD,数据保护分为三个级别:

-

-

- 前端:端到端数据保护 (ETEDP) 可保护读取和写入操作中的数据。

- 核:SmartECCTM引擎使用RAID机制恢复错误数据。

- 后端:NAND 闪存 ECC 保护在读取操作期间执行错误检测和纠正。

-

端到端数据保护,也称为 ETEDP,旨在检测数据传输时的任何软错误。当从 NAND 闪存读取数据或向 NAND 闪存写入数据时,在数据传输过程中存在多个临时存储数据的步骤。因此,闪存存储可能存在位翻转或噪声,从而可能导致单事件错误。控制人员需要知道这些错误何时发生,并在可能的情况下采取行动。

写操作保护

当数据写入 NAND 时,它从主机 IP(PCIe 和 NVMe IP)移动到数据缓冲区(DRAM 和 SRAM)、闪存 IP,最后移动到 NAND 闪存。

当主机发出写命令时,数据首先移动到主机IP。根据 CRC 检查数据,如果匹配,则将 E2E 奇偶校验(基于数据的逻辑块地址 (LBA) 生成)附加到数据本身。当数据移动到数据缓冲区时,该数据受到 SECDED(单错误纠正,双错误检测)的保护,内部的 ECC 引擎可以恢复错误的数据。对于闪存 IP,数据会被检查并附加 CRC 和 LDPC 代码。最后,所有带有奇偶校验的数据被一次性写入 NAND 闪存。

读操作保护

当主机读取数据时,数据从 NAND 移动,然后移动到 Flash IP,然后移动到数据缓冲区,最后移动到主机 IP。

纠错引擎的设计决定了可以恢复多少错误。在读取操作期间,首先检查数据在Flash IP中的LDPC和CRC。如果数据正确,则 ECC 奇偶校验被分离,并且数据相应地移动到其他 IP。与写入操作类似,在数据缓冲区和主机 IP 处检查数据的正确性。如果数据正确,则分离E2E奇偶校验,并将数据发送到主机。

群联科技保障您的数据安全

借助 3D NAND 工艺技术,客户寻求 SSD 的高性能和容量以及更好的耐用性和数据可靠性。在数据保护方面,有不同的方法可以达到目的,但端到端数据保护通常在 PCIe 控制器内实现。端到端数据保护的目的是生成奇偶校验并将其附加到数据中,以便在读写操作的数据传输期间进行软错误检测。