The SSD has been gradually maturing in the storage world, and users have begun replacing HDDs with SSDs because of their higher performance, lower weight, smaller dimensions, and lower power consumption.

In NB (notebook) applications, power consumption, performance, and dimensions are the critical pointers for users when choosing a product. This is especially true for power efficiency since an SSD’s power consumption can determine how long an NB user can work without reaching for a power cable. For this reason, ASPM (Active State Power Management) and APST (Autonomous Power State Transition) of PCIe are crucial to achieving efficient power management.

What is Active State Power Management (ASPM)?

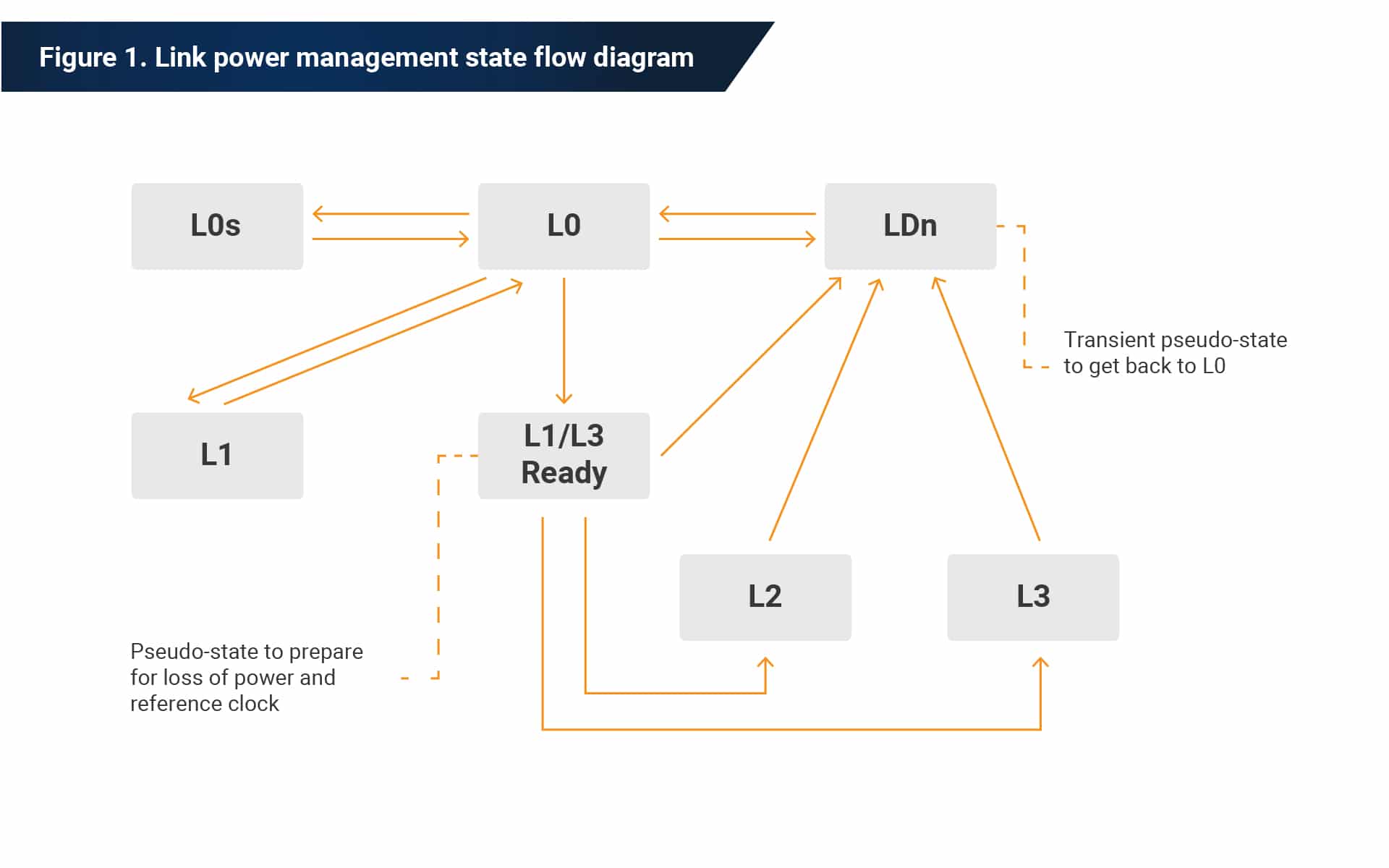

ASPM is a power management protocol used to manage PCIe links when links become less active. The PCIe specification allows PCIe links to go into low power states without involving the system driver. It is typically used on notebooks and other mobile devices to extend battery life. ASPM uses five power link states.

-

-

- L0 – Active state: All PCIe transactions and operations are enabled.

- L0s – A low resume latency, energy-saving standby state: All main power supplies, component reference clocks, and component’s internal PLLs must be active at all times during L0s. The physical layer provides a mechanism for quick transitions from this state to the L0 state.

- L1 – Higher latency, lower power standby state: All main power supplies must remain active during A component’s internal PLLs may be shut off during L1. Enabling more significant power savings with L1 comes with increasing exit latency as a trade-off.

- L2 – Auxiliary-powered link, deep-energy-saving state: In L2, the component’s main power supply inputs and reference clock inputs are shut off. TLP (Transaction Layer Packets) and DLLP (Data Link Layer Packets) transmission are disabled for a link in L2.

- L3 – Link off state: When no power is present, the component is in the L3 state.

-

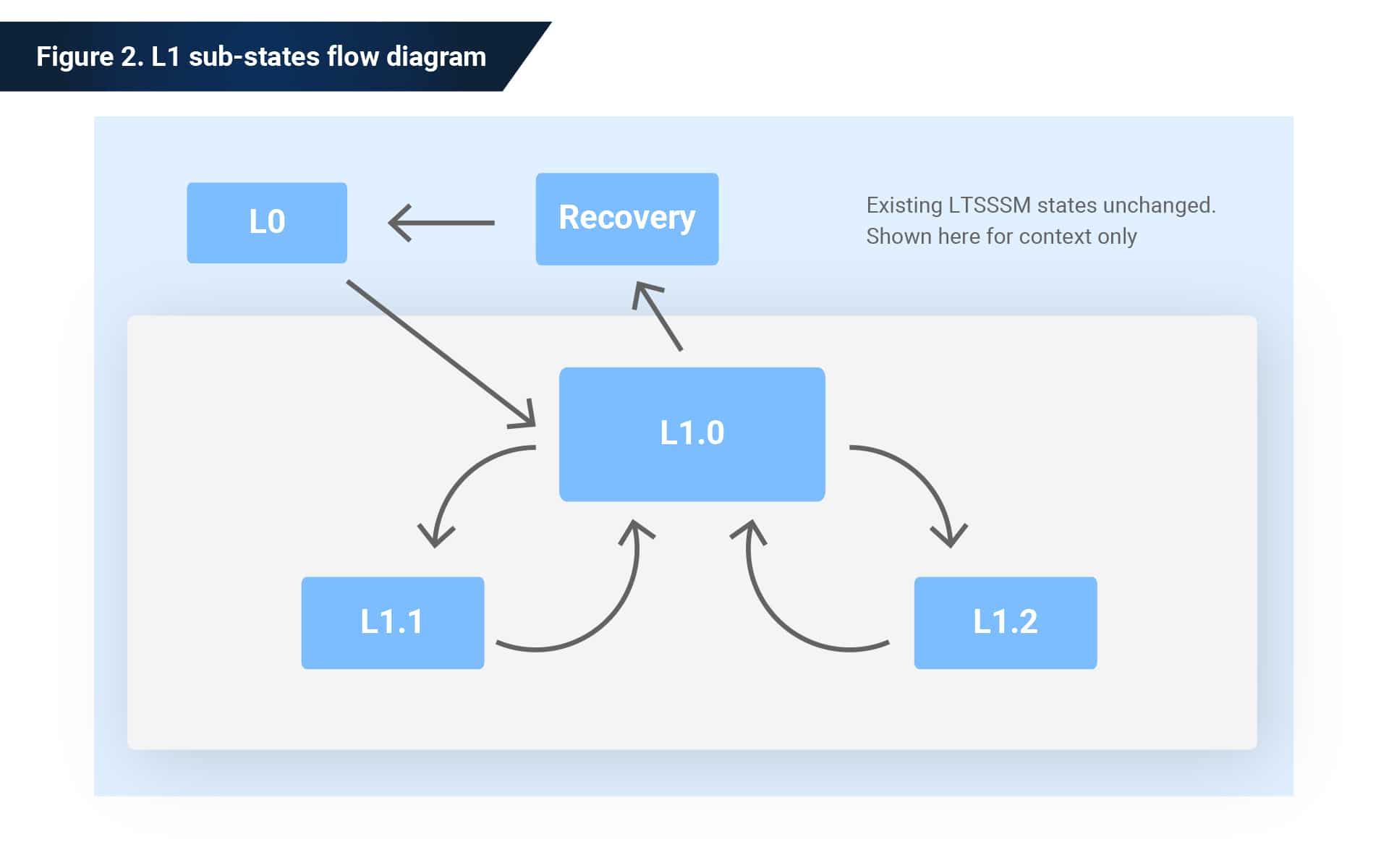

The power savings achieved by L1 are too low to reach SSD power consumption goals, and the resume latencies of L2 are too high to allow for frequent and rapid state switching. L1 sub-states were added to the PCIe specification to address these limitations. L1.1 and L1.2 allow PCIe transceivers to turn off their PLLs, receivers, and transmitters. In addition, L1.2 allows a common mode keeper circuit also to be turned off.

What is an Autonomous Power State Transition (APST)?

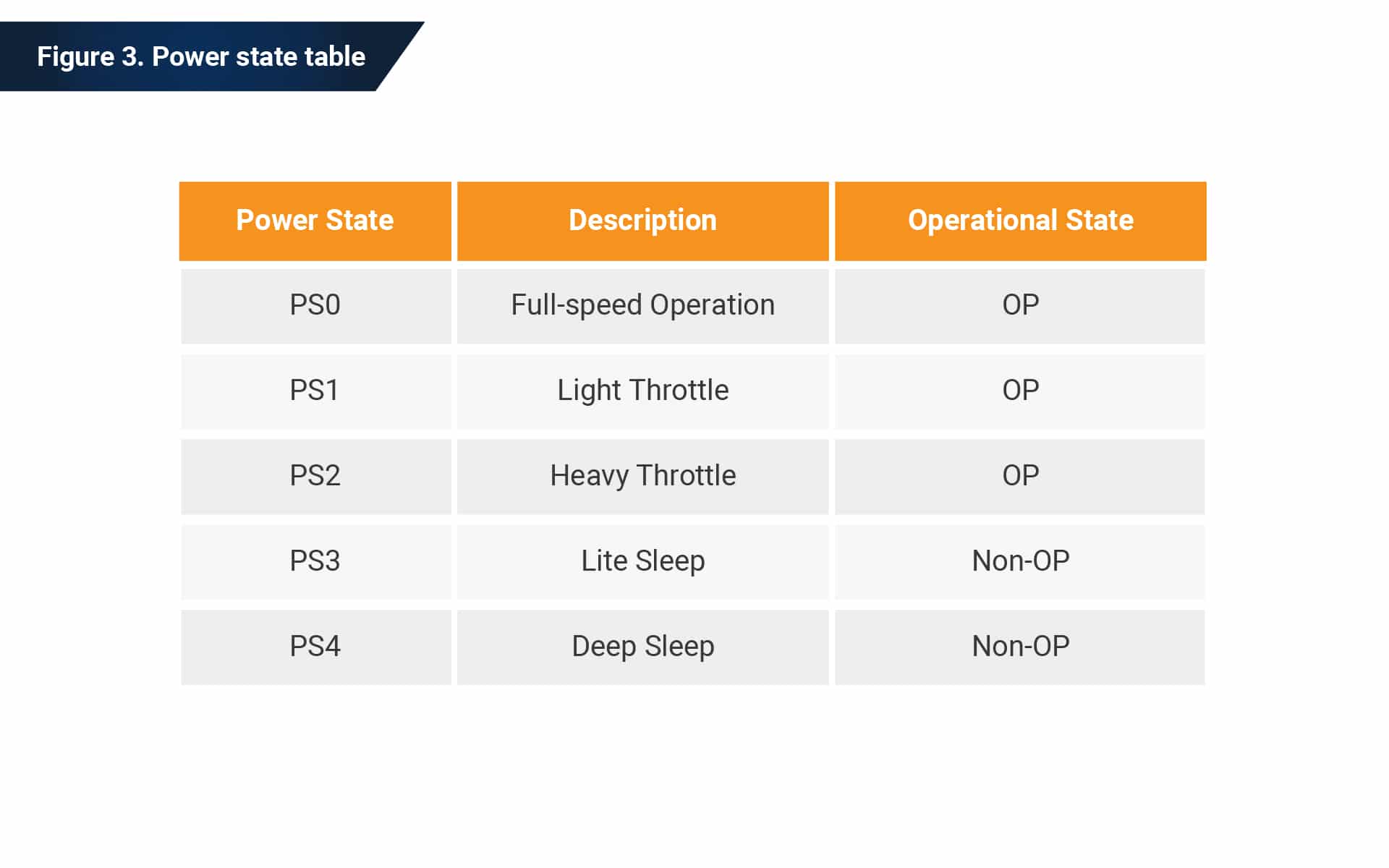

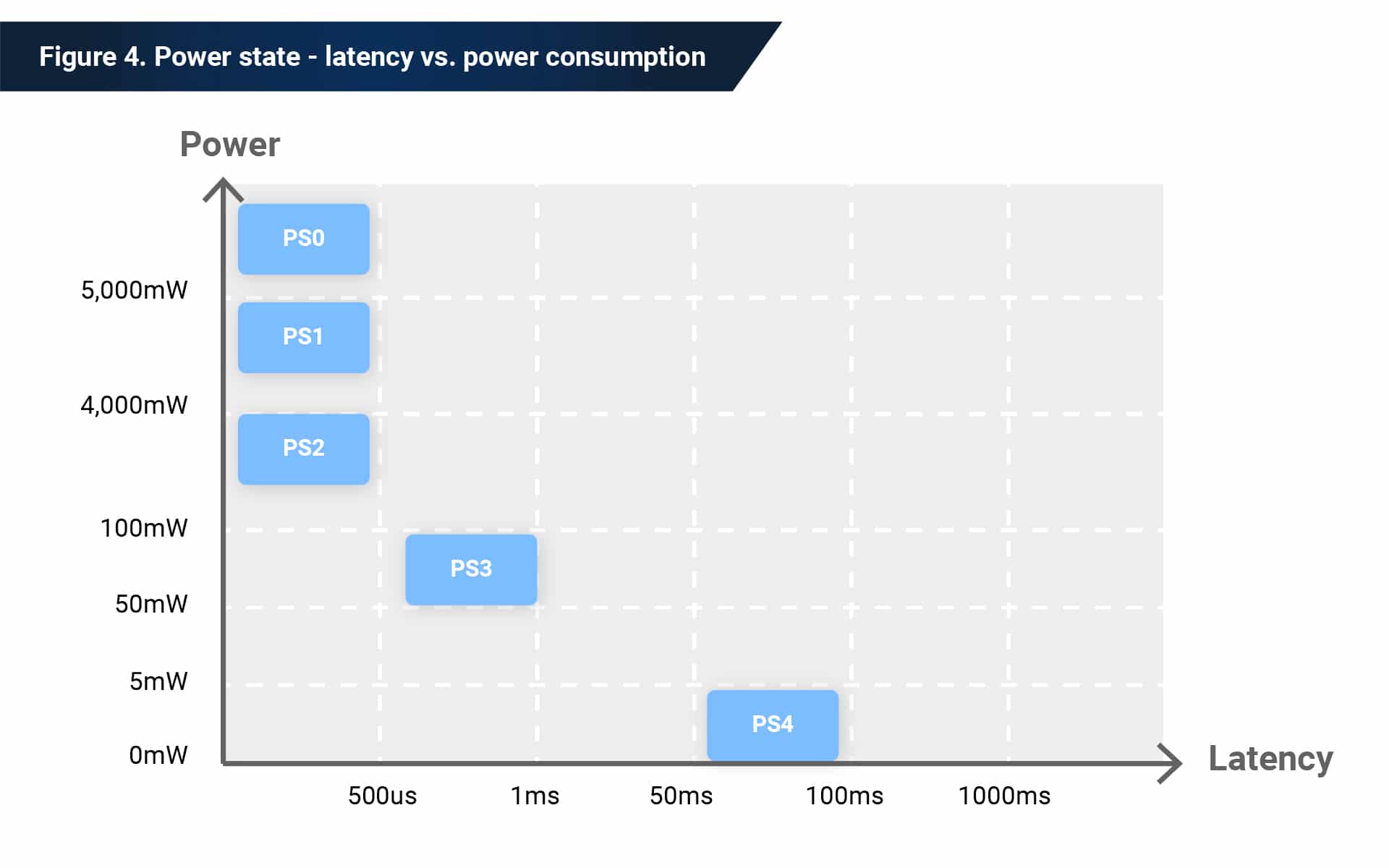

APST allows a host to configure the controller to automatically transition between power states without software intervention when specific conditions are met. For example, the transition power state is triggered when a controller is idle for a particular time. Furthermore, a non-operational power state can automatically transition to another non-operational power state. A firmware developer can define the number of power states. The Phison PS5012-E12, for example, has five defined power states.

The deeper the power state controller entered, the less power consumption and longer exit latency.

Summary

As more and more SSDs are being used in notebooks and mobile devices, more efficient power consumption is crucial for users. ASPM and APST are the essential tools used to manage device power consumption. Phison’s SSDs are designed to efficiently manage power consumption and extend battery life, making them the best SSD choice in the market.