SSD はストレージの世界で徐々に成熟しており、高性能、軽量、小型、消費電力が低いため、ユーザーは HDD を SSD に置き換え始めています。

で NB(ノート)アプリケーション、消費電力、パフォーマンス、寸法は、ユーザーが製品を選択する際の重要な指標です。これは特に電力効率に当てはまります。SSD の消費電力によって、NB ユーザーが電源ケーブルに手を伸ばさずにどれだけ長く作業できるかが決まるからです。このため、効率的な電源管理を実現するには、PCIe の ASPM (Active State Power Management) と APST (Autonomous Power State Transition) が重要です。

アクティブ ステート パワー マネジメント (ASPM) とは何ですか?

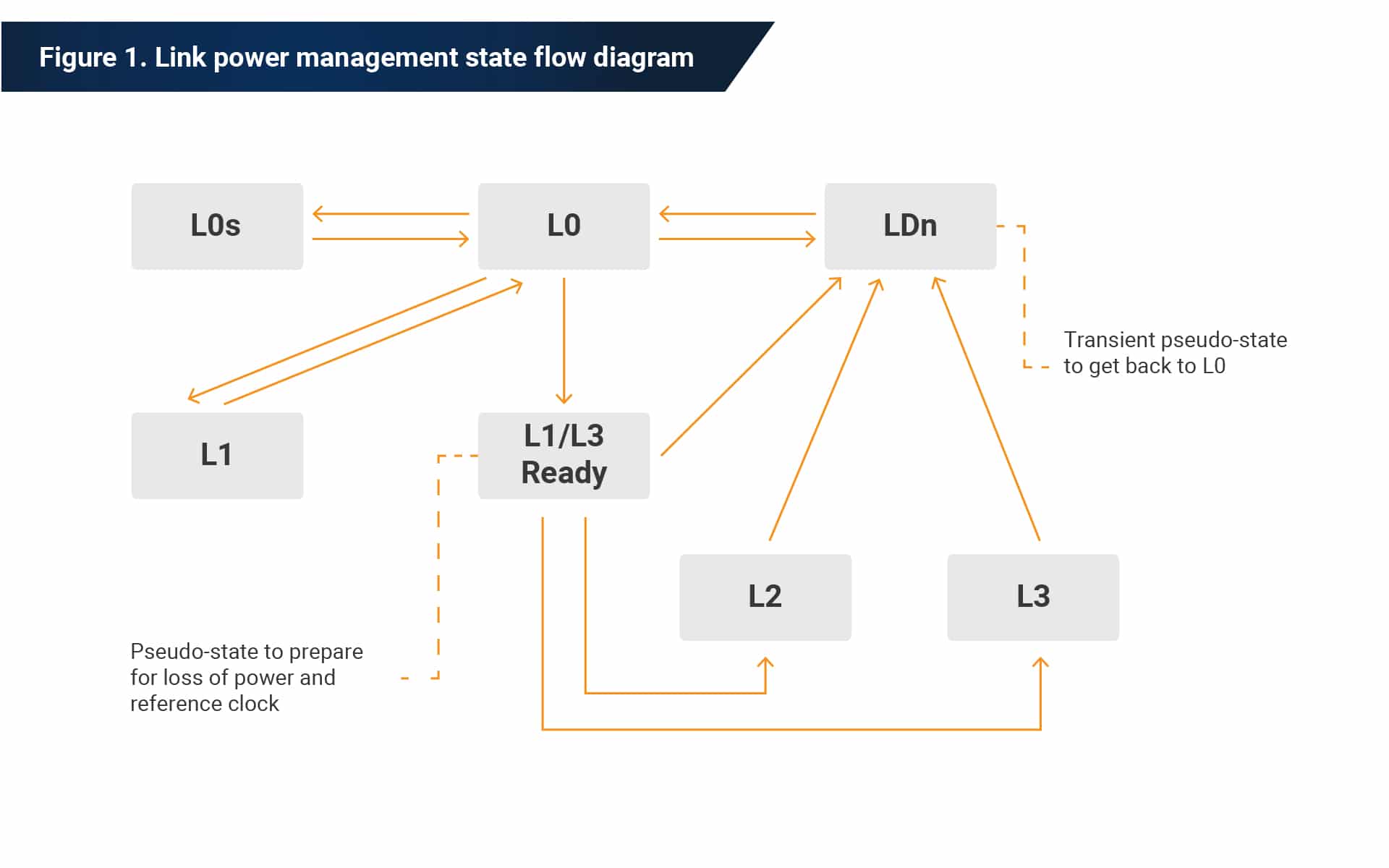

ASPM は、リンクがアクティブでなくなったときに PCIe リンクを管理するために使用される電源管理プロトコルです。 PCIe 仕様では、システム ドライバーを介さずに PCIe リンクを低電力状態にすることができます。通常、バッテリ寿命を延ばすためにノートブックやその他のモバイル デバイスで使用されます。 ASPM は 5 つの電源リンク状態を使用します。

-

-

- L0 – アクティブ状態: すべての PCIe トランザクションと操作が有効になります。

- L0s – 短い再開レイテンシー、省エネスタンバイ状態: すべての主電源、コンポーネントの基準クロック、およびコンポーネントの内部 PLL は、L0s の間常にアクティブである必要があります。物理層は、この状態から L0 状態に迅速に移行するためのメカニズムを提供します。

- L1 – レイテンシが高く、電力が低いスタンバイ状態: L1 の間、コンポーネントの内部 PLL がシャットオフされる可能性がある間、すべての主電源はアクティブのままである必要があります。 L1 でさらに大幅な省電力を実現するには、トレードオフとして終了レイテンシの増加が伴います。

- L2 – 補助電源リンク、高度省エネ状態: L2 では、コンポーネントの主電源入力と基準クロック入力が遮断されます。 L2 のリンクでは、TLP (トランザクション層パケット) および DLLP (データリンク層パケット) 送信が無効になります。

- L3 – リンクオフ状態: 電力が存在しない場合、コンポーネントは L3 状態になります。

-

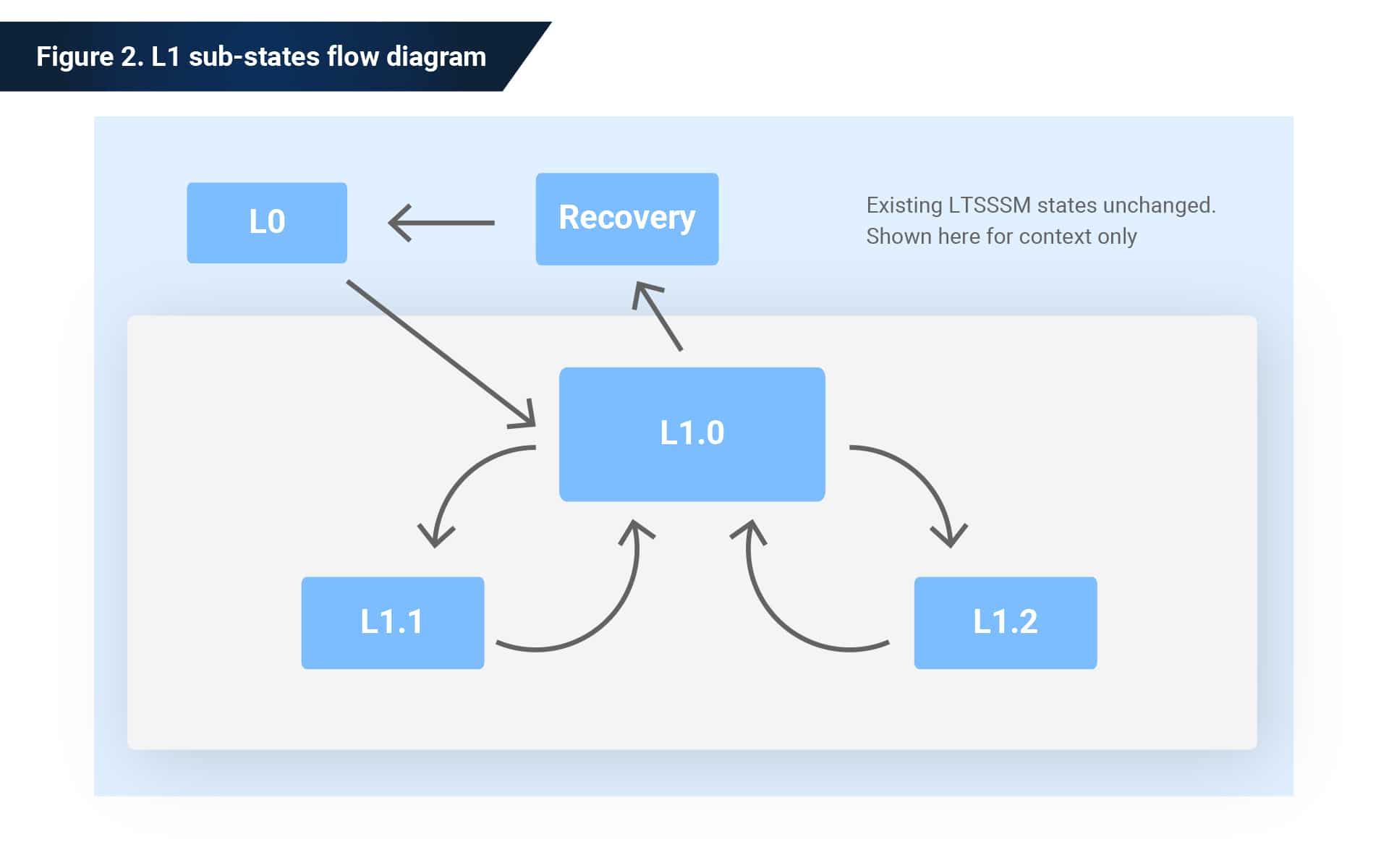

L1 によって達成される省電力は、SSD の消費電力目標を達成するには低すぎます。また、L2 の再開レイテンシは高すぎて、頻繁かつ迅速な状態切り替えを行うことはできません。これらの制限に対処するために、L1 サブステートが PCIe 仕様に追加されました。 L1.1 および L1.2 により、PCIe トランシーバーは PLL、レシーバー、およびトランスミッターをオフにすることができます。さらに、L1.2 により、コモンモードキーパー回路もオフにすることができます。

自律電源状態遷移 (APST) とは何ですか?

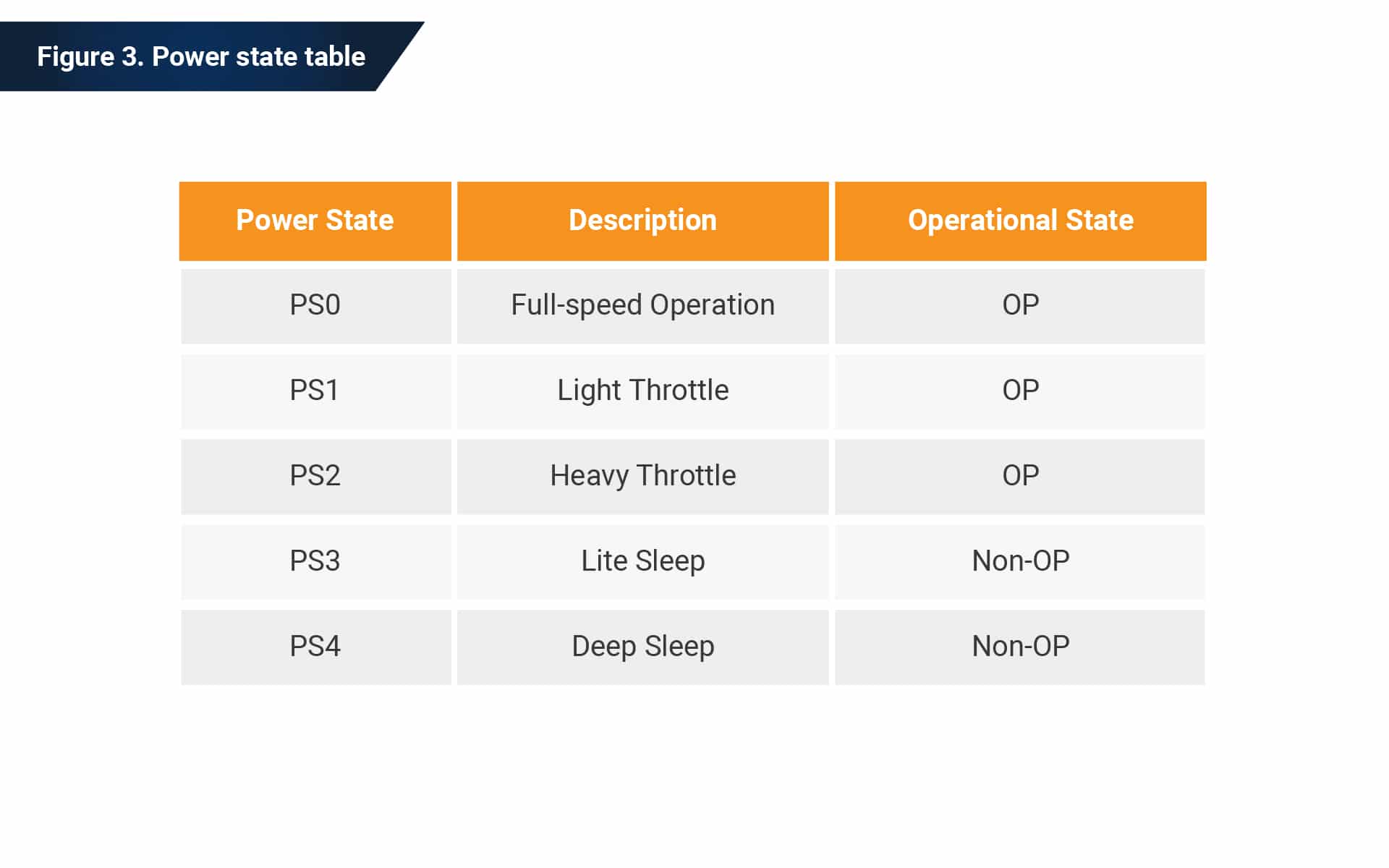

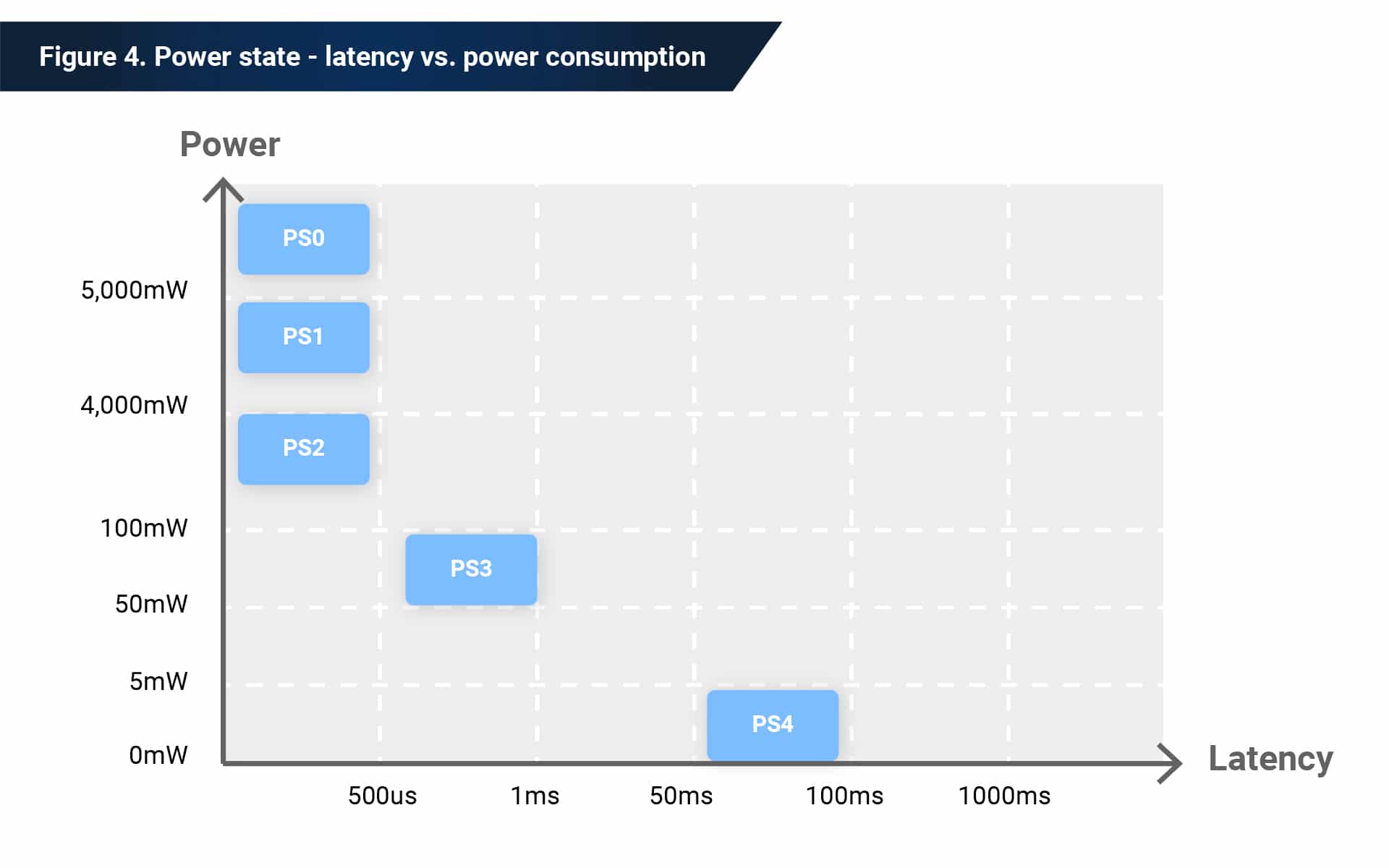

APST を使用すると、ホストは、特定の条件が満たされたときにソフトウェアの介入なしで電源状態間を自動的に移行するようにコントローラーを構成できます。たとえば、移行電力状態は、コントローラーが特定の時間アイドル状態になるとトリガーされます。さらに、非動作電力状態は、別の非動作電力状態に自動的に移行できます。ファームウェア開発者は、電源状態の数を定義できます。フィソン PS5012-E12たとえば、 には 5 つの電源状態が定義されています。

電力状態コントローラーが深く入るほど、消費電力は少なくなり、終了レイテンシーは長くなります。

まとめ

ノートブックやモバイル デバイスで SSD が使用されることが増えているため、ユーザーにとって電力消費効率の向上が重要になっています。 ASPM と APST は、デバイスの電力消費を管理するために使用される重要なツールです。 Phison の SSD 電力消費を効率的に管理し、バッテリー寿命を延ばすように設計されており、市場で最良の SSD の選択肢となっています。