ストレージ市場においてソリッド ステート ドライブ (SSD) が果たす役割はますます重要になってきています。また、SSD は従来のハードディスク ドライブ (HDD) に比べて非常に優れているため、SSD はすぐに主流のストレージ ソリューションになるでしょう。

SSD の採用は、NAND フラッシュのプロセスの進化に関係しています。他の半導体製品と同様に、NAND フラッシュ チップの単価は、処理ノードを削減することで大幅に削減されます。フラッシュ メモリも、主にトランジスタ スケーリングとマルチレベル セル (MLC) テクノロジによって駆動されます。 1 つのフラッシュ セルに複数のビットを保存できます。残念ながら、NAND フラッシュの物理的特性により、トランジスタのスケールダウンと単一フラッシュ セル内のデータ ビットの増加に伴って信頼性が低下します。こうした副作用をカバーする技術が開発されてきました。

読み取り妨害エラー

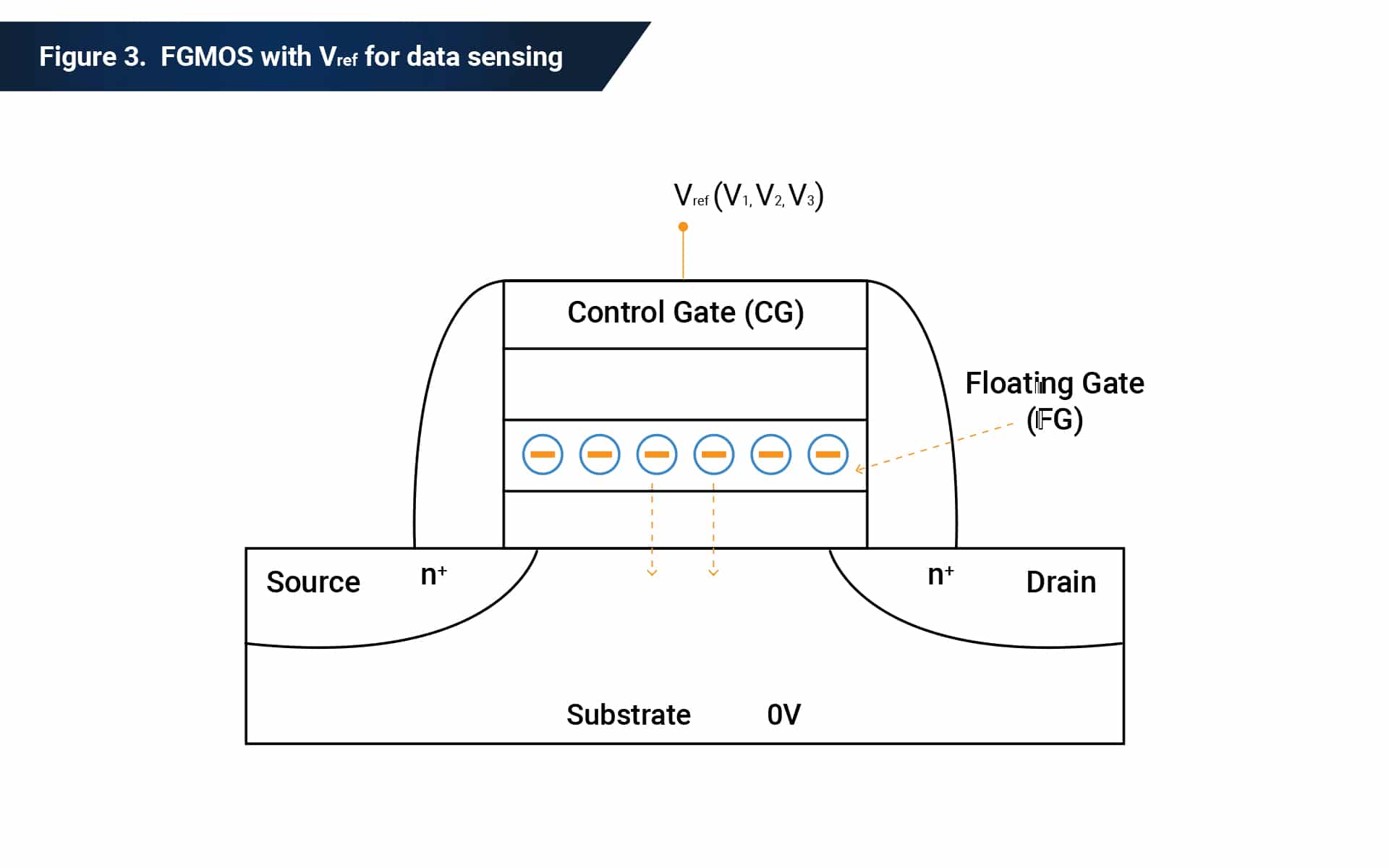

NAND フラッシュ メモリは、数百万個のトランジスタ (MOSFET) で構成されています。各MOSFETはメモリセルとみなすことができます。これらのメモリ セルは、メモリ セルを「スイッチオン」できる最低電圧であるしきい値電圧 (Vth) を通じてデータを保存します。

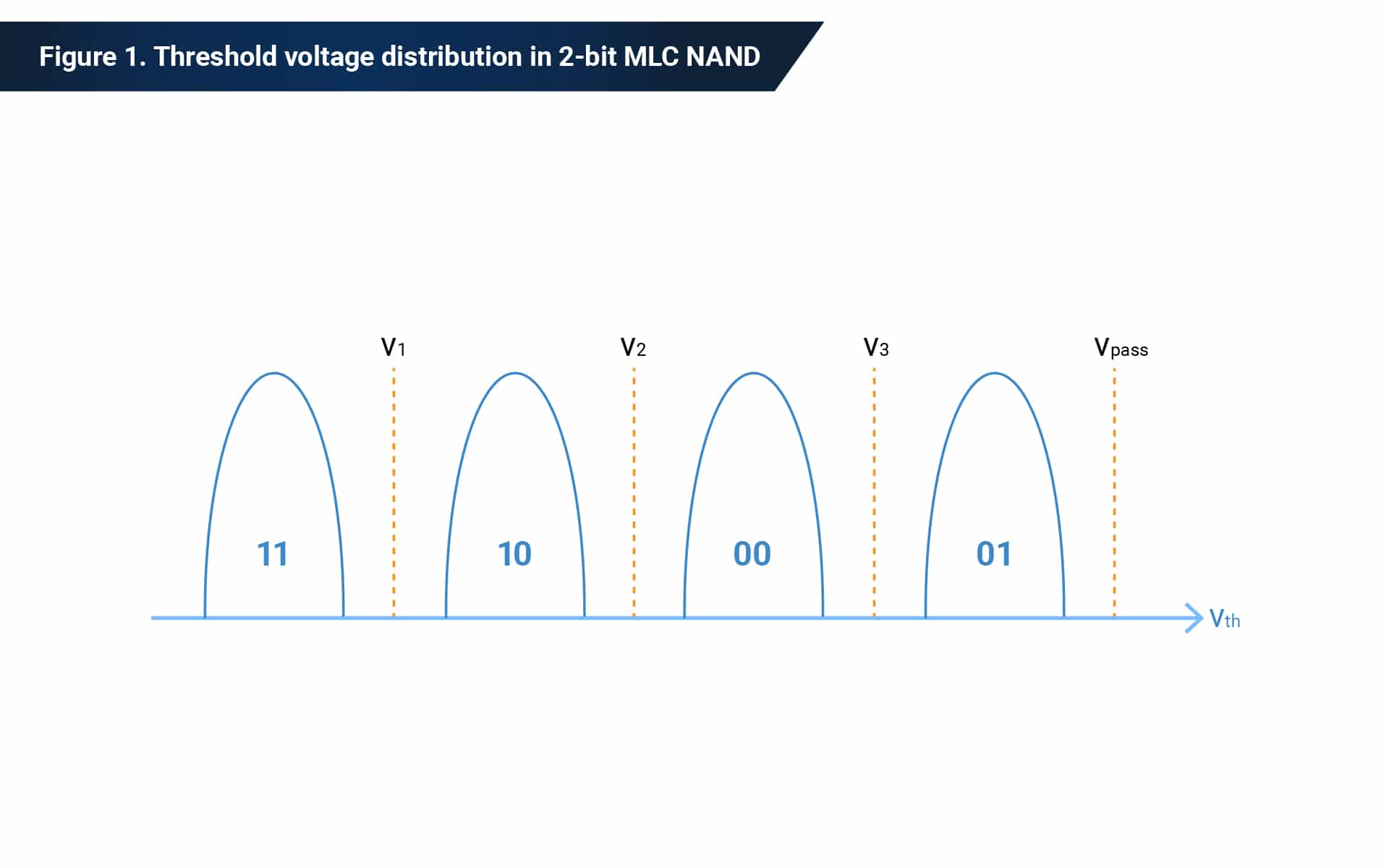

2 ビット MLC NAND を例にとると、2 ビット MLC NAND には 4 つのデータ状態があります。可能な Vth 値の全範囲をこれら 4 つのセグメントに分割する 3 つの基準電圧 (V1、V2、および V3 など)。 Vth が位置する領域はメモリ セルの現在の状態を示し、メモリ セルにどのようなデータが格納されているかを識別するために使用されます。すべてのメモリ セルのしきい値電圧には、パススルー電圧 (Vpass) と呼ばれる上限が存在します。 Vpass は、メモリ セルが「オン」に切り替わることを保証するために必要な電圧です。

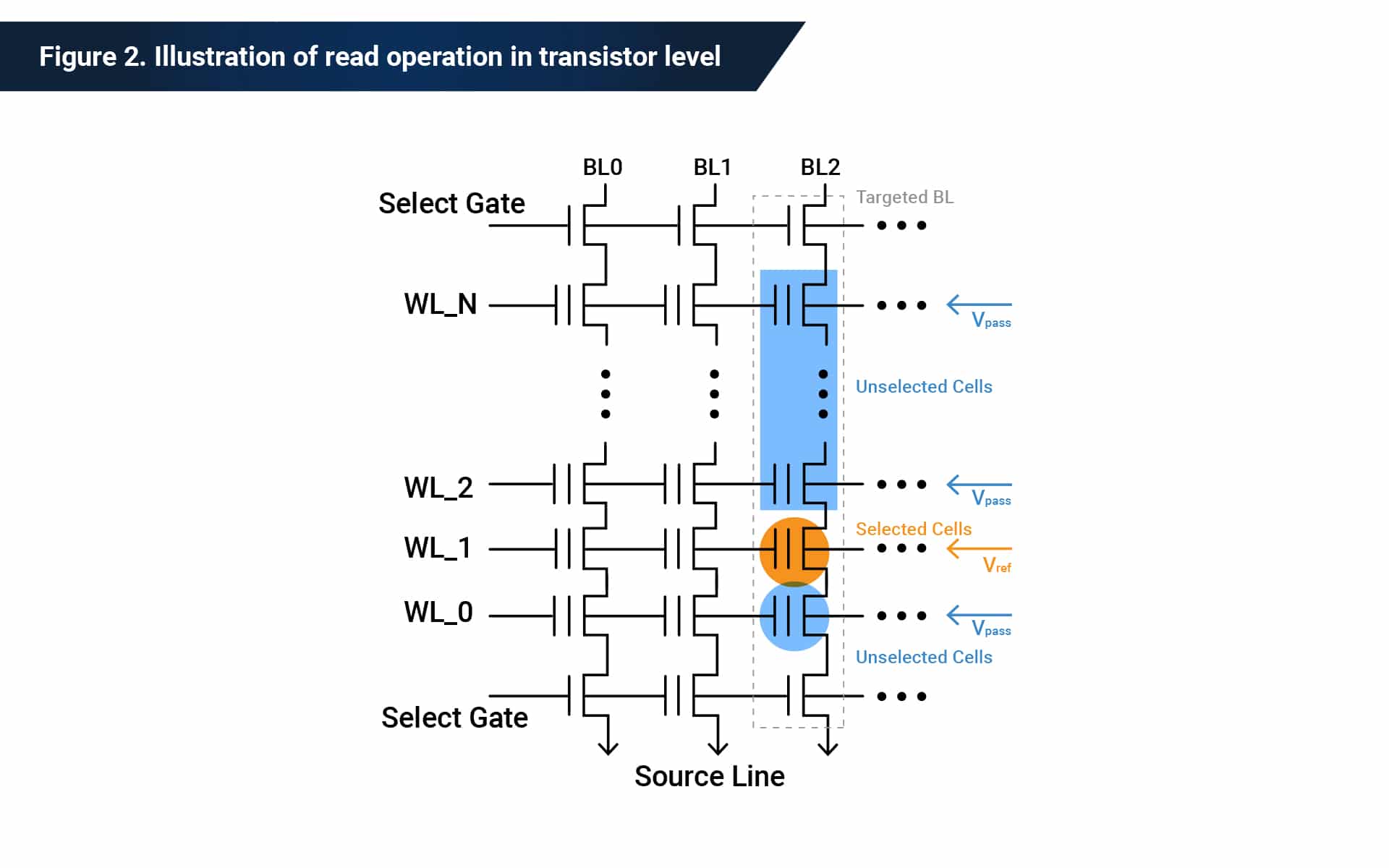

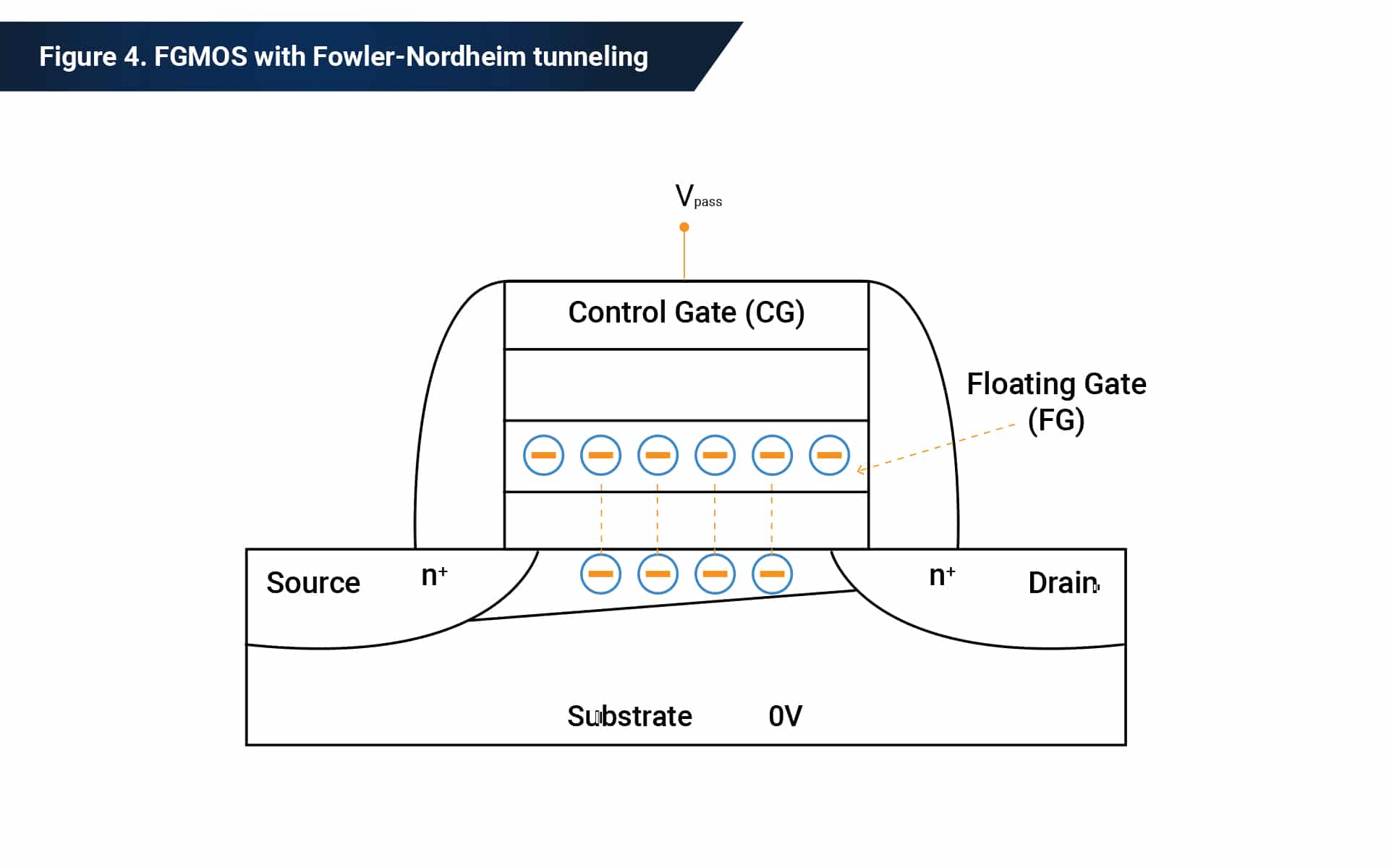

NAND フラッシュ ブロックは、多数のトランジスタのアレイとみなすことができます。 NAND フラッシュ メモリの単純な読み取り操作は、ワード線 (WL) に基準電圧 (Vref) を印加し、この WL 上で選択されたセルのスイッチのオン/オフ ステータスをチェックすることによって実行されます。同じビットライン (BL) 上のメモリ セルは、隣接するセルと接続されます。読み出し対象のセルはそのうちの 1 つだけであるため、選択されていない他のセルは、選択されたセルの状態を確実に検出できるように「ON」状態を維持する必要があります。したがって、同じ BL 上の他の選択されていないセルにはパススルー (Vpass) を適用する必要があります。

このようにして、データ読み出し動作が実行されると、同じブロック内の他の非選択セルの閾値電圧がより高い値にシフトされる。

同じブロック内の選択されていないメモリセルのステータスは、Vpass により影響を受ける可能性があります。選択されていないトランジスタにパススルー電圧が印加されると、ファウラー・ノルドハイム・トンネルと呼ばれるトンネル効果により、フローティング・ゲートに電荷が注入される場合があります。この影響により、トランジスタのしきい値電圧がシフトし、許容できないデータ歪みが発生します。

NANDフラッシュのリテンションエラー

SSD にファイルを書き込みますが、長期間アクセスしないユーザーもいます。これらの古いファイルではいくつかのエラーが検出される可能性があります。この種のエラーは、時間の経過による電荷漏れによって発生します。この現象は、「読み取りディスターブ」の根本原因に似ています。トランジスタ内に存在する電荷によって、メモリセルの閾値電圧レベルが決まります。 NAND フラッシュのスケーリング縮小に伴い、しきい値電圧ウィンドウのサイズもますます小さくなっています。この縮小傾向により、保持ノイズによる閾値電圧レベルのシフトの可能性が高まります。ただし、めったにアクセスされないデータの整合性は依然として保証される必要があります。

Phison の SmartRefresh™ テクノロジー

SSD に保存されたデータを保護するために、Phison は、と呼ばれる独自のテクノロジーを開発しました。 スマートリフレッシュ™ これは、次の 2 つの主要な方法論を使用します。

-

-

- 動的エラービット監視 (DEBM)

- リードリトライ

-

プロセスのスケーリングが縮小すると、NAND フラッシュの本質的な信頼性が問題になります。エラー訂正コード (ECC) 機能は、NAND フラッシュ業界で最も重要なトピックの 1 つになっています。残念ながら、どのような種類の ECC アルゴリズムが使用される場合でも、その訂正能力には理論上の限界があるはずです。 ECC エンジンがトリガーされる前にエラーを軽減または回避できれば、ECC エンジンがユーザー データを回復できない可能性が低くなります。 Dynamic Error Bit Monitoring (DEBM) は、データ破損が発生する前にデータの健全性ステータスをチェックするために使用されるメカニズムです。

Phison の組み込みファームウェアはバックグラウンドで実行され、各ブロックのエラー ビットをチェックします。ファームウェアによって設定された基準内でブロック障害が発生すると(つまり、エラービット数が事前に決定されたしきい値を超えた場合)、ファームウェアはこの障害ブロックに対して特定のアクションを実行して、ユーザーデータの整合性を保証します。

読み取りリトライ

問題のある NAND ブロックから正しいデータを取得するもう 1 つの方法は、異なる電圧レベルを選択してデータ解釈を実行することです。図 1 は、2 ビット MLC NAND フラッシュでの読み取り動作と、保存されたデータを解釈するために使用されるしきい値電圧 (Vth) を示しています。 Phison のファームウェアは、現在のターゲット ブロックが危険であると識別された場合、適切な電圧レベルを使用してデータを分析します。この方法を使用して取得されたデータの信頼性は、Vth の選択によって決まります。 Phison 独自のアルゴリズムは、NAND ブロックの健全性評価に基づいて最適な Vth 値を決定します。

アイドルタイム メディア スキャン (ITMS)

前述の方法論は、それぞれ予防措置と是正措置とみなすことができます。 SmartRefresh™ は、NAND フラッシュの物理的特性による不要なエラーからユーザー データを保護するために、これら 2 つの方法論を組み合わせたテクノロジーです。このメカニズムは 2 つの段階に分かれています。

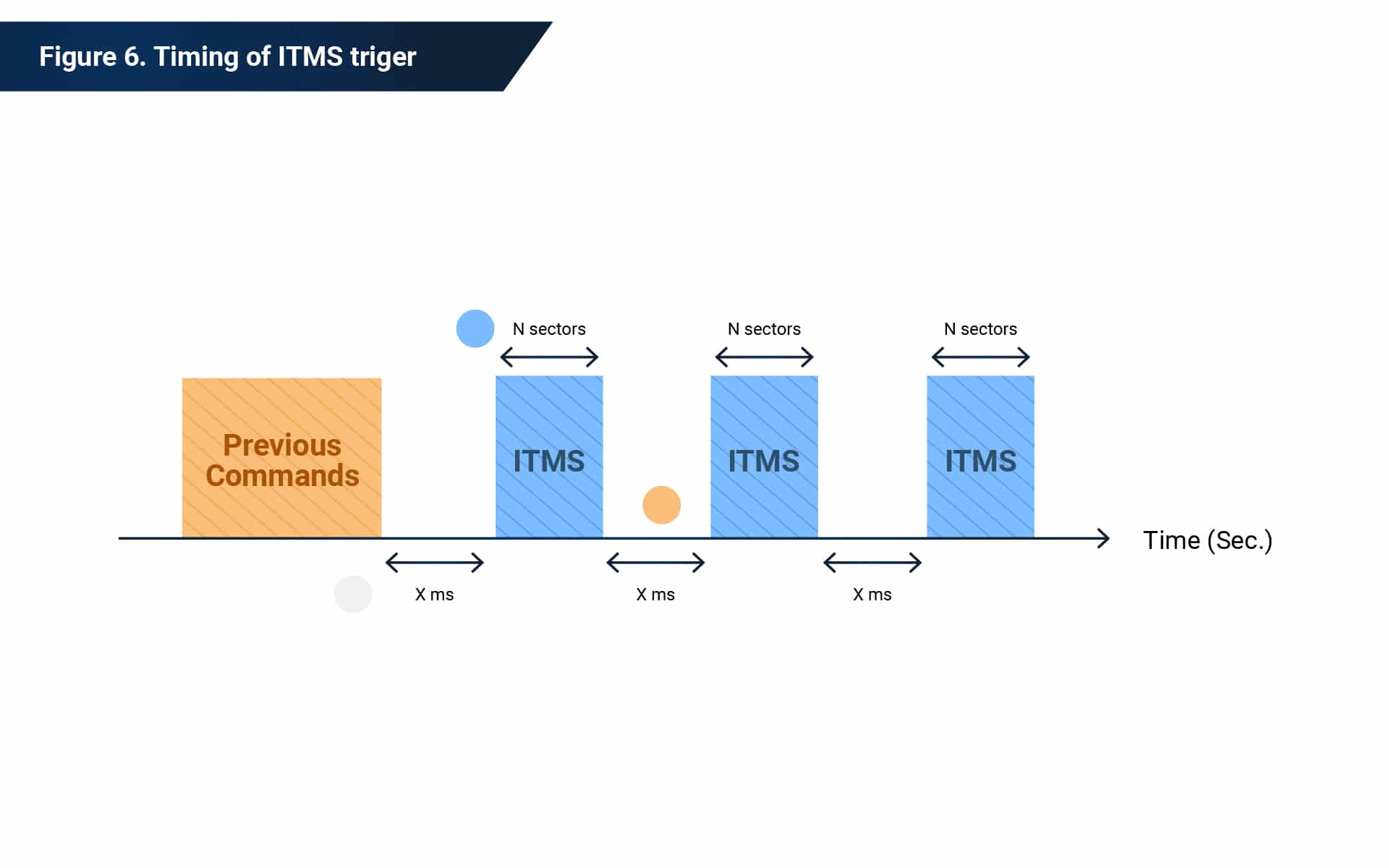

ステージ 1 はアイドルタイム メディア スキャン (ITMS) です。 ITMS は、ホストが IDLE ステータスになるとトリガーされます。 ITMS がアクティブ化されると、ITMS は多くの ITMS サイクルに分割され、各 ITMS サイクル内で多数のセクターがスキャンされます。

ITMS は、DEBM および読み取り再試行操作の実行後に、スキャンされたブロックが正常であるかどうかを検出するために使用されるメカニズムです。いずれかのブロックが異常なブロックとして識別された場合、データの損失を避けるために、異常なブロック内の有効なデータが適切に処理されます。 ITMS はホストが IDLE モードに入っている時間を利用して保存されたデータの健全性状態をチェックするため、ホストがドライブにコマンドを送信するたびに ITMS が中断される可能性があります。この場合、ITMS は停止され、次の ITMS サイクルは、最後の ITMS サイクルでチェックされていないアドレスから起動されます。

ランタイムメディアスキャン (RTMS)

ステージ 2 は、ランタイム メディア スキャン (RTMS) です。 ITMS とは異なり、RTMS を実行するタイミングは IDLE モードに限定されません。 RTMS は、ホストがドライブにコマンドを送信し続けている場合でも、ドライブ全体が特定の期間 (たとえば、毎週 1 回) に完全にスキャンされることを保証します。言い換えれば、RTMS は、長期タスクの処理に使用されるドライブのデータの整合性を保証するように設計されています。

Phison はデータの整合性を保証します

Phison 独自のテクノロジーである SmartRefresh™ は、SSD に保存されているユーザー データを保護するための複数層のアクションなど、データの整合性を確保する信頼性の高いメカニズムを提供します。 Phison の SmartRefresh™ ソリューションを採用することで、NAND フラッシュの固有特性によって引き起こされるエラーを回避できます。