この記事は、Phison の最も重要な製品の 1 つである集積回路 (IC) について詳しく説明するシリーズの 2 番目です。 第一弾 IC とは何か、そしてそれらがどのように分類されるかを調査しました。次に、IC がどのように設計されるかを詳しく説明します。

この集積回路は 1960 年に初めて開発され、含まれていたのはわずか 5 つの抵抗器と 4 つのトランジスタ (電圧または電流に接続すると導通状態になるミニスイッチまたはバルブ) でした。単純そうに思えますよね?

しかし、IC 上のトランジスタやその他のコンポーネントの数が急速に増加するにつれて、状況は急速に変化しました。実際、1965 年にゴードン ムーアという賢人が、今では有名な観察を行ったほどです。同氏は、平均的な IC 内のトランジスタの数が 2 年ごとに 2 倍になるだろうと予測しました。彼は、わずか数年で半導体産業が急成長し、製造プロセスと技術知識が進歩するにつれてトランジスタのサイズが縮小し続けている様子を目の当たりにしました。

「ムーアの法則」は 40 年以上にわたってかなり正確でした。 2000 年代初頭、シリコン トランジスタの技術が物理的な限界を押し上げたため、この推定は鈍化し始めました。トランジスタは物理的に今日可能な限り小さいですが、3D アーキテクチャやその他のテクノロジによってますます複雑になっています。

しかし、それはコンピューターチップの進化が止まったという意味ではありません。半導体や IC コンポーネントを実現する技術は、今も飛躍的に進歩しています。今日のデジタル IC には、チップあたり 1,000 億個以上のトランジスタが簡単に組み込まれています。これだけ多くのトランジスタで構築された IC は信じられないほど複雑です。前回の記事で行ったように、1,000 億個どころか、わずか 10 億個のバルブを備えたパイプ システムを想像することさえ困難です。

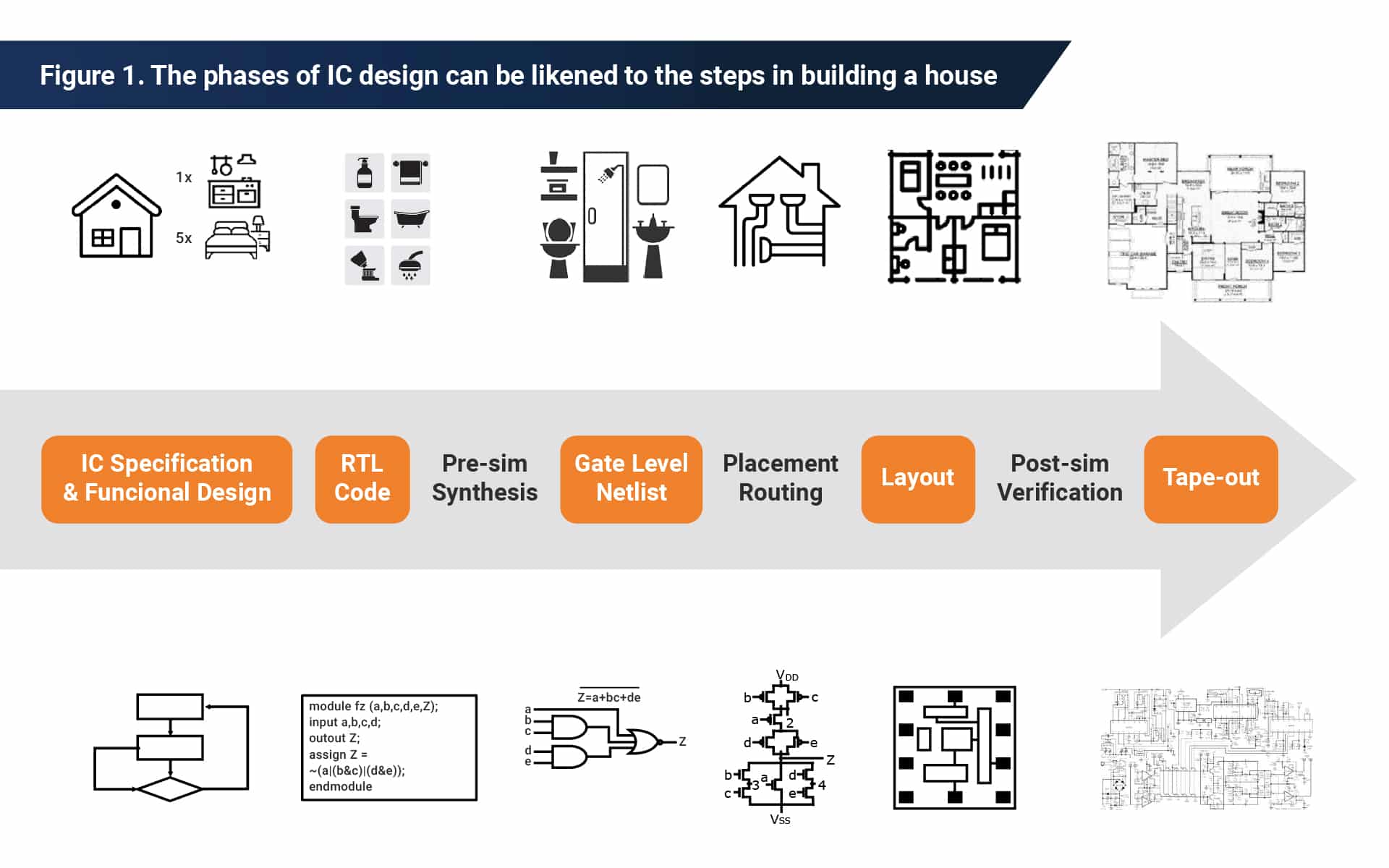

最新の IC の驚くほど複雑さを視覚化する代わりに、これらのチップがどのように設計されているかを段階的に見ていきます。 IC 設計には主に 5 つの段階があります。

-

-

- ICの仕様と機能設計

- RTLコーディング

- ゲートレベルのネットリスト

- レイアウト制作

- テーピングアウト

-

これらの用語は最初は難しそうに思えるかもしれませんが、住宅の設計という単純な例えですべて説明できます (図 1)。

図 1. IC 設計の段階は、家を建てる手順にたとえることができます。

フェーズ 1: IC の仕様と機能設計

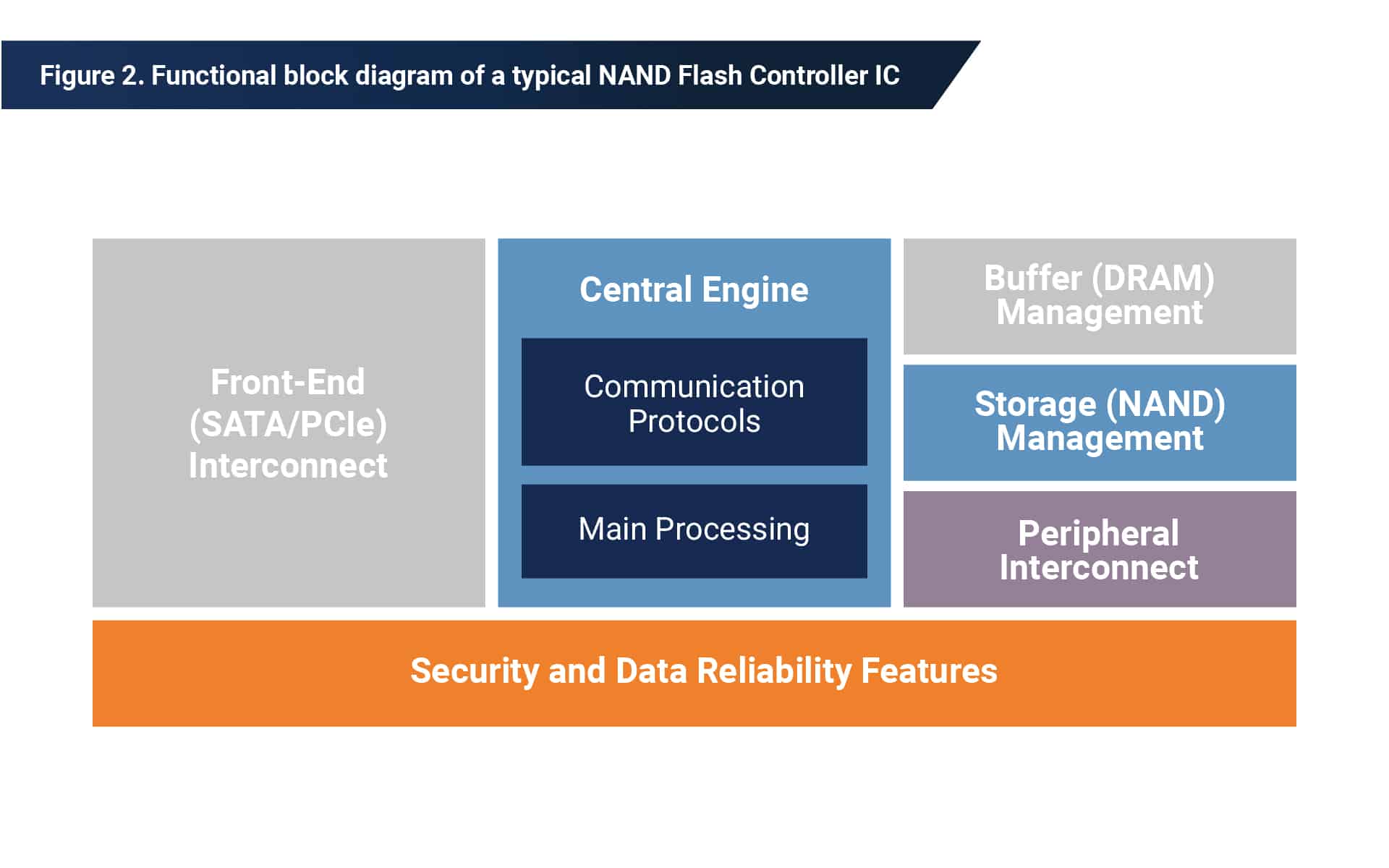

住宅を設計するときは、住宅所有者と建築家が、所有者が家に求めているすべての機能や特徴について事前に話し合うことが重要です。重要なのはプロジェクトの計画であり、IC 設計でも同様に機能します。 IC 設計者と関係者は、ターゲット アプリケーションに必要な機能を実現するための望ましい仕様について話し合う必要があります。たとえば、一般的な NAND フラッシュ コントローラ IC では、主要な機能ブロックには、フロントエンド相互接続、中央エンジン、バッファおよびストレージ メディア管理、周辺機器相互接続、およびセキュリティ機能が含まれます (図 2)。

図 2 に示す機能ブロック図は簡単に見えるかもしれませんが、実際には、ハードウェア設計者が次のフェーズに進む前に、事前に確立して慎重に検討する必要がある詳細な条件とパラメータが豊富にあります。

図 2. 典型的な NAND フラッシュ コントローラー IC の機能ブロック図。

フェーズ 2: RTL コーディング

最初のフェーズはすべて計画に関するものでしたが、このフェーズと次のフェーズは IC 設計プロセスの実行部分とみなされます。機能ブロック図を手に、設計者は、フェーズ 1 でチームが合意した仕様を理論的に実行できるレジスタ転送レベル (RTL) コードのドラフトを作成します。RTL コードは、IC の高レベル表現であり、は、初期段階でシステム全体を最も単純な形で「説明」するために使用されます。

RTL コードは、設計者が基本的に IC の「パズル」を組み立てるさまざまな方法を提示できるようにする低レベルのコーディング言語です。住宅建築の例えを続けると、RTL コーディングのドラフトは基本的に設計コンポーネントの組み合わせのリストであり、住宅計画が床材やキャビネットのスタイルと材料、天井や壁のトリム、配管設備を指定するのと同じです。 RTL コード ドラフトを評価することで、設計チームはシステム内の各ブロックの理論的に最適な構成を推測できるはずです。

フェーズ 3: ゲートレベルのネットリスト作成

RTL コード ドラフトにコミットすると、設計チームは RTL コード結果のゲート レベルのネットリストを実行する準備が整います。これは、設計者が論理ゲートを使用して RTL コードの結果をマッピングすることを意味します。このマップには、最終システムに含まれるすべての遅延とロジックが含まれています。これは、すべての設計要素と設備が設置された家の 3D シミュレーションに似ており、チームはすべてがどのように連携するかを確認できます。

3D グラフィック シミュレーションにより、住宅設計者や関係者は設計を視覚化できますが、ゲート レベルのネットリストは、RTL コード プランに従ってすべての論理構成を明確にするのに役立ちます。ネットリストの最終バージョンが完成すると、設計上の難しい決定のほとんどがこの段階で議論され解決されるため、設計者は全体的な設計の実現可能性について高い信頼レベルを得ることができます。ゲートレベルのネットリストを使用すると、シミュレーションを通じて最終デザインをテストできます。

フェーズ4:レイアウト制作

ゲートレベルのネットリストが完成すると、ハードウェアエンジニアは回路、トランジスタ、その他のコンポーネントの配置をシミュレーションして、IC の詳細なレイアウトを作成できるようになります。必要なすべての機能ブロックとそれぞれのコンポーネントを接続するこの作業は、家庭の配管および照明システムのリンクと配線に似ています。このフェーズの終わりまでに、IC 設計チームは詳細な「マスター設計図」を作成し、実際の構築はほぼ完了します。

フェーズ 5: テープアウト

テープアウトは IC 設計プロセスの最終段階であり、IC が製造に送られる前の最後の段階です。このフェーズには、回路のフォトマスクの作成が含まれます。フォトマスクは、通常は石英またはガラスで作られた固体プレートから始まります。テーピングアウトは、光が差し込む切り抜きスペースまたは穴のある不透明なフィルムでプレートをコーティングするプロセスです (図 3)。 IC 製造業者はフォトマスクを使用してシリコン チップ上にパターンを作成します。これは、IC 設計の「マスター テンプレート」と考えることができます。

図 3. 準備された IC フォトマスク。

この時点で、家づくりの例えは少し崩れ始めます。詳細な設計図に従って住宅を建設する場合でも、多くの課題や予期せぬ問題に直面する可能性があります。 IC 設計では、電子設計自動化 (EDA) ソフトウェアで作成されたシミュレーションはシステム設計の現実的な動作と機能を模倣できるため、不確実性が少なくなります。異常が発生する可能性はありますが、潜在的な問題のほとんどは実際の生産前に予測して解決できるため、時間、労力、コストを大幅に節約できます。

Phison はカスタマイズされた IC 設計の業界リーダーです

Phison の NAND フラッシュ ストレージ ソリューション 独自の IC 設計は、現代の企業の変化するニーズと変動する市場の需要を満たすために進化してきました。実証済みの設計能力とイノベーションにおける豊富な経験により、同社は世界中の次世代アプリケーションの革命を支援する用意ができています。

IC 101 ブログ シリーズの第 3 回目と最終回にご期待ください。この記事では、Phison が IC 開発に採用しているアプローチを探ります。