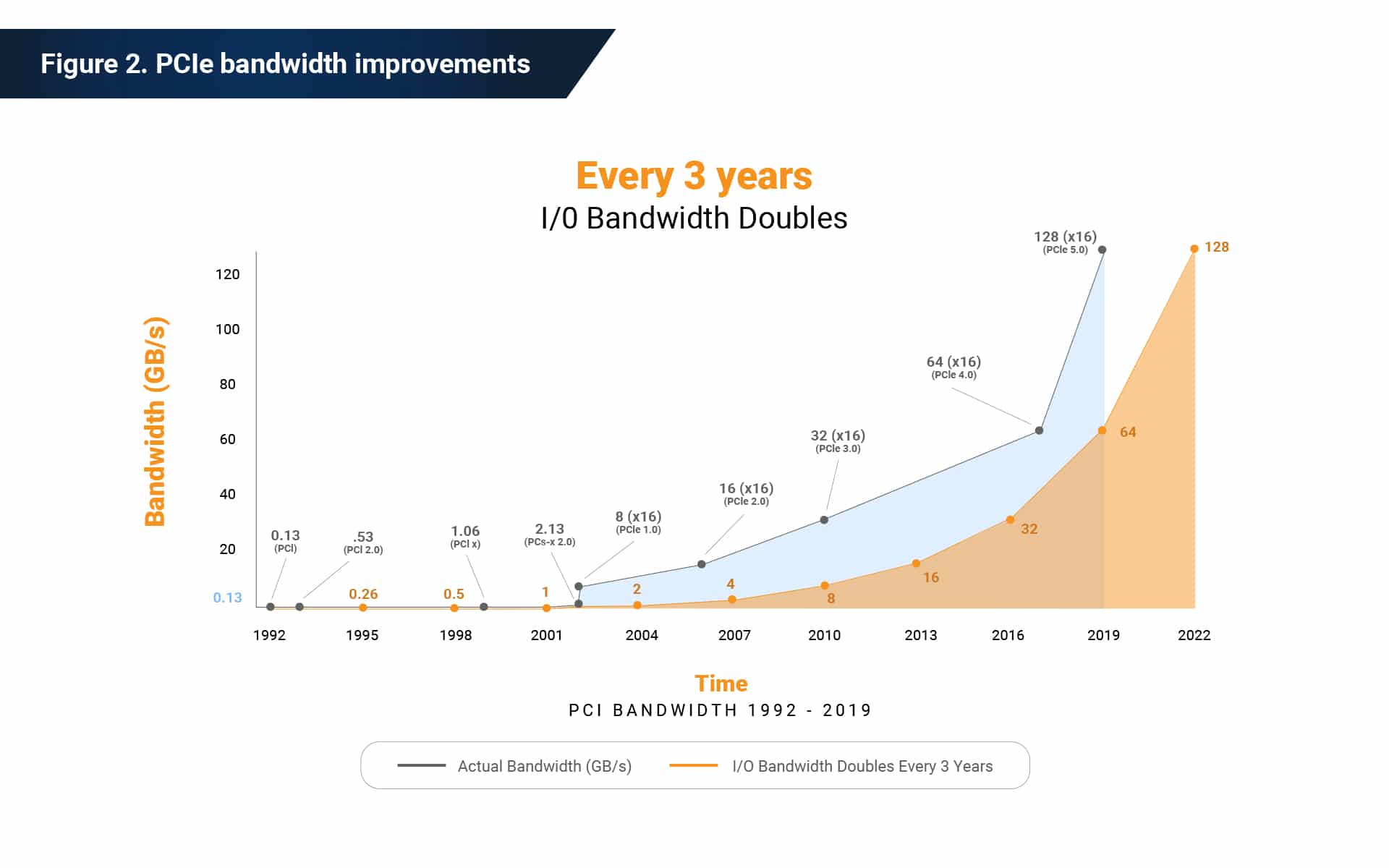

Es ist keine Neuigkeit, dass PCIe seit einem Jahrzehnt die Standardschnittstelle für den Anschluss von Hochgeschwindigkeits-Peripheriehardwarekomponenten auf Computer-Motherboards ist. Während der Standard seit der frühesten Veröffentlichung alle drei bis vier Jahre ein stetiges Upgrade der Übertragungsrate und einen Generationswechsel durchlief, kam PCIe 4.0 im Jahr 2017 auf den Markt und erregte Wellen der Aufmerksamkeit und Begeisterung für technologische Innovationen. Aus Sicht der Datenspeicherung setzte die „Gen 4“-Schnittstelle die seit langem bestehende Bandbreitenobergrenze von etwa 3 GB/s für NVMe Solid State Drives (SSD) frei, die auf dem PCIe 3.0-Standard basieren. Das Schnittstellen-Upgrade ermutigte viele Anbieter, auf ein besseres Design zu drängen, um die Gen-4-Schnittstelle zu berücksichtigen und den Engpass zwischen Hardwarelösungen auf Prozessor- und Speicherebene zu beheben.

Die PCIe-Schnittstelle und Gen 4-Grundlagen

Aus der Perspektive der Peripheriekomponenten ist die PCIe-Schnittstelle das, was wir als „Frontend“ innerhalb des Komponentenmodul-Entwicklungsprozesses betrachten. Das ultimative Ziel eines anständigen „Front-End“-Designs besteht darin, eine robuste Verbindung zwischen dem Hardwaremodul und dem Computersystem über die Zielschnittstelle sicherzustellen.

Sie können den Design- und Entwicklungsprozess in zwei Phasen unterteilen: Hardware und Firmware. Während es leicht ist, die seit Anfang der 2000er Jahre andauernde Innovation in der „Front-End“-Designarbeit mit PCIe in Frage zu stellen, zeichnen sich ausgereifte Designs und Veröffentlichungen der einzelnen Schnittstellenspezifikationen durch die Details der Hardware- und Firmware-Verbesserungsbemühungen aus.

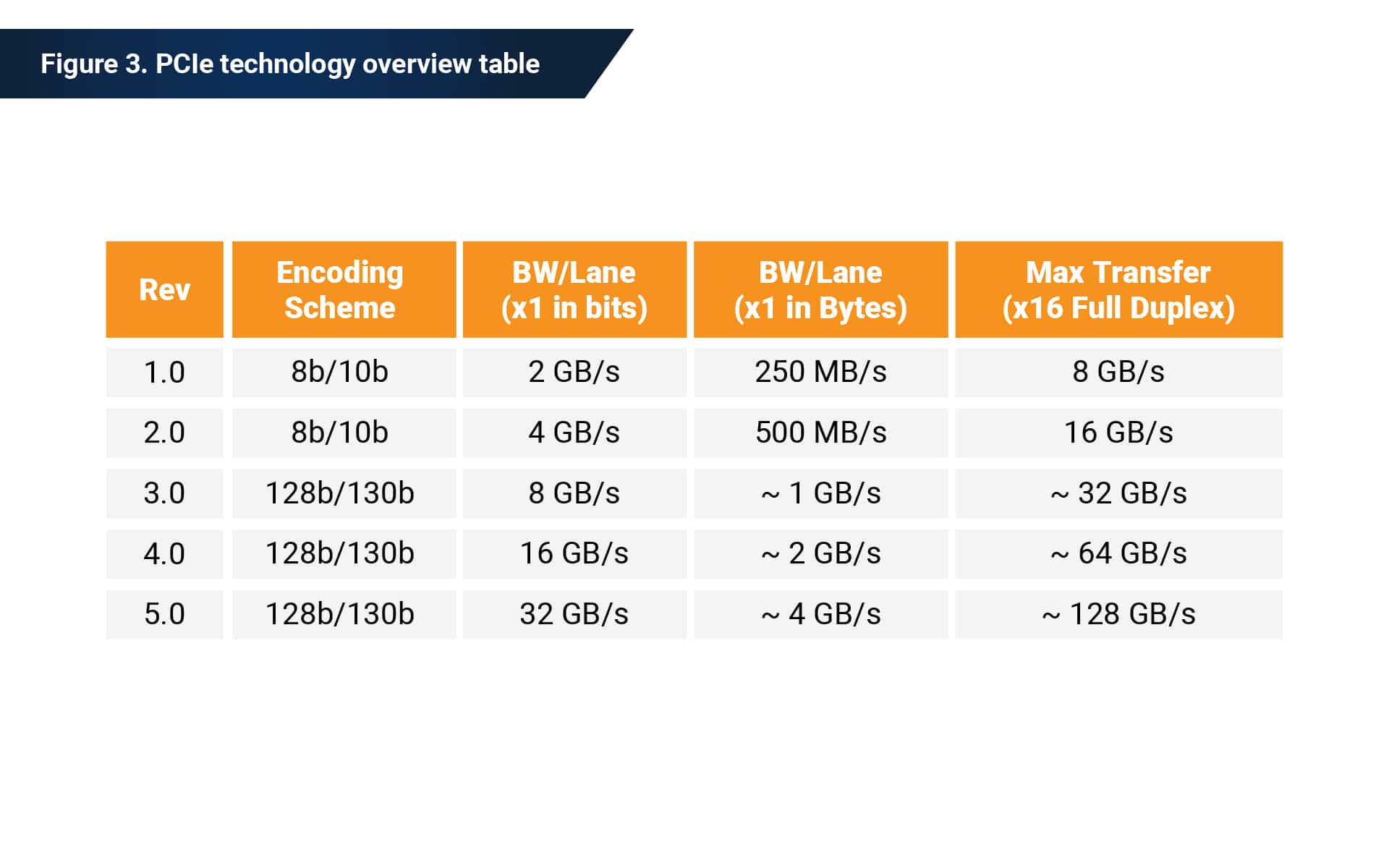

Um das „Front-End“-Design des Mainframes zu verstehen, müssen Sie zunächst die Grundlagen der Hardwarekonfiguration der PCIe-Schnittstelle lesen. Damit eine Speicherkomponente über PCIe mit dem Motherboard verbunden werden kann, verwendet sie einen der Hardwareanschlüsse, die üblicherweise als x1-, x4-, x8- und x16-Steckplatzkonfigurationen bezeichnet werden. Eine Konfiguration der Generation 4×4 weist beispielsweise darauf hin, dass der Steckverbinder den notwendigen Design- und Merkmalsanforderungen der PCIe-Basisspezifikation Revision 4.0 entspricht und gleichzeitig Datensignale über 4 PCIe-„Lanes“ sendet. Jede Spur ist ein bidirektionaler Pfad, der innerhalb einer Sekunde Milliarden elektrischer Signale „aufblitzen“ lässt. Die PCIe-Lanes der 4. Generation führen die Signalisierung mit 16 Giga-Transfers pro Sekunde (GT/s) durch. Während ein „Bit“ an Daten zwischen einem Sendeknoten und einem Empfangsknoten durch die Freisetzung elektrischer Signale mit hoher/niedriger Spannung ausgetauscht werden kann, um logische Einsen und Nullen darzustellen, bedeuten 16 GT/s 16 Milliarden Mal einer solchen Ausführung innerhalb einer Sekunde.

Darüber hinaus funktionieren PCIe-Lanes nach dem „Vollduplex“-Mechanismus. Dh, Datenübertragungen in zwei Richtungen können gleichzeitig erfolgen. Die Übertragungsrate von 16 GT/s bedeutet also theoretisch, dass eine leistungsfähige PCIe-Komponente, die an den Anschlüssen der vierten Generation betrieben wird, innerhalb einer Sekunde 32 Milliarden Datenbits auf nur einer ihrer 32 zur Verfügung stehenden Lanes austauschen kann.

Der Haken an der Berechnung ist jedoch, dass PCIe, wie viele andere Hardwareschnittstellen für die Datenübertragung, seine Daten schützt, indem es Taktinformationen in die Datenströme kodiert. Ab PCIe Gen 3 wird für den Datenschutz das 128-Bit- bis 130-Bit-Codierungsschema verwendet. Dieses Schema erfordert 2 Bits innerhalb jeder 130-Bit-Übertragung für gespeicherte Taktinformationen, um die Identifizierung und Überprüfung der Daten auf der Empfangsseite der Verbindung zu erleichtern. Durch einfache Division und Multiplikation ergibt sich aus 16GT/s eine Übertragungsrate von 15,754 Milliarden Bits pro Sekunde, was allgemein als 15,754 Gbit/s sinnvolle Datenbitübertragung bezeichnet wird (unter Vernachlässigung der Taktinformationsbits).

Unter Einbeziehung der Taktinformationsbits ergibt sich eine physikalische Bandbreite von 16 Gbit/s. Es kann dann mit einer Rate von 8 Bits pro 1 „Byte“ in 4 Gigabyte pro Sekunde (GB/s) umgewandelt werden, was in der Welt der Bandbreite auf Modulebene und im gesamten Bereich die am häufigsten verwendete Standard-Datengrößeneinheit ist. Darüber hinaus ist die Gesamtbandbreite gemäß PCIe Gen 4 mit einer Skalierbarkeit von bis zu 64 GB/s ausgestattet, was dem Doppelten des maximalen Durchsatzes gegenüber der vorherigen Generation von PCIe 3.0 entspricht.

Um die Bedeutung dieses Fortschritts ins rechte Licht zu rücken: Die Datengröße eines eingegebenen Zeichens auf einem Computer beträgt 1 Byte (oder 8 Bit) und eine PCIe Gen 4×16-Schnittstelle kann ein Paar Dateien mit 32 Milliarden Zeichen innerhalb einer austauschen zweite. Ein 1080p-HD-Film hat in der Regel eine Dateigröße von ca. 10 GB, und mit einer Bandbreite von 64 GB/s können Sie unter idealen Datenverarbeitungsbedingungen drei davon aus Ihrem Speicher auf einen Computer kopieren und drei davon in einer Sekunde herausbewegen. Dennoch bleibt der PCIe-Flash-Speicherengpass weit unter der vollen 16-Lane-Fähigkeit. Mainstream-NVMe-SSDs im Jahr 2021 verwenden hauptsächlich die x4-Konfiguration, wodurch die physische Leistung bei 8 GB/s liegt.

Übersicht über die PCIe-Spezifikationen

Die derzeit am weitesten verbreitete Speicherschnittstelle hat weitaus mehr zu bieten als nur Leistungsindikatoren. Die im PCIe-Protokoll geregelte elektrische Signalisierung regelt detaillierte Funktionen und Fähigkeiten, einschließlich, aber nicht beschränkt auf:

-

-

- Schnittstelleninitialisierung,

- Wartungsstatusverfolgung,

- Verbindungsenergiemanagement,

- Spurzuordnungsverhandlung,

- Datenkodierung/-dekodierung auf Schnittstellenebene,

- und auch integriertes Clock-Tuning

-

Über die physikalische Schicht hinaus gibt es zwei weitere PCIe-Spezifikationen, die für den ordnungsgemäßen SSD-Frontend-Betrieb genauso wichtig, wenn nicht sogar noch wichtiger, sind; die „Datenverbindungsschicht“ (oder einfach „Verbindungsschicht“) und die „Transaktionsschicht“. Wie das Wort „physisch“ schon andeutet, hängen viele der Fähigkeiten innerhalb dieser Schicht stark vom Hardware-Design des Speichermoduls ab. Andererseits hilft das Verständnis der beiden oben genannten Ebenen dabei, etwas Licht auf die Front-End-bezogenen Firmware-Module zu werfen.

Unmittelbar über der physikalischen Schicht befindet sich die Datenverbindungsschicht, die für die Zusammenarbeit mit der physikalischen Schicht verantwortlich ist, um einen zuverlässigen Informationsaustausch zwischen Systemen sicherzustellen. Beachten Sie die Formulierung „Information“ statt „Daten“, da sich der technische Schwerpunkt innerhalb dieser Schicht von der physischen Sichtweise bei der Datensignalisierung auf die logische und eher Firmware-Sicht der Verbindung und Verknüpfung der physischen Geräte verlagert hat. Die Zusammenarbeit mit der physikalischen Schicht umfasst die Übertragung des Energiezustands zur und von der physikalischen Schicht, den Datenschutz auf Verbindungsebene sowie Fehlerwiederholungs-/Protokollierungsdienste.

Die letzte PCIe-Entwurfsschicht ist die Transaktionsschicht, die mit der Bewegung von Datenpaketen arbeitet, die als Transaction Layer Packages (TLP) bekannt sind. Mit der Generierung und dem Empfang von TLPs tauscht die Transaktionsschicht Flusskontrollinformationen mit der anderen Seite des PCIe-Links aus. Genauer gesagt speichert es Verbindungskonfigurationsinformationen, die von den System-/Speicherprozessoren generiert werden, und Verbindungsfunktionen, die von der Hardware der physikalischen Schicht generiert werden. Darüber hinaus ist die Handhabung von TLP auch die primäre Grundlage für software- und hardwareinitiierte Energieverwaltungsmechanismen. Das Verständnis der beiden oben genannten Ebenen hilft dabei, etwas Licht auf die Front-End-bezogenen Firmware-Module zu werfen.

Alles in allem trägt die Transaktionsschicht schwere Aufgaben der Verbindungsverarbeitung und des Energiemanagements, die synchronisierte Hardware- und Firmware-Aufwände erfordern.

Die Marktübersicht für PCIe Gen 4

Mit der kontinuierlichen Weiterentwicklung des geschichteten Designmodells für die PCIe-Architektur hat die Spezifikation eine erweiterbare und skalierbare Datenübertragungsschnittstelle formuliert, die sich über die aktuellen Maßnahmen hinaus weiterentwickeln wird. Selbst mit dem bevorstehenden technologischen Fortschritt in Richtung der nächsten PCIe-Generationen, da Speichercontrollerlösungen der 5. Generation auf den Markt gekommen sind (zusammen mit den aufkommenden Diskussionen zur 6. Generation), ist es die Marktakzeptanz, die Tag für Tag unmittelbar zu den Speichereinnahmen auf Branchenebene beiträgt.

Obwohl es kein Geheimnis ist, dass die PCI-SIG-Arbeitsgruppe bereits weit über Gen 4 hinausblickt, befindet sich der Mainstream-Solid-State-Storage-Markt immer noch in der Hochphase der Einführung von Gen 4. Beginnend mit dem Verbrauchermarkt sicherte sich AMD seine Position als erster Systemhersteller, der auf der Computex 2019 seine PCIe-Gen-4-Plattform mit dem X570-Chipsatz vorstellte. Im selben Jahr übernahm Phison die Führung bei der Einführung des weltweit ersten PCIe-Gen-4-Flash-Controllers Unsere E16-Lösung, die die Leistung der 3. Generation in den Hintergrund rückt und Daten mit einem Durchsatz von 5 GB/s überträgt.

Andererseits kündigte Intel die Einführung seiner neuen Plattform mit dem Codenamen Rocket Lake an, die möglicherweise zeitlich später erfolgte, nicht jedoch im Hinblick auf die Leistung der unterstützten PCIe-Peripheriegeräte. Den offiziellen Benchmark-Ergebnissen von Intel zufolge hat die PCIe-Gen-4-SSD in Kombination mit der Rocket-Lake-Plattform die Gen-4-Leistung im Jahr 2020 auf die nächste Stufe gehoben.

Passend zu diesem Durchbruch brachte Phison später im selben Jahr seine aktualisierte E18 PCIe Gen 4-Controllerlösung auf den Markt, um den Gen 4-Rekord auf den Höhepunkt zu bringen. Es war die weltweit erste Controller-Lösung, die einen Durchsatz von über 7 GB/s erreichte. Durch die weiterhin starke Partnerschaft mit den beiden Weltklasse-CPU-/Plattform-Anbietern wird Phison weiterhin bereit sein, den PCIe-Verbrauchermarkt anzuführen und seine Partner und Kunden mit hochmodernen Speicherlösungen für die Desktop-, Laptop-, Gaming- und Workstation-Märkte zu unterstützen.

Auf der anderen Seite der Branche hat das anhaltende Wachstum bei Hochleistungs-Computing-Anwendungen sowohl für Unternehmen als auch für Rechenzentren wie maschinelles Lernen, künstliche Intelligenz (KI) und Deep Learning den Servermarkt dazu angeregt, nach größerer Rechenleistung zu greifen . Der Bedarf an Hochleistungsspeicher mit zuverlässiger Konsistenz und Zuverlässigkeit zur Gewährleistung einer stabilen Servicequalität ist die perfekte Gelegenheit für den Übergang zu PCIe Gen 4-Speicherlösungen, um die Bandbreitenanforderungen zu erfüllen. Zusätzlich zu den Durchsatzanforderungen folgen die meisten Anwendungsfälle für Unternehmen und Rechenzentren strengen Kriterien, die eine stabile Leistung mit einer geringen Toleranz für Latenz außerhalb der Spezifikation unter Belastung regeln.

Um auf diese Nachfrage zu reagieren, sind starke Hardware- und Firmware-Designfähigkeiten zur Feinabstimmung für Kundenanwendungen erforderlich, damit der PCIe Gen 4-Übergang nahtlos erfolgen kann. Als Vorreiter auf dem Gen-4-Lösungsmarkt hat sich das Ingenieurteam von Phison sorgfältig darauf vorbereitet, in den Übergang zum Cloud- und Hochleistungs-Computing-Markt einzutauchen und Speicherdienste auf die nächste Stufe zu bringen, indem es den Front-End-Engpass beseitigt.

Phison hat nachweislich Erfolge bei Gen-4-Anwendungen und der schnellen und pünktlichen Lieferung von Gen-4-SSD-Lösungen für den Verbrauchermarkt erzielt. Wir widmen der Unterstützung des Gen 4- und Gen 5-Übergangs in den Unternehmensmarktanwendungen die gleiche Aufmerksamkeit und die gleichen technischen Ressourcen.