2013 年、Apple は PCIe SSD を搭載した最初の MacBook Pro を発売し、PCIe ベースの SSD の領域を消費者向けアプリケーションに正式に拡大しました。ただし、PCIe ベースの SSD は、その高い帯域幅と拡張性により、それよりずっと前からサーバーやデータセンターですでに使用されていました。

最新の 3D NAND フラッシュ テクノロジーにより、PCIe SSD が安価になり、小売店や消費者向けアプリケーションでの採用が増えています。しかし、消費者や企業が SSD に切り替える理由は、価格とパフォーマンスだけではありません。データ保護も重要な要素です。

SSDのエンドツーエンドのデータ保護

3D TLC や QLC などの高度なフラッシュ プロセス テクノロジを使用すると、ドライブは非常に魅力的な小売価格でテラバイトのデータを簡単に保存できます。ただし、保存されるデータ量が 2 倍、さらには 3 倍になるため、PCIe SSD コントローラーがデータを保護する方法もパフォーマンスを向上させる上で同様に重要です。

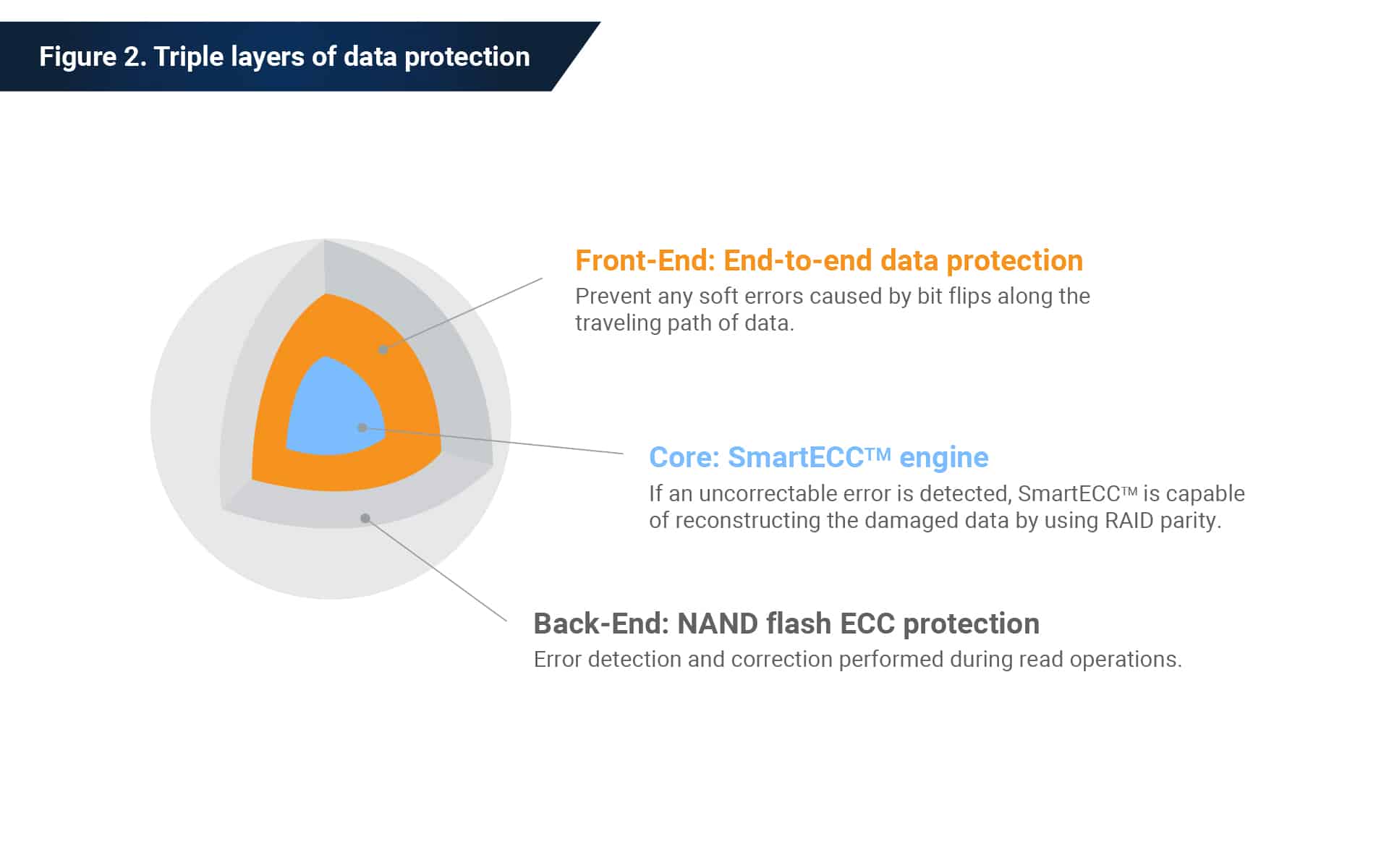

のために Phison PCIe SSD、データ保護は 3 つのレベルで構成されます。

-

-

- フロントエンド: エンドツーエンドのデータ保護 (ETEDP) は、読み取り操作と書き込み操作の両方でデータを保護します。

- 芯: SmartECCTM エンジンは、RAID メカニズムを使用して誤ったデータを回復します。

- バックエンド: NAND フラッシュ ECC 保護は、読み取り操作中にエラーの検出と訂正を実行します。

-

ETEDP とも呼ばれるエンドツーエンドのデータ保護は、データ転送時にソフト エラーを検出するように設計されています。 NAND フラッシュへのデータの読み取りまたは書き込みを行う場合、データ転送中にデータが一時的に保存される複数のステップがあります。したがって、フラッシュ ストレージには、シングル イベント エラーを引き起こす可能性のあるビット フリップやノイズが発生する可能性があります。コントローラーは、これらのエラーがいつ発生するかを認識し、可能であれば対処する必要があります。

書き込み操作の保護

データが NAND に書き込まれるとき、データはホスト IP (PCIe および NVMe IP) からデータ バッファー (DRAM および SRAM)、フラッシュ IP、そして最後に NAND フラッシュに移動します。

ホストが書き込みコマンドを発行すると、データはまずホスト IP に移動されます。データは CRC に対してチェックされ、一致する場合は、E2E パリティ (データの論理ブロック アドレス (LBA) に基づいて生成される) がデータ自体に追加されます。データがデータ バッファーに移動すると、そのデータは SECDED (単一エラー訂正、二重エラー検出) によって保護され、内部の ECC エンジンが誤ったデータを回復できます。 Flash IP の場合、データがチェックされ、さらに CRC およびLDPC コードが追加されます。最後に、パリティ付きのすべてのデータが一度に NAND フラッシュに書き込まれます。

読み取り動作保護

ホストによってデータが読み取られると、データは NAND からフラッシュ IP、データ バッファ、最後にホスト IP に移動します。

修正エンジンの設計によって、どれだけのエラーを回復できるかが決まります。読み取り操作中、データは最初にフラッシュ IP 内のLDPC と CRC をチェックされます。データが正しい場合、ECC パリティが解除され、データはそれに応じて他の IP に移動します。書き込み操作と同様に、データはデータ バッファーとホスト IP でその正確性がチェックされます。データが正しい場合、E2E パリティが切り離され、データがホストに送信されます。

Phison はデータを安全に保ちます

3D NAND プロセス テクノロジーにより、顧客は SSD に高いパフォーマンスと容量、さらに優れた耐久性とデータ信頼性を求めています。データ保護に関しては、目的を達成するためのさまざまな方法がありますが、エンドツーエンドのデータ保護は一般的に PCIe コントローラー内で実行されます。エンドツーエンドのデータ保護の目的は、パリティを生成し、読み取りおよび書き込み操作のデータ転送中にソフト エラーを検出するためにデータにパリティを追加することです。